Fターム[5F033VV11]の内容

半導体集積回路装置の内部配線 (234,551) | 配線の用途 (10,506) | ヒューズ、アンチヒューズ (176)

Fターム[5F033VV11]に分類される特許

1 - 20 / 176

半導体回路装置およびその製造方法

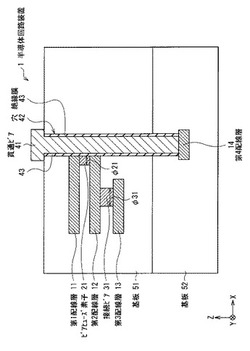

【課題】ビアヒューズ素子の径を小さくし、ビアヒューズ素子を低電流で溶断することが可能な半導体回路装置およびその製造方法を提供する。

【解決手段】一方向に配置された複数の配線層と、前記複数の配線層のうちの少なくとも2つの前記配線層の間に設けられたビアヒューズ素子と、前記複数の配線層の配置方向に直交する平面内において前記ビアヒューズ素子に隣接する穴と、前記穴内に設けられた貫通ビアとを備えた半導体回路装置。

(もっと読む)

半導体装置

【課題】多層配線プロセスでSOGエッチバックにて平坦化を行なうプロセスにて、ヒューズ開口部に起因する水分の浸入における長期信頼性の劣化を防止する半導体装置の製造方法を提供する。

【解決手段】ヒューズ開口部からの水分侵入を防ぐためのメタル1層目のガードリングの下部まで多結晶シリコンが伸びているヒューズ形状にする。これによりヒューズの電極をとるためのメタル配線とガードリングのメタル配線の高さがそろい、SOG層がIC内部に到達することを防ぐことが可能となる。

(もっと読む)

半導体装置

【課題】ヒューズ開口部からの水分侵入による電特異常及び配線腐食を防止する半導体装置を提供する。

【解決手段】ヒューズ配線4の下方には凸領域となるTEOS膜14の下敷きがあり、ヒューズ配線4はTEOS膜14を跨ぐように設けられ、ヒューズ配線4の上方にはTEOS膜14よりも小さい領域のヒューズ開口部13が設けられる。さらに、TEOS膜14の無い領域にてヒューズ配線14の両端に設けられたヒューズ端子15には第1金属配線7が電気的に接続されている。

(もっと読む)

半導体装置

【課題】抵抗体とヒューズ素子が並列に接続された半導体装置において、ヒューズ素子切断時に抵抗体への損傷がなく、抵抗体とヒューズ素子とを積層すること。

【解決手段】半導体基板上に第1の絶縁膜を介して形成された抵抗体を設け、抵抗体の上に第2の絶縁膜を介して形成された遮光層を設け、遮光層の上に第3の絶縁膜を介して形成されたヒューズ素子のヒューズ部を有し、抵抗体と遮光層とヒューズ部を重畳した半導体装置とする。

(もっと読む)

ヒューズ、半導体装置、半導体装置の製造方法

【課題】高電圧が不要で安定した状態を得ること。

【解決手段】半導体装置10に形成されたヒューズ素子11は、概略的に、拡散領域22と、拡散領域22と一部重なるように拡散領域22より上方に形成された導電体25を含む。半導体装置10の半導体基板21には、拡散領域22が形成されている。半導体基板21には素子分離領域23が形成されている。拡散領域22を含む半導体基板21上には絶縁膜24が形成されている。絶縁膜24上には、導電体25が形成されている。導電体25上には、カバー膜26が形成されている。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。カバー膜26は、絶縁膜24より高い引っ張り応力を持つ。

(もっと読む)

半導体装置および基板

【課題】アライメントマークを用いて形成される半導体装置であり、ダイシングおよびクラックに起因する半導体チップの品質低下を抑制し、半導体チップの微細化を容易にすることが可能な構成を有する半導体装置および基板を提供する。

【解決手段】主表面を有する半導体基板と、半導体基板の一方の主表面上に形成された多層構造回路ICと、多層構造回路ICのうち最上層と同一の層に形成される、平面視において多層構造回路を取り囲むように配置される保護壁GRと、最上層と同一の層に形成される位置合わせマークM2Bとを備える。上記位置合わせマークM2Bは少なくとも一部において保護壁GRと接するように形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】トリミングヒューズの上の絶縁膜が、トリミングヒューズの機能を高めるために適正な状態を維持することが可能な半導体装置を提供する。

【解決手段】表面を有する絶縁膜III上のヒューズ配線F1と、ヒューズ配線F1上の層間絶縁層II1,II2,PIと、層間絶縁層II1,II2,PIの内部に位置する、ヒューズ配線F1と平面視において重ならない領域に形成された電極部PDとを備える。上記ヒューズ配線F1の真上のうち少なくとも一部の第1の領域において、層間絶縁層II1,II2,PIの厚みが、第1の領域以外の第2の領域における層間絶縁層II1,II2,PIの厚みより薄くなるようにトリミング開口部LTCが形成される。トリミング開口部LTCの内側において側壁および底面の少なくとも一部を覆うアルミニウム薄膜部SALを備える。アルミニウム薄膜部SALは、側壁の少なくとも一部から、底面より上側において上記表面に沿う方向に連なる。

(もっと読む)

半導体ダイ上にフィーチャをめっきするためのヒューズバス

【課題】半導体ダイ上に相互接続部又はボンドパッドなどのフィーチャ構造を電気めっきする方法を提供する。

【解決手段】方法は半導体基板の上方に複数のヒューズ(208)を形成する工程と、半導体基板の上方の複数の相互接続層(400〜408)と、該複数の相互接続層の上面の複数の相互接続パッド(502)とを形成する工程と、を含む。シールリング(202)が、半導体基板(302)と、前記複数の相互接続パッド(502)と、前記複数のヒューズ(208,320)とに形成された能動回路を包囲する。各ヒューズ(208,320)は、対応する相互接続パッド(502)とシールリング(202)とに電気的に接続される。各ヒューズ(208)が導通状態にあるとき、該ヒューズは対応する相互接続パッド(502)をシールリング(202)に電気的に接続する。

(もっと読む)

半導体装置

【課題】占有面積の小さな直線状の電気ヒューズを有する半導体装置を提供する。

【解決手段】複数の突出部10fは、電気ヒューズ部10aの中央位置からずれた位置、より具体的には、ビア10dに近くかつビア10eから遠い位置に設けられている。また、複数の突出部20fは、電気ヒューズ部20aの中央位置からずれた位置、より具体的には、ビア20dから遠くかつビア20eに近い位置に設けられている。つまり、突出部10fおよび突出部20fは、ジグザグ状に配置されている。

(もっと読む)

電気ヒューズ及びその製造方法

【課題】発熱体である抵抗から熱容量の大きいアノード領域への放熱を阻止し、ジュール熱を効率的に抵抗で消費するようにして、電気ヒューズの切断電力の低減化を図る。

【解決手段】絶縁膜5上にポリシリコン層6を形成し、該ポリシリコン層6上の一部に絶縁膜マスクを形成する。次に、該絶縁膜マスク層で被覆された以外のポリシリコン層6上にシリサイド層7を形成する。次にフォトエッチング工程を経てシリサイド層7、ポリシリコン層6をエッチングし、アノード領域1、カソード領域2及びアノード領域1とカソード領域2を接続するリンク領域3からなる電気ヒューズを形成する。電気ヒューズは、アノード領域1とリンク領域3の境界を挟んでリンク領域3方向からアノード領域1の一部に延在する非シリサイド領域を具備する。リンク領域3の非シリサイド領域は高抵抗領域11を構成し、アノード領域1の非シリサイド領域は熱伝導阻止層1bを構成する。

(もっと読む)

半導体装置

【課題】半導体装置において、高電圧の配線層とその下方を横切るように配置された抵抗層との間の絶縁膜の耐圧を確保し、この配線層と抵抗層との間で破壊が起きるのを抑制することを目的とする。

【解決手段】第1半導体領域10に接続され第2半導体領域11上を通過するように第3配線層22が配置されている。第3配線層22と第2半導体領域11との間に配置される絶縁膜14内には、一端が第3配線層22に接続されると共に、他端が第1半導体領域11よりも電位の低い制御端子12に接続され、且つ第3配線層22とSOI層2との間において第3配線層22を少なくとも1回以上横切る構成で抵抗層25が配置されている。この抵抗層25は、第3配線層22を横切る部位の上面が他の部位よりも下方位置となるように段差状に形成されている。

(もっと読む)

半導体装置

【課題】銅ヒューズに起因する故障または特性悪化を抑制または防止できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1と、銅ヒューズ4と、半導体基板1と銅ヒューズ4との間に配置された銅膜からなるシール膜7,8と、銅ヒューズ4よりも上の層に形成された銅以外の金属材料膜からなり、銅ヒューズ4の両端にそれぞれに接続された最上層配線501,502と、シール膜7,8に結合され、銅ヒューズ4の周囲を取り囲む筒状に形成された銅シールリング6とを含む。

(もっと読む)

半導体装置

【課題】安定した特性のヒューズ素子を有する半導体装置を提供する。

【解決手段】半導体装置100は、基板10と、基板10の上方に形成され、空洞部20を画成する被覆構造体30と、空洞部20に収容されたヒューズ素子40a,40b,40cと、を含み、被覆構造体30は、導電層を有し、ヒューズ素子40a,40b,40cの材質は、導電層の材質と同じである。

(もっと読む)

半導体装置の製造方法

【課題】ヒューズ(FUSE)を備えた半導体装置の信頼性を向上する。

【解決手段】半導体基板11の主面上に形成にされた多層配線を構成する層M1〜M6のうちの層M4に設けられた電気溶断型の救済用のヒューズ4aおよび試験用のヒューズ4bと、ヒューズ4aの近傍であって層M2および層M6に設けられた一対の導電板10aと、ヒューズ4bの近傍であって層M3および層M5に設けられた一対の導電板10bとから構成する。ヒューズ4bと導電板10bとの間が、ヒューズ4aと導電板10aとの間より近いものとする。

(もっと読む)

半導体装置

【課題】周辺部を損傷させずに、電流を供給することによって切断され得る電気ヒューズ構造を有する半導体装置を提供する。

【解決手段】電気ヒューズ10は、電子回路とその電子回路のスペアとしての冗長回路との間に電気的に接続され、それらの回路が樹脂封止された後に、外部から電流が供給されることによって切断され得るものである。電気ヒューズ10は、ファイン層中に設けられており、主配線1およびバリア膜3からなる。主配線1およびバリア膜3のそれぞれの線膨張係数は、その周辺に設けられている絶縁層2,4,および5のそれぞれの線膨張係数よりも大きい。また、主配線1およびバリア膜3のそれぞれの融点は、絶縁層2,4,および5のそれぞれの融点よりも低い。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセル領域の周辺に金属電極を有するアンチフューズを製造歩留り良く形成する。

【解決手段】MOSトランジスタを備えたメモリセルを有するメモリセル領域と、アンチフューズを備えた周辺回路領域とを有する半導体装置において、メモリセルを構成するコンタクトプラグ又はビット配線と同層に形成される周辺回路のコンタクトプラグ又は配線を用いて、アンチフューズの電極を形成する。

(もっと読む)

半導体装置の製造方法

【課題】製造工程を簡略化することの可能な半導体装置の製造方法を提供する。

【解決手段】第2の層間絶縁膜14に、配線の上面を露出するように、第1の開口径とされた第1の開口部16、及び第1の開口径よりも小さい第2の開口径とされた第2の開口部17を一括形成し、次いで、第1及び第2の開口部の内面を覆う高誘電率絶縁膜19を成膜し、次いで、斜めイオン注入法により、第2の開口部の底面に形成された高誘電率絶縁膜にイオンが注入されないように、少なくとも第1の開口部の底面の外周に形成された高誘電率絶縁膜にイオンを注入し、その後、ウエットエッチングにより、イオンが注入された高誘電率絶縁膜を除去し、次いで、第1及び第2の開口部内を導電膜21で埋め込むことで、第1の開口部内にコンタクトプラグ22を形成すると共に、前記第2の開口部内に、第2の開口部に高誘電率絶縁膜及び導電膜よりなるアンチヒューズ素子23を形成する。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、ヒューズの微細化を図ること。

【解決手段】シリコン基板1に素子分離絶縁膜2を形成する工程と、素子分離絶縁膜2の上に第1の絶縁膜13を形成する工程と、第1の絶縁膜13にスリット13xを形成する工程と、スリット13xを通じて素子分離絶縁膜2をウエットエッチングして凹部2bを形成する工程と、凹部2bとスリット13xの各々の内面に第2の絶縁膜24を形成することにより、第2の絶縁膜24によりスリット13xを塞ぎつつ、凹部2b内にボイド24aを形成する工程と、ボイド24aの上の第2の絶縁膜24にホール25bを形成し、ホール25b内にボイド24aを露出させる工程と、露出したボイド24aとホール25bのそれぞれの中に導電膜27を形成することによりヒューズFを形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、ヒューズ層を覆う絶縁膜の膜厚を精度良く調整する。

【解決手段】半導体基板10上の第2の層間絶縁膜17上にヒューズ層18Tが形成され、ヒューズ層18Tは第3の層間絶縁膜20で覆われる。第3の層間絶縁膜20上には、キャップメタル24に覆われたパッド電極23が形成され、それらは第1及び第2のパッシベーション膜25,26に覆われる。次に、ヒューズ層18T上で開口する第1のレジスト層27をマスクとして、ヒューズ層18T上で第2のパッシベーション膜26から第3の絶縁膜の厚さ方向の途中までをエッチングする。その後、パッド電極23上で開口する第2のレジスト層30をマスクとして、パッド電極23上で第1及び第2のパッシベーション膜25,26及びキャップメタル層24をエッチングしてパッド電極23の表面を露出する。その後、保護膜32を形成する。

(もっと読む)

半導体装置及びその検査方法並びにその設計方法

【課題】不良箇所を容易に特定し得る半導体装置及びその形成方法並びにその設計方法を提供する。

【解決手段】配線パターン32aと、ダミーパターン32bと、一方の端部が配線パターンに電気的に接続され、他方の端部がダミーパターンに電気的に接続されたヒューズ32cとを有している。

(もっと読む)

1 - 20 / 176

[ Back to top ]