Fターム[5F033WW04]の内容

半導体集積回路装置の内部配線 (234,551) | 数値の特定 (5,273) | 濃度 (735)

Fターム[5F033WW04]に分類される特許

721 - 735 / 735

銅配線用超低誘電絶縁膜

【課題】銅配線用層間絶縁膜として有用な超低誘電薄膜を提供する。

【解決手段】本発明は、銅配線用超低誘電絶縁膜であって、更に詳しくは、マトリクス成分としてポリアルキルシルセスキオキサン前駆体またはその共重合体と、気孔形成用テンプレートとしてアセチルシクロデキストリンナノ粒子が溶解されている有機溶液でコーティングした後、ゾル−ゲル反応及び、高温で熱処理を行って形成された多孔性薄膜で、前記テンプレートとしてアセチルシクロデキストリンを選択使用し、最高60vol%までの量を含めることができ、形成された薄膜はマトリクス内に5nm以下の非常に小さい気孔が均一に分布されており、誘電率が1.5程度で低く、気孔間の相互接続性(interconnectivity)が非常に優れた特性を有する銅配線用超低誘電絶縁膜である。

(もっと読む)

金属の化学的機械的研磨用の新規なスラリー

一般に集積回路の製造に有用な、金属を取り除くための、及び、特に貴金属の化学的機械的研磨用の、スラリーは、過ヨウ素酸、研磨剤、及び緩衝系を組み合わせることによって、形成されてもよく、ここでそのスラリーのpHは、約(4)と約(8)との間にある。

(もっと読む)

(もっと読む)

精密ポリシリコン・レジスタ・プロセス

【課題】 製造されるポリシリコン・レジスタのシート抵抗の許容誤差をより正確に制御する精密ポリシリコン・レジスタを製造するためのプロセスを提供する。

【解決手段】 プロセスは、一般に、部分的に形成されたポリシリコン・レジスタを有するウェハに対して、エミッタ/FET活性化高速熱アニール(RTA)を行うステップと、それに続いて、保護誘電体層をポリシリコン上に堆積させるステップと、ドーパントを該保護誘電体層を通して該ポリシリコンに注入して、ポリシリコン・レジスタの抵抗を定めるステップと、シリサイドを形成するステップとを含む。

(もっと読む)

ボンドパッドの形成方法

パッシベーション層(68)及びポリイミド層(72)の下層には、ボンドパッド層(62)を覆うように最上層(64)が形成される。パッシベーション層(68)及びポリイミド層(72)の内部には、開口部(70,74)の形成時にボンドパッド層(62)を保護する最上層(64)を露出させるように、開口部(70,74)が形成される。一実施形態において、露出した最上層(64)は、過酸化水素及び水酸化アンモニウム等のアミンを用いて選択的にエッチングされる。この化学系は、ボンドパッド層(62)に攻撃を加えないため、ボンドパッド層の薄化が回避される。従って、ボンドパッドの信頼性が維持される。  (もっと読む)

(もっと読む)

半導体装置、半導体装置の製造方法及びプラズマCVD用ガス

本発明は、420℃以下の熱履歴を経たフッ素添加カーボン膜からなる絶縁膜を備えた半導体装置に関する。本発明の特徴は、前記フッ素添加カーボン膜中の水素原子の含有量が、前記熱履歴を経る前において、3原子%以下であることにある。 (もっと読む)

溝配線を有する半導体装置および半導体装置の製造方法

【課題】 多層配線において、ショートやビア抵抗増加のような目合わせずれによる問題を回避し、信頼性の高い多層配線を得る。

【解決手段】 半導体装置は、第1配線層(201)と、層間絶縁層(202〜208)とを具備する。第1配線層(201)は、基板の上面側に設けられ、第1配線を含む。層間絶縁層(202〜208)は、前記第1配線層(201)上に設けられ、一方の端を前記第1配線に接続されたビアと、前記ビアの他方の端に接続された第2配線とを含む。前記層間絶縁層(202〜208)はシリコン酸化膜より低い比誘電率を有する。前記層間絶縁層(202〜208)の上部は、下側から順に、シリコン酸化膜(206)、シリコン窒化膜(207)、シリコン酸化膜(208)を備える。

(もっと読む)

バリヤ金属上に直接銅めっきするマルチステップ電着法

本発明の実施形態は、基板表面に、通常はバリヤ層に銅シード層を堆積させる方法を教示している。その方法は、基板表面を銅溶液に入れるステップであって、該銅溶液が錯体形成銅イオンを含んでいる、前記ステップを含んでいる。電流又はバイアスを基板表面に印加し、錯体形成銅イオンを還元してバリヤ層に銅シード層を堆積させる。 (もっと読む)

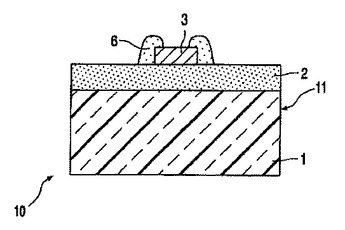

半導体デバイスを製造する方法およびその方法で使用するための装置

本発明は、基板(1)および少なくとも1つの半導体要素を含んだ半導体本体(11)を有した半導体デバイス(10)の製造方法に関する。その方法では、要素の形成後、少なくとも1つの電気的絶縁層(2)または電気的導体層(3)を含んだ層構造が形成され、開口部が、パターン形成されたフォトレジスト層(4)およびエッチング・プロセスの助けによって層構造中に形成され、残渣が、エッチング・プロセス中に半導体本体(11)の表面上に形成され、エッチング・プロセス後に、フォトレジスト層(4)が、酸素含有化合物を使用する処理によって灰にされ、その後、表面が、酸を水で希釈した溶液を含んだ洗浄剤を、室温より高い温度に加熱して使用する洗浄作業を受け、それによって形成された残渣が除去される。本発明によれば、硫酸が、洗浄剤用の酸として選択される。  (もっと読む)

(もっと読む)

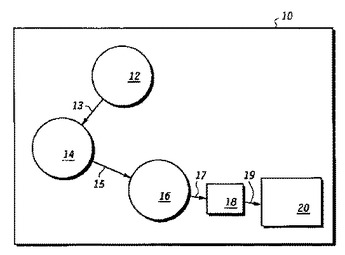

銅メタライゼーションのためのALD窒化タンタルの集積

窒化タンタル/タンタルバリア層を堆積させるための方法および装置が、集積処理ツールでの使用のために提供される。遠隔発生プラズマによる洗浄ステップの後、窒化タンタルは原子層堆積法で堆積され、タンタルはPVDで堆積される。窒化タンタル/タンタルは、堆積された窒化タンタルの下の導電性材料を露呈するために、誘電体層の部材の底部から除去される。場合によって、さらなるタンタル層が、除去ステップの後に物理気相堆積法で堆積されてもよい。場合によって、窒化タンタル堆積およびタンタル堆積は同一の処理チャンバで生じてもよい。シード層が最後に堆積される。 (もっと読む)

半導体製造プロセスの過程で導電面を不動態化するための方法

半導体ウェハの製造プロセスが開示されている。メタル配線の表面に発生するデンドライトや電気分解反応を抑止するため、半導体ウェハに対して溶液が適用される。その溶液は、CMP処理の際又はCMP洗浄後処理の際に適用される。その溶液は、界面活性剤及び防食剤を含む。一実施形態では、その溶液中に含まれる界面活性剤の濃度が約1重量パーセント未満に設定され、防食剤の濃度が約1重量パーセント未満に設定される。また、その溶液は、溶媒及び共溶媒を含むこともできる。別の実施形態では、その溶液が、界面活性剤及び防食剤を含まず、溶媒及び共溶媒を含む。一実施形態では、CMP処理及びCMP洗浄後処理を、約1μm未満の波長を持つ光の存在下で実施できる。  (もっと読む)

(もっと読む)

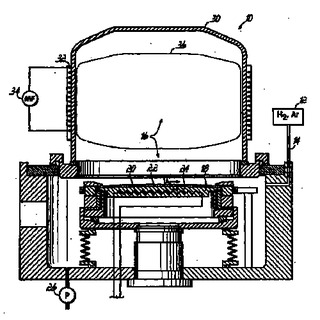

高温水素含有プラズマによるチャンバ及びウェーハ表面から物質を除去する方法及び装置

半導体ウェーハ処理装置(10)のチャンバ(16)と、清掃されるべき表面にバイアス電圧を掛けることなくガス混合物中に高密度プラズマを生成するためのみのICP電源と、に供給される、水素及び不活性ガスから成る清掃ガス混合物、例えば、水素含有量が体積で20%から80%の間にある混合物を使用する清掃方法が提供される。本発明の実施形態では、Si及びSiO2汚染物質又はCFx汚染物質は引き続く金属被着に先立ってシリコン・コンタクト(46)から清掃される。本発明の別の実施形態では、基準酸化物エッチング速度を回復するために酸化物をエッチングする以前にシリコン残留物は内部チャンバ表面から清掃される。

(もっと読む)

(もっと読む)

多層配線構造の形成方法

【課題】SOG膜のSi原子と有機基(例えばCH3基)やH基の結合がアッシング時に切れるのを抑制して誘電率を低く抑える。

【解決手段】低誘電率の有機又は無機SOG膜にパターン化レジスト膜をマスクとしてエッチングを行って配線溝を形成し、この後、枚葉式ダウンストリーム型のプラズマアッシング装置を用いて、酸素ガスプラズマによるアッシング処理を例えば1.2Torrの圧力雰囲気下で施してレジスト膜を除去し、この後配線溝にバリヤメタル形成後、Cuを電界メッキ法にて埋設して配線を形成する。

(もっと読む)

配線用シード膜および半導体装置の配線方法

【課題】 低コストにて歩留まり,信頼性,電気的特性の高い半導体装置を作製する。

【解決手段】 絶縁膜60上の下層絶縁膜61に銅の下層配線62を形成(S61)した後、プラズマCVD法により層間絶縁膜63,ストッパ膜64を順次形成し、ストッパ膜64における下層配線62上に孔64aを形成してから、ドライエッチングして層間絶縁膜63にコンタクトホール63aを形成する(S62)。その後、上層絶縁膜65を形成しマスク66を介してドライエッチングすることにより、上層絶縁膜65に溝部65aを形成すると共に、コンタクトホール63a中の上層絶縁膜65を除去する(S63)。そして、バリア膜67を形成(S64)した後、Cu−Ni膜,Cu−Zn膜,Cu−Zn−Ni膜のうち何れかを堆積してシード膜68を形成する(S65)。

(もっと読む)

低誘電率層間絶縁膜の形成方法

【課題】 半導体装置の層間絶縁膜などとして有用な低誘電率の膜を形成する方法と、この方法により形成される膜を提供すること。

【解決手段】 基材上に膜を成長させるのに十分な化学気相成長条件下で、シリルエーテル、シリルエーテルオリゴマー又は1以上の反応性基を有する有機ケイ素化合物を含む、有機ケイ素前駆物質を反応させて、約3.5以下の誘電率を有する層間絶縁膜を形成する。

(もっと読む)

表示素子用配線、これを利用した薄膜トランジスタ基板及びその製造方法

【課題】 物理的に接着力が向上し、電気的には接触抵抗が良好な特性を有する表示素子用配線及びこれを利用した薄膜トランジスタ基板並びにその製造方法を提供することを目的とする。

【解決手段】 表示素子用配線を、低融点金属の合金元素が少なくとも一つ以上合金されているAg合金で形成する。液晶表示パネルにおいて、このような表示素子用配線を用いてゲート配線22,24,26及びデータ配線65,66,68を形成すれば、接触部で他の導電物質と連結される過程で腐食が発生して素子の特性を低下させるのを防止できる。

(もっと読む)

721 - 735 / 735

[ Back to top ]