Fターム[5F033XX20]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 酸化防止 (315)

Fターム[5F033XX20]に分類される特許

1 - 20 / 315

半導体装置およびその製造方法

半導体装置及びその製造方法

半導体装置およびその作製方法

【課題】酸化物半導体膜と金属膜との接触抵抗を低減する。オン特性の優れた酸化物半導体膜を用いたトランジスタを提供する。高速動作が可能な半導体装置を提供する。

【解決手段】酸化物半導体膜を用いたトランジスタにおいて、酸化物半導体膜に窒素プラズマ処理を行うことで酸化物半導体膜を構成する酸素の一部が窒素に置換された酸窒化領域を形成し、該酸窒化領域に接して金属膜を形成する。該酸窒化領域は酸化物半導体膜の他の領域と比べ低抵抗となり、また、接触する金属膜との界面に高抵抗の金属酸化物を形成しにくい。

(もっと読む)

半導体チップ、これを含む半導体パッケージ、及びその製造方法

【課題】信頼性を向上させることができる高集積化された半導体チップ及びこれを含む半導体パッケージが提供される。

【解決手段】本発明にしたがう半導体チップは、基板と、前記基板を貫通している貫通ビアと、前記貫通ビアと前記基板との間に介在されたウェッティング膜と、前記ウェッティング膜と前記貫通ビアとの間に介在されたシード膜と、を含む。本発明の実施形態による半導体チップは突出された貫通ビアをウェッティング膜が覆っているので、導電パッドを追加に形成する必要がない。したがって、半導体チップの厚さを減らすことができ、構造が単純化されて半導体装置の高集積化により有利である。また、工程を単純化することができるので、生産収率を増大させ得る。

(もっと読む)

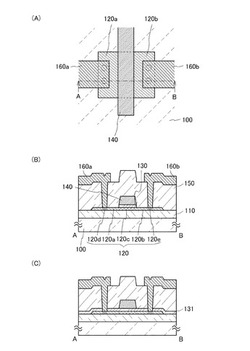

不揮発性記憶素子及び不揮発性記憶装置並びにそれらの製造方法

【課題】良好な電気的特性が得られる不揮発性記憶素子及びその製造方法を提供する。

【解決手段】第1の配線103と、第1の配線103上に形成され、第1の配線103に接続される第1のプラグ107及び第2のプラグ108と、第1電極109、第2電極113、及び抵抗変化層112を有し、第1のプラグ107上に形成され、第1電極109が第1のプラグ107と電気的に接続されている抵抗変化素子114と、抵抗変化素子114上に形成され、第2電極113と電気的に接続されている第2の配線119と、第2のプラグ108上に形成され、第2のプラグ108と電気的に接続されている第3の配線121とを備え、第1のプラグ107の上面と第2のプラグ108の上面とが略同一平面内に形成され、かつ第2の配線119の上面と第3の配線121の上面とが略同一平面内に形成されている。

(もっと読む)

電子部品用積層配線膜および被覆層形成用スパッタリングターゲット材

【課題】 耐湿性や耐酸化性を改善し、さらに、低抵抗な主導電層であるAlと積層した際に、加熱工程を経ても低い電気抵抗値を維持できる、Mo合金からなる被覆層を用いた電子部品用積層配線膜および被覆層を形成するためのスパッタリングターゲット材を提供する。

【解決手段】 基板上に金属膜を形成した電子部品用積層配線膜において、Alを主成分とする主導電層と該主導電層の一方の面および/または他方の面を覆う被覆層からなり、該被覆層は原子比における組成式がMo100−x−y−Nix−Tiy、10≦x≦30、3≦y≦20で表され、残部が不可避的不純物からなる電子部品用積層配線膜。

(もっと読む)

電子部品用積層配線膜および被覆層形成用スパッタリングターゲット材

【課題】 耐湿性や耐酸化性を改善し、さらに低抵抗な主導電層であるCuと積層した際に、加熱工程を経ても低い電気抵抗値を維持できる、Mo合金からなら被覆層を用いた電子部品用積層配線膜および被覆層を形成するためのスパッタリングターゲット材を提供する。

【解決手段】 基板上に金属膜を形成した電子部品用積層配線膜において、Cuを主成分とする主導電層と該導電層の一方の面および/または他方の面を覆う被覆層からなり、該被覆層は原子比における組成式がMo100−x−y−Nix−Tiy、10≦x≦50、3≦y≦30、x+y≦53で表され、残部が不可避的不純物からなる電子部品用積層配線膜。

(もっと読む)

プラズマ処理による酸化物又は他の還元可能な汚染物質の基板からの除去

【課題】VLSI技術及びULSI技術において多段相互接続は、アスペクト比の高いバイアや他の相互接続が注意深く処理されることを要する。これらの相互接続の確実な形成技術を提供する。

【解決手段】窒素と水素を含有する化合物、一般にアンモニアを使用し、次層を上へ堆積するに先立ち相対的に低い温度で酸化物又は他の汚染物質を還元する、プラズマ還元プロセスを提供する。酸化物の層の典型的な物理的スパッタ洗浄プロセスと比較して、層の粘着特性が改善され酸素の存在が減少する。このプロセスは、デュアルダマシン構造、とりわけ銅が応用されている場合の複雑な要求に特に有効であろう。

(もっと読む)

半導体装置

【課題】層間絶縁膜のエッチングの際に半導体層がエッチングされることによるコンタク

ト抵抗の増大を防ぎ、書き込み特性及び電荷保持特性に優れた不揮発性半導体記憶装置及

びその作製方法を提供する。

【解決手段】ソース領域又はドレイン領域とソース配線又はドレイン配線との間に導電層

を設ける。また、該導電層は、制御ゲート電極を形成する導電層と同じ導電層からなる。

また、該導電層を覆うように絶縁膜が設けられており、該絶縁膜は該導電層の一部が露出

するコンタクトホールを有する。また、該ソース配線又はドレイン配線は、該コンタクト

ホールを埋めるように形成されている。

(もっと読む)

電子部品用積層配線膜

【課題】 Moの持つSiバリヤ性、ITOコンタクト性という利点を維持しながら、耐酸化性を改善し、尚且つCuとの積層時や信号ケ−ブルの取り付け等の加熱工程を経ても低い電気低抵値を維持できる、電子部品用積層配線膜を提供する。

【解決手段】 基板上に金属膜を形成した電子部品用積層配線膜において、Cuでなる主導電層と、該主導電層の一方の面および/または他方の面を覆う被覆層からなり、該被覆層は原子比における組成式がMo100−XNiX、10≦X≦70で表され、残部不可避的不純物からなるMo−Ni合金である電子部品用積層配線膜。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】実際の強誘電体メモリセルについて疲労特性を直接に測定する試験方法を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板上に形成された強誘電体キャパシタの疲労特性の面内分布を取得する第1の工程と、前記面内分布に基づいて、半導体装置を製造する第2の工程と、を含み、前記第2の工程は、前記半導体装置が形成される基板上に複数の強誘電体キャパシタを形成し、前記第1の工程で取得された疲労特性の面内分布から、前記半導体装置が形成される基板上の特定領域を指定し、前記特定領域に形成された前記強誘電体キャパシタについて疲労特性を測定し、前記特定領域の強誘電体キャパシタについて測定した前記疲労特性に基づき、前記特定領域の強誘電体キャパシタについて良否判定を行い、前記良否判定の結果が良であれば、前記複数の強誘電体キャパシタの全てについて良と判定する。

(もっと読む)

半導体装置

【課題】浮遊状態の配線と洗浄水との間において高い密度で電荷が移動することに起因する配線の高抵抗化を防ぐ。

【解決手段】半導体製造装置の製造工程中において、半導体基板1Sなどと絶縁された浮遊状態となる銅配線である第1層配線L1の上面に、電気的に機能する接続ビアPL2と電気的に機能しないダミービアDP2とを接続させて形成する。これにより、第1層配線L1の上面に接続ビアPL2を形成するためのビアホールを形成した後の洗浄工程中に、第1層配線L1に溜まった電荷が洗浄水中に移動する際、前記電荷をダミービアDP2形成用のビアホールにも分散させることで、接続ビアPL2形成用のビアホールの底部のみに前記電荷が集中することを防ぐ。

(もっと読む)

半導体装置の製造方法

【課題】TATの短縮及び製造コストの低下を図る。

【解決手段】実施形態に係わる半導体装置の製造方法は、下地層上にピラーを形成する工程と、GCIB法を用いて、下地層上に、ピラーを覆い、かつ、上面の最も低い部分がピラーの上面よりも下にある絶縁層を形成する工程と、CMP法を用いて、絶縁層及びピラーを、絶縁層の上面の最も低い部分まで研磨する工程とを備える。

(もっと読む)

強誘電体キャパシタ

【課題】還元性雰囲気による特性劣化を抑制することができる構造の強誘電体キャパシタを提供する。

【解決手段】強誘電体キャパシタ積層構造8は、強誘電体膜3と、強誘電体膜の一方表面に接する下部電極2と、強誘電体膜3の他方表面に接する上部電極4とを含む。上部電極4および下部電極2のうちのうちの少なくともいずれか一方が、酸化物導電体層と金属層とを交互に積層した積層電極構造を有している。この積層電極構造は、酸化物導電体層および金属層のうちの少なくともいずれか一方を2層以上含む。

(もっと読む)

Cu合金膜および表示装置

【課題】酸化物半導体層を用いた表示装置において、保護膜形成時のプラズマ処理におけるCu配線の酸化を有効に防止し得る技術を提供する。

【解決手段】基板1の上に、基板側から順に、薄膜トランジスタの半導体層4と、電極に用いられるCu合金膜5と、保護膜6と、を備えており、半導体層は酸化物半導体からなる。Cu合金膜5は、基板側から順に、第一層(X)5aと第二層(Z)5bを含む積層構造を有し、第一層(X)は、純Cu、またはCuを主成分とするCu合金であって第二層(Z)よりも電気抵抗率の低いCu合金からなり、第二層(Z)は、Zn、Ni、Ti、Al、Mg、Ca、W、Nb、希土類元素、Ge、およびMnよりなる群から選択される少なくとも1種の元素を合計で2〜20原子%含むCu−Z合金からなり、第二層(Z)の少なくとも一部は、前記保護膜と直接接続されている。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極の形成過程で、余分な酸化膜を確実に除去する。

【解決手段】貫通電極を形成するビアホール25の内面に酸化膜26を形成した後、Cu膜28を埋め込む。第1層間絶縁膜22の上に形成された余分なCu膜28をCMP法による研磨で除去するときに、酸化膜26も研磨されて膜厚が薄くなる。膜厚が薄くなった酸化膜26Bをハードマスクとして第1層間絶縁膜14に配線溝を形成する。このとき、酸化膜26Bの膜厚が薄くなる。配線溝に導電材を埋め込んだ後、余分な導電材を研磨によって除去する。このとき、残りの酸化膜26Bが全て研磨により除去される。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高誘電率ゲート絶縁膜を用いたCMIS型半導体集積回路において、短チャネル長、且つ狭チャネル幅のデバイス領域では、ソースドレイン領域の活性化アニールによって、高誘電率ゲート絶縁膜とシリコン系基板部との界面膜であるILの膜厚が増加することによって、閾値電圧の絶対値が増加するという問題がある。

【解決手段】本願の一つの発明は、MISFETを有する半導体集積回路装置の製造方法において、MISFETのゲートスタック及びその周辺構造を形成した後、半導体基板表面を酸素吸収膜で覆い、その状態でソースドレインの不純物を活性化するためのアニールを実行し、その後、当該酸素吸収膜を除去するものである。

(もっと読む)

成膜方法およびCu配線の形成方法

【課題】被処理基板を加熱してトレンチやホールの間口部のオーバーハングを抑制しつつ金属膜を成膜するとともに、成膜後に速やかに被処理基板の温度を低下させることができる成膜方法を提供すること。

【解決手段】載置台を低温に保持して、載置台上に被処理基板を吸着させずに載置する工程と、プラズマ生成ガスのプラズマを生成し、載置台に高周波バイアスを印加した状態で、被処理基板にプラズマ生成ガスのイオンを引きこんで被処理基板を予備加熱する工程と、ターゲットに電圧を印加して金属粒子を放出させ、プラズマ生成ガスのイオンとともにイオン化した金属イオンを被処理基板に引きこんで金属膜を形成する工程と、被処理基板を低温に保持された載置台に吸着させ、載置台と被処理基板との間に伝熱ガスを供給して被処理基板を冷却する工程とを有する。

(もっと読む)

銅配線の形成方法、配線基板の製造方法および配線基板

【課題】銅粒子の酸化、燃焼を防止し、銅配線の導電性を向上させるとともに経時劣化を抑えることができる銅配線の形成方法、配線基板の製造方法および配線基盤を提供することを目的とする。

【解決手段】粒子径が100nm以下の炭素被膜銅粒子14を、基板10上に配線パターンを形成するパターン形成工程と、配線パターンを酸素プラズマ処理する酸素プラズマ処理工程と、配線パターンを還元プラズマ処理する還元プラズマ処理工程と、を有することを特徴とする銅配線の形成方法、配線基板の製造方法および配線基板である。

(もっと読む)

処理方法および記憶媒体

【課題】低誘電率膜のダメージ回復処理を行う際に、比誘電率やリーク電流値を低く維持しつつ内部の水分を除去することができる処理方法を提供すること。

【解決手段】被処理基板に形成された、表面部分にダメージ層を有する低誘電率膜に回復処理を施すにあたり、その分子が、低誘電率膜のダメージ層の内部に浸透できる程度に小さく、ダメージ層内の水分を除去することが可能な第1処理ガスと、ダメージ層の表面に疎水性で緻密な改質層を形成する第2処理ガスとを低誘電率膜のダメージ層に作用させる。

(もっと読む)

1 - 20 / 315

[ Back to top ]