Fターム[5F033XX29]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 拡散、突き抜け防止 (992) | シリコンの拡散、突き抜け防止 (20)

Fターム[5F033XX29]に分類される特許

1 - 20 / 20

薄膜トランジスタおよびその製造方法

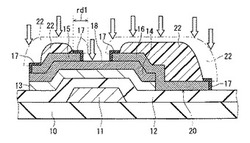

【課題】オフ電流および漏れ電流が抑制された薄膜トランジスタ、および前記薄膜トランジスタを歩留り良く製造することのできる薄膜トランジスタの製造方法を提供する。

【解決手段】ゲート電極12上にゲート絶縁膜12を介して順次形成されるSi(i)膜13およびSi(n)膜14上に金属膜を形成し、フォトレジストパターン22をマスクとしてエッチングし、ソース電極15およびドレイン電極16を形成する。酸素を含むプラズマで処理して、フォトレジストパターン22の側面を後退させるとともに、ソース電極15およびドレイン電極16の側面および露出した上面にAl酸化皮膜17を形成する。残存するフォトレジストパターン22およびAl酸化皮膜17をマスクとして、チャネル部18のSi(n)膜14およびSi(i)膜13の表面の一部をエッチングする。

(もっと読む)

薄膜トランジスタ基板および表示デバイス

【課題】ソース電極とドレイン電極のドライエッチングレートの低下や、エッチング残さを引き起こすことがなく、半導体層と、ソース電極やドレイン電極といった配線金属の間からバリアメタルを省略することができる薄膜トランジスタ基板および表示デバイスを提供する課題とする。

【解決手段】半導体層1、ソース電極2、ドレイン電極3、透明導電膜4を有する薄膜トランジスタ基板において、ソース電極2とドレイン電極3は、ドライエッチング法によるパターニングで形成されたGe:0.3原子%〜1.2原子%、Co:0.05原子%〜2.0原子%、Laおよび/またはNd:0.1原子%〜0.5 原子%を含有するAl合金薄膜より成り、半導体層1と直接接続している。

(もっと読む)

半導体装置とその製造方法

【課題】表面電極にはんだ接合層を有する半導体装置において、その製造工程でウェハの反りやはんだ接合層のクラックが発生することを抑制する。

【解決手段】表面電極は、半導体基板に接する第1層として250℃以下の基板温度でスパッタ法によってAl−Si層またはAl−Si−Cu層を形成し、その表面に積層する第2層として400℃以上の基板温度でスパッタ法によってAl層またはAl−Cu層を形成し、その表面側に、はんだ接合層、はんだ層を形成することによって、製造する。

250℃以下の基板温度で第1層を形成するため、シリコンノジュールの発生を防止することができ、第2層を400℃以上の基板温度で形成するため、第2層の平坦性を確保でき、ウェハの反りやはんだ接合層のクラック発生を防止することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】高温環境下での絶縁膜の腐食を抑制して、絶縁不良を回避した半導体装置及びその製造方法を提供することことを課題とする。

【解決手段】半導体基板11上にエピタキシャル成長により第1絶縁膜12が積層形成され、この第1絶縁膜12上には、耐熱性の電極13が選択的に形成され、この電極13の上部には、シリカガラスを主成分とする層間絶縁膜14が形成され、この層間絶縁膜14の表面には絶縁バリア膜15が形成され、この絶縁バリア膜15の上には、Alの配線16が形成され、絶縁バリア膜15は、絶縁性の窒化物、炭化物、窒化炭化物の単層膜、多層膜、または混合膜で構成されている。

(もっと読む)

表示装置用Al合金膜、薄膜トランジスタ基板および表示装置

【課題】Al合金膜とTFTの半導体層との間のバリアメタル層を省略可能な新規のSiダイレクトコンタクト技術を提供する。詳細には、Al合金膜をTFTの半導体層と直接接続しても、AlとSiの相互拡散を防止でき、良好なTFT特性が得られると共に、TFTの製造工程でAl合金膜に約100〜300℃の熱履歴が加わった場合でも、低い電気抵抗と優れた耐熱性が得られる新規なSiダイレクトコンタクト技術を提供する。

【解決手段】本発明の表示装置用Al合金膜は、表示装置の基板上で、薄膜トランジスタの半導体層と直接接続されるAl合金膜であって、上記Al合金膜は、Geを0.1〜4原子%;La、GdおよびNdよりなる群から選ばれる少なくとも1種を0.1〜1原子%;並びにTa、Nb、Re、ZrおよびTiよりなる群から選ばれる少なくとも1種を含有する。

(もっと読む)

酸素含有前駆体を用いる誘電体バリアの堆積

低誘電率及び優れた電気特性等の改良されたバリア誘電体特性を有する、ケイ素、炭素、酸素及び水素を有する前駆体を含む誘電体バリアフィルムを堆積させるための方法を与える。この方法は、相互接続構造のためのダマシン又は二重ダマシン集積で、又は他の誘電体バリア用途で用いられるバリア層に関して重要となるであろう。この例では、バリア性能を改良する特定の構造特性が注目される。  (もっと読む)

(もっと読む)

薄膜半導体装置およびその製造方法

【課題】 微細化に伴うコンタクト抵抗の増加を防止した、信頼性の高い素子特性を有する薄膜半導体装置を提供すること。

【解決手段】 透明絶縁性基板上に形成され、所定の間隔を隔てて第1導電型の不純物を含むソース領域及び第1導電型の不純物を含むドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜、前記ゲート絶縁膜上に形成されたゲート電極、前記島状半導体層及びゲート電極を覆う層間絶縁膜、及び前記ソース領域及びドレイン領域にそれぞれ接続する、前記層間絶縁膜に形成された第1及び第2のコンタクト孔内にそれぞれ埋め込まれた第1導電型の不純物を含む凸型ソース多結晶半導体層並びに第1導電型の不純物を含む凸型ドレイン多結晶半導体層を具備することを特徴とする。

(もっと読む)

薄膜トランジスタ基板および表示デバイス

【課題】ソース電極とドレイン電極のドライエッチングレートの低下や、エッチング残さを引き起こすことがなく、半導体層と、ソース電極やドレイン電極といった配線金属の間からバリアメタルを省略することができる薄膜トランジスタ基板および表示デバイスを提供する課題とする。

【解決手段】半導体層1、ソース電極2、ドレイン電極3、透明導電膜4を有する薄膜トランジスタ基板において、ソース電極2とドレイン電極3は、ドライエッチング法によるパターニングで形成されたSiおよび/またはGe:0.1〜1.5 原子%、Niおよび/またはCo:0.1〜3.0原子%、Laおよび/またはNd:0.1〜0.5 原子%を含有するAl合金薄膜より成り、半導体層1と直接接続している。

(もっと読む)

半導体装置及びその製造方法

【課題】Wを材料とする接続部の下地膜の形成工程として、形成容易なプロセスを選択することができ、下層のCu配線である第1の配線のCuの浸食を抑制することにより、第1の配線と接続部との間における接触抵抗を低く抑えるとともにその均一性を高め、信頼性の高い半導体装置を実現する。

【解決手段】熱CVD法によりWF6、H2及びB2H6を含有し、シラン系ガスを含有しない第1の供給ガスを用いてW膜18aを形成した後、WF6及びH2を含有する第2の供給ガスを用いてW膜18bを形成し、CMPを経て、ビア孔16をW膜18で充填するWプラグ19を形成する。

(もっと読む)

Al合金膜、電子デバイス及び電気光学表示装置用アクティブマトリックス基板

【課題】ITOやSiとの界面拡散を防止するとともに、低温プロセスが要求される各種電子デバイスに適用可能な低抵抗の電極膜用Al合金膜を提供すること。

【解決手段】本発明の一態様に係るAl合金膜は、Niからなる第1の添加元素と、元素周期表の周期2又は3に属する2a族のアルカリ土類金属、3b、4b族の半金属から選ばれる少なくとも1種類以上の第2の添加元素とを含む。また、第1の添加元素の組成比は0.5〜5at%であり、第2の添加元素の組成比は0.1〜3at%である。

(もっと読む)

薄膜トランジスター

【課題】薄膜トランジスターを提供する。

【解決手段】ガラス基板1の上にゲート電極膜2を形成し、前記ガラス基板1およびゲート電極膜2の上に窒化珪素膜3を形成し、前記窒化珪素膜3の上にアモルファスSi膜4を形成し、前記アモルファスSi膜4の上にバリア膜を介していずれもCu−O−AEM(アルカリ土類金属)銅合金膜15の下地層を有するCu−AEM(アルカリ土類金属)銅合金からなるドレイン電極膜5およびソース電極膜6を形成し、前記アモルファスSi膜4、ドレイン電極膜5およびソース電極膜6の上に窒化珪素膜3´を被覆形成してなる薄膜トランジスターにおいて、前記バリア膜は、Cu−Si−O−AEM(アルカリ土類金属)銅合金膜19で構成されていることを特徴とする。

(もっと読む)

薄膜トランジスター

【課題】薄膜トランジスターを提供する。

【解決手段】ガラス基板1の上にゲート電極膜2を形成し、前記ガラス基板1およびゲート電極膜2の上に窒化珪素膜3を形成し、前記窒化珪素膜3の上にアモルファスSi膜4を形成し、前記アモルファスSi膜4の上にバリア膜を介していずれもCu−O−Zn銅合金膜15の下地層を有するCu−Zn銅合金からなるドレイン電極膜5およびソース電極膜6を形成し、前記アモルファスSi膜4、ドレイン電極膜5およびソース電極膜6の上に窒化珪素膜3´を被覆形成してなる薄膜トランジスターにおいて、前記バリア膜は、Cu−Si−O−Zn銅合金膜19で構成されていることを特徴とする。

(もっと読む)

薄膜トランジスター

【課題】薄膜トランジスターを提供する。

【解決手段】ガラス基板1の上にゲート電極膜2を形成し、前記ガラス基板1およびゲート電極膜2の上に窒化珪素膜3を形成し、前記窒化珪素膜3の上にアモルファスSi膜4を形成し、前記アモルファスSi膜4の上にバリア膜を介して純銅からなるドレイン電極膜5およびソース電極膜6を形成し、前記アモルファスSi膜4、ドレイン電極膜5およびソース電極膜6の上に窒化珪素膜3´を被覆形成してなる薄膜トランジスターにおいて、前記バリア膜は、炭化ケイ素膜12で構成されており、微量炭素含有銅膜15は有ることが好ましいが無くてもよい。

(もっと読む)

薄膜トランジスター

【課題】薄膜トランジスターを提供する。

【解決手段】ガラス基板1の上にゲート電極膜2を形成し、前記ガラス基板1およびゲート電極膜2の上に窒化珪素膜3を形成し、前記窒化珪素膜3の上にアモルファスSi膜4を形成し、前記アモルファスSi膜4の上にバリア膜を介していずれも酸素含有銅膜15の下地層を有する純銅からなるドレイン電極膜5およびソース電極膜6を形成し、前記アモルファスSi膜4、ドレイン電極膜5およびソース電極膜6の上に窒化珪素膜3´を被覆形成してなる薄膜トランジスターにおいて、

前記バリア膜は、銅、シリコンおよび酸素からなる酸素含有銅合金膜19で構成されていることを特徴とする。

(もっと読む)

薄膜トランジスタ基板、および表示デバイス

【課題】バリアメタル層を省略しても優れたTFT特性を発揮し得、ソース−ドレイン配線をTFTの半導体層に直接かつ確実に接続することができる技術を提供する。

【解決手段】薄膜トランジスタの半導体層33と、ソース−ドレイン電極28,29とを有する薄膜トランジスタ基板において、ソース−ドレイン電極28,29は、窒素を含有する窒素含有層、または窒素及び酸素を含有する酸素窒素含有層28a、29aと、純Cu又はCu合金の薄膜28b、29bとからなっている。窒素含有層を構成する窒素の一部若しくは全部、または、酸素窒素含有層を構成する窒素または酸素の一部若しくは全部は、薄膜トランジスタの半導体層33のSiと結合している。また、純CuまたはCu合金の薄膜28b、29bは、窒素含有層または酸素窒素含有層28a、29aを介して薄膜トランジスタの半導体層33と接続している。

(もっと読む)

薄膜トランジスタ基板、および表示デバイス

【課題】バリアメタル層を省略しても優れたTFT特性を発揮し得、ソース−ドレイン配線をTFTの半導体層に直接かつ確実に接続することができる技術を提供する。

【解決手段】薄膜トランジスタの半導体層33と、ソース−ドレイン電極28,29とを有する薄膜トランジスタ基板において、ソース−ドレイン電極28,29は、窒素を含有する窒素含有層、または窒素及び酸素を含有する酸素窒素含有層28a、29aと、純Cu又はCu合金の薄膜28b、29bとからなっている。窒素含有層を構成する窒素の一部若しくは全部、または、酸素窒素含有層を構成する窒素または酸素の一部若しくは全部は、薄膜トランジスタの半導体層33のSiと結合している。また、純CuまたはCu合金の薄膜28b、29bは、窒素含有層または酸素窒素含有層28a、29aを介して薄膜トランジスタの半導体層33と接続している。

(もっと読む)

Al−Ni−B合金配線材料及びそれを用いた素子構造

【課題】 薄膜トランジスタや透明電極層を備える表示デバイスにおいて、ITOやIZOなどの透明電極層との直接接合が可能であるとともに、n+−Siなどの半導体層とも直接接合が可能なAl系合金配線材料を提供する。

【解決手段】 Al−Ni−B合金配線材料において、ニッケル含有量をニッケルの原子百分率Xat%、ボロンの含有量を原子百分率Yat%とした場合、式0.5≦X≦10.0、0.05≦Y≦11.0、Y+0.25X≧1.0、Y+1.15X≦11.5の各式を満足する領域の範囲内にあり、残部がアルミニウムであるAl−Ni−B合金配線材料とした。

(もっと読む)

半導体装置の製造方法

【課題】 層厚の厚い電極部および信頼性の高い保護膜を形成することができる半導体装置の製造方法を提供する。

【解決手段】 半導体層21の積層方向Zの一表面上に電極部34を形成する。次に半導体層21および電極部34とを予め定める第1の温度T1のN2雰囲気下でシンタ処理し、半導体層21と電極部34とのオーミック性を向上させる。次にPSG膜35がアニーリングされかつ堆積される予め定める第2の温度T2において、酸化膜22の表面と電極部34の表面とにPSG膜35を堆積して形成する。次にPSG膜35の一部をエッチングすることによって、電極部34の一部が露出するように第2貫通孔37を形成する。

(もっと読む)

基板処理装置,基板処理方法,プログラム,プログラムを記録した記録媒体

【課題】下地との界面がより平坦(フラット)で均一なTiシリサイド膜を形成することができ,これにより一層低抵抗なコンタクトを形成することがきる。

【解決手段】基板処理装置100は,処理室104A〜104Dに共通に連結される第1共通搬送室102と,処理室104E,104Fに共通に連結される第2共通搬送室120とを備える。各処理室104E,104F,104A,104C,104Bはそれぞれ,Siウエハ上の自然酸化膜を含む異物とガス成分とを化学反応させて生成物を生成するCOR処理室,Siウエハ上に生成された生成物を熱処理により除去するPHT処理室,SiウエハのSi表面上にTi膜を成膜するTi膜成膜処理室,Ti膜と下地との間で珪化反応を起させてTiシリサイド膜を形成するシリサイド形成処理室,Tiシリサイド膜上にTiN膜を成膜するTiN膜成膜処理室として構成した。

(もっと読む)

半導体装置の製造方法

【課題】 貫通電極を有した半導体装置の製造方法において、工程を簡略化して製造コストを極力低く抑えると共に、歩留まりの向上を図る。

【解決手段】 半導体基板10の表面に第1の絶縁膜11を形成し、その一部をエッチングして、半導体基板10の一部を露出する開口部11aを形成する。次に、開口部11a内から第1の絶縁膜11上に延びるパッド電極12を形成する。半導体基板10の裏面上には第2の絶縁膜15を形成する。次に、開口部11aよりも大きい開口径を有したビアホール16を形成する。そして、ビアホール16内から第2の絶縁膜15上に延びる第3の絶縁膜17を形成し、ビアホール16の底部の第3の絶縁膜17をエッチングしてパッド電極12を露出する。その後、ビアホール16内に貫通電極19及び配線層20を形成する。最後に、半導体基板10を複数の半導体チップ10Aに切断分離する。

(もっと読む)

1 - 20 / 20

[ Back to top ]