Fターム[5F033XX31]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 短絡防止 (613)

Fターム[5F033XX31]に分類される特許

201 - 220 / 613

半導体装置およびその製造方法

【課題】半導体装置の小型化が進んでも半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】本発明の技術的思想は、積層形成される窒化シリコン膜SN1〜SN3のそれぞれの膜厚を一定値ではなく、トータルの総膜厚を一定に保ちながら、上層の窒化シリコン膜SN3から下層の窒化シリコン膜SN1にしたがって膜厚を薄くするように構成している点にある。これにより、歪シリコン技術を実効あらしめる窒化シリコン膜SN1〜SN3の引張応力を確保しながら、特に、最上層の窒化シリコン膜SN3の埋め込み特性を改善できる。

(もっと読む)

半導体装置の配線構造物及びその形成方法

【課題】後工程における、キャパシタの下部電極と接続されるべき第2コンタクトプラグの形成の際の洗浄液による第1コンタクトパッドの損傷を防止できる、半導体装置の配線構造物及びその形成方法を提供する。

【解決手段】配線構造物は、第1コンタクトパッド126、第1コンタクトプラグ150、スペーサー140、及び層間絶縁膜パターン120、130を含む。第1コンタクトパッド126は、基板100の第1コンタクト領域116aと電気的に接続される。第1コンタクトプラグ150は、第1コンタクトパッド126上に具備され、第1コンタクトパッド126と電気的に接続される。スペーサー140は、第1コンタクトプラグ150の側壁と第1コンタクトパッド126の側壁の上部とに同時に面接する。層間絶縁膜パターン120,130は、コンタクトパッド126とスペーサー140を収容する開口を有する。

(もっと読む)

半導体装置

【課題】信頼性が高く、特性の改善された半導体装置を提供すること。

【解決手段】本発明の一態様に係る半導体装置1は、ワンチップに規則性を有するレイアウト領域と、規則性のないレイアウト領域を備える半導体装置であって、下層導電層11と、下層導電層11上に形成された層間絶縁膜と、その上に形成された上層配線層M1と、下層導電層11と上層配線層M1とを、実質的に最短距離で電気的に接続するように配設した接続プラグ10とを備える。そして、規則性を有するレイアウト領域における少なくとも一部の領域において、下層導電層11と上層配線層M1との電気的接続が、下層導電層11の直上から延在する直上位置、当該直上位置から離間したシフト位置に配設した少なくとも2つの接続プラグ10と、これらを電気的に接続するための中間接続層20により行われている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半田バンプが採用された半導体装置において、隣接する半田バンプ同士の接触の抑制が図られた半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置は、第1主表面を有する半導体チップ120と、第1主表面に形成された複数の電極123と、電極123ごとに複数形成されたランド部127と、半導体チップ120の第1主表面と対向する第2主表面を有するパッケージ基板160と、第2主表面に形成された複数の電極162と、電極162に形成されたランド部170と、ランド部127およびランド部170とを接続する半田バンプ125とを備える。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置に含まれる半導体基板と当該半導体基板に形成される貫通孔(TSV)を含む配線との間の絶縁性を良好に保つことができる半導体装置の製造方法を提供する。

【解決手段】

貫通孔の内壁に形成された絶縁膜の開口底部に対応する部分を除く部分をエッチングレジストで被膜し、当該エッチングレジストをマスクとしたエッチングにより当該絶縁膜を除去して電極パッドを露出させた後、導電層を形成して配線する。

(もっと読む)

半導体装置

【課題】対向、近接する拡散層と導体との間の漏れ電流を抑制し、効率を向上が図られた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1と、半導体基板1を貫通する貫通電極7と、半導体基板1の上部であって、貫通電極7の側方に位置する領域に設けられた拡散層24と、拡散層24の上部に設けられた拡散層22とを備えている。貫通電極7の側面のうち拡散層24に対向する部分は湾曲しており、拡散層24の表面のうち貫通電極7に対向する部分は湾曲している。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】層間絶縁膜として低誘電率膜を用いて配線溝を形成する際のダメージ層の形成による配線間容量の増加を抑制する。

【解決手段】低誘電率膜114の側壁に形成されたダメージ層130を除去する工程(図3(a)、3(b))と、化学気相成長法により第2の保護絶縁膜134を形成し、第1の保護絶縁膜116および低誘電率膜114の側壁を第2の保護絶縁膜134で覆って第2の凹部136cを形成する工程(図3(c))と、配線溝136dが低誘電率膜114の表面に選択的に第2の保護絶縁膜134が形成された側壁を有するように、第2の保護絶縁膜134をエッチバックして成形する工程(図3(d))とにより配線溝136dを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ビアホール下方でのスペーサ膜の閉塞を回避するとともに、ビアプラグの上方で隣接する配線層との間の余裕距離を確保することができる半導体装置を提供する。

【解決手段】シリコン基板1上に設けられた上面から下面まで貫通するコンタクトプラグ32を有する第1の層間絶縁膜30と、第1の層間絶縁膜30上に形成され、コンタクトプラグ32の形成位置に対応する位置の上面から下面まで貫通するビアホール41を有する第2の層間絶縁膜40と、ビアホール41内にコンタクトプラグ32と電気的に接触するように導電性材料が埋め込まれたビアプラグ43と、を備え、ビアホール41を形成する側壁は、第2の層間絶縁膜40の上面から下面に向かって、基板面に平行な方向の断面積が徐々に減少する順テーパ状を有し、ビアホールの上端部から所定の深さまでの側壁に、第2の層間絶縁膜40とは異なる絶縁性材料からなるスペーサ膜42が埋め込まれている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】エアーギャップ型の多層配線構造を有する半導体装置の上部配線のたわみを少なくするとともに、前記半導体装置の製造方法を簡略化するという課題があった。

【解決手段】半導体素子102を含む層間膜層95と、層間膜層95上に備えられ、エアーギャップ部96cを有する多層配線部96と、層間膜層95の上に立設され、多層配線部96を構成する複数の配線部のうちいずれか一つの配線部を支持するものであって、前記配線部と同一の材料からなり、前記一の配線部のみと電気的に接続された柱状の支持体51と、を具備してなる半導体装置111を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極のショート不良を引き起こすことなく、貫通電極とパッド電極との密着性を向上させる。

【解決手段】開口部22が設けられたパッド電極21b上にエッチストッパ膜23を積層し、半導体基板11に形成された貫通孔41に貫通電極45を埋め込む際に、貫通電極45の先端が、開口部22を介してパッド電極21bの一部を突き抜け、エッチストッパ膜23で止められるように構成する。

(もっと読む)

半導体装置

【課題】隣接する配線間及び配線と隣接するコンタクトプラグとの間に発生するリーク電流の低減、及びこれらの間の耐圧を向上させることができる半導体装置を提供する。

【解決手段】半導体基板11上には層間絶縁膜12が形成され、層間絶縁膜12内にはコンタクトプラグ13が埋め込まれている。層間絶縁膜12上には層間絶縁膜14が形成されている。コンタクトプラグ13上の層間絶縁膜14に形成された溝内には、銅を含む配線層15が形成されている。配線層15間の層間絶縁膜14内には、絶縁膜16が形成されている。コンタクトプラグ13は上面の一部に窪みを有し、絶縁膜16は層間絶縁膜14の上面からコンタクトプラグ13が有する窪みまで形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】Cu配線パターンとキャップ層との界面を伝うCuの拡散を抑制し、同時にCu配線パターンの抵抗の増大を抑制するCuダマシン配線の製造法を提供する。

【解決手段】基板41上に側壁面と底面とにより画成された凹部を有する絶縁膜45を形成する。側壁面のうち、上端部を含む上側の第1の部分Dを覆い、凹部の底面と下側の第2の部分においては前記絶縁膜が露出するように覆う、金属膜47を形成する。凹部の側壁面と底面とを連続的に覆う導電性拡散障壁膜48を形成する。銅を充填し銅配線パターン49A、49B、49Cとする。絶縁膜上と銅配線パターンの表面を覆う絶縁性拡散障壁膜49を形成する。熱処理により、銅配線パターンと絶縁性拡散障壁膜との界面に、金属元素の濃集領域49Dを形成する。金属元素の濃集領域では、金属膜を構成する金属元素の濃度が、銅配線パターン中よりも高い。

(もっと読む)

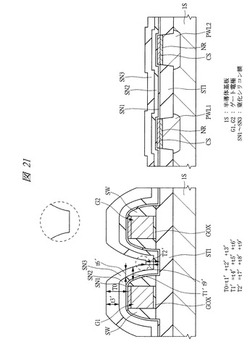

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】プリ・メタル層間絶縁膜の構成法としては、オゾンTEOSによる酸化シリコン膜の埋め込み特性の良好なCVD酸化シリコン系絶縁膜を成膜後、高温リフローさせて平坦化した後、CMPスクラッチ耐性が良好なプラズマTEOSによる酸化シリコン膜を積層し、更にCMPで平坦化することが考えられる。しかし、コンタクト・ホール形成プロセスにおいて、プリ・メタル層間絶縁膜中のクラックがコンタクト・ホール内に露出し、そこにバリア・メタルが入り込み、ショート不良の原因となることが明らかとなった。

【解決手段】本願発明はプリ・メタル工程において、エッチ・ストップ膜上にオゾンTEOS膜を形成後、一旦、ゲート構造上のエッチ・ストップ膜が露出するようにオゾンTEOS膜をエッチバックし、その後、残存オゾンTEOS膜上にプラズマTEOS膜を成膜し、このプラズマTEOS膜をCMPにより、平坦化するものである。

(もっと読む)

半導体装置

【課題】半導体装置の製造歩留まりを向上できる。

【解決手段】本発明の例に関わる半導体装置は、ウェハ1内に設けられる第1及び第2半導体チップエリア21,22と、第1及び第2半導体チップエリア21,22内の各々に設けられ、トランジスタが形成される第1素子領域51,52と、第1及び第2半導体チップ51,52間に設けられるダイシングエリア3Aと、ダイシングエリア3A内に設けられ、アライメントマークが形成されるアライメント領域35と、第1素子領域51,52とアライメント領域35との間に設けられ、ウェハ1表面に対して垂直方向に突出した凸部91,92を有する凸部形成領域71,72とを具備し、凸部91,92の上端は、ウェハ1表面より高い位置にあり、トランジスタのゲート電極12上端よりも低い位置にある。

(もっと読む)

半導体装置及びその製造方法

【課題】オフセットスペーサが除去されることを防止する。

【解決手段】第1導電型の半導体領域10x上に形成されたゲート絶縁膜13Aと、ゲート絶縁膜上に形成されたゲート電極15Aと、ゲート電極の側面上に形成されたオフセットスペーサ17Aと、ゲート電極の側面上にオフセットスペーサを介して形成された断面形状がL字状の内側サイドウォール19と、ゲート電極15A、オフセットスペーサ17A、内側サイドウォール19、及び半導体領域10xにおける内側サイドウォール19の外側方に位置する領域を覆うように形成された絶縁膜24とを備え、オフセットスペーサ17Aは、ゲート電極の側面上に形成された内側オフセットスペーサ16と、ゲート電極の側面上に内側オフセットスペーサ16を覆うように形成された外側オフセットスペーサ17とを有し、外側オフセットスペーサは、内側オフセットスペーサの上端及び外側面に接して形成されている。

(もっと読む)

配線基板製造装置、配線基板における絶縁膜の欠損修正判定方法、絶縁膜の欠損の修正を判定するプログラム、及び、当該プログラムを記録した記録媒体

【課題】配線基板の生産歩留りおよび生産性を向上する配線基板製造装置を提供する。

【解決手段】本発明に係る配線基板製造装置1における欠損検出部110は、絶縁膜における欠損を検出する。続いて、欠損数算出部120は、検出した絶縁膜における欠損のうち、交差部における欠損の数を算出する。そして、修正指示部130は、算出した欠損の数が0より多く、かつ、所定の閾値Th1未満である場合に、交差部における欠損を修正すべきであると判断する。

(もっと読む)

半導体装置およびその製造方法

【課題】 CSPと呼ばれる半導体装置において、配線相互間で銅イオンマイグレーションによるショートが発生しにくいようにし、且つ、配線用の下地金属層を良好に形成する。

【解決手段】 配線7の銅からなる上部金属層9の表面にはポリイミド系樹脂等からなる第2の保護膜10が設けられている。これにより、配線7相互間で銅イオンマイグレーションによるショートが発生しにくいようにすることができる。また、第1の保護膜5の平坦な上面に下地金属層8を形成しているので、配線7用の下地金属層8を良好に形成することができる。

(もっと読む)

半導体装置の製造方法

【課題】 CSPと呼ばれる半導体装置において、封止膜が配線の表面および柱状電極の外周面から剥離しにくいようにし、且つ、配線間でショートが発生しにくいようにする。

【解決手段】 銅からなる配線7の表面および銅からなる柱状電極10の外周面には針状構造の酸化銅膜11が設けられている。これにより、酸化銅膜11が無い場合と比較して、エポキシ系樹脂等からなる封止膜12が配線7の表面および柱状電極10の外周面から剥離しにくいようにすることができる。また、酸化銅膜11を形成する前に、配線7下以外の領域における導電性を有する変質層Cを完全に除去することにより、変質層Cに起因する配線7間でのショートの発生を確実に防止することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】露光条件が最適化される領域の配線と異なる方向の配線を必要とする領域の露光マージン不足を回避する。

【解決手段】半導体基板と、

前記半導体基板上に形成された層間絶縁膜と、

前記層間絶縁膜上の第1の領域において、第1のデザインルールを適用して形成された、特定方向に沿って走る、複数の第1の配線と、

前記層間絶縁膜上の第2の領域において、前記第1のデザインルールと同じ第2のデザインルールを適用して形成された、前記特定方向に沿って走る、複数の第2の配線と、

前記層間絶縁膜中に形成され、同一電位となるべき少なくとも2つの前記第2の配線を電気的に接続して所望の配線パターンを形成する、接続部材と、

を備える。

(もっと読む)

半導体装置の製造方法

【課題】 CSPと呼ばれる半導体装置において、柱状電極形成用メッキレジスト膜を剥離した際にレジスト残渣が発生しにくいようにし、且つ、工程数を少なくする。

【解決手段】 保護膜5の上面全体に、スパッタにより形成されたチタン膜およば銅膜からなる2層構造の配線形成用金属膜7aを形成する。次に、配線形成用金属膜7aの上面にネガ型のドライフィルムレジストからなる柱状電極形成用メッキレジスト膜23をパターン形成する。次に、配線形成用金属膜7aをメッキ電流路とした銅の電解メッキを行なうことにより、柱状電極形成用メッキレジスト膜23の開口部24内の配線形成用金属膜7aの上面に柱状電極8を形成する。次に、柱状電極形成用メッキレジスト膜23を剥離する。この場合、柱状電極形成用メッキレジスト膜23は平坦性の極めて高い配線形成用金属膜7aの上面に形成されているため、柱状電極形成用メッキレジスト膜23のレジスト残渣が発生しにくいようにすることができ、且つ、工程数を少なくすることができる。

(もっと読む)

201 - 220 / 613

[ Back to top ]