Fターム[5F033XX31]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 短絡防止 (613)

Fターム[5F033XX31]に分類される特許

141 - 160 / 613

半導体装置の製造方法

【課題】ゲート電極周辺の寄生容量を低減させることのできる半導体装置の製造方法を提供する。

【解決手段】半導体基板上にゲート絶縁膜を形成する。ゲート絶縁膜上に、その上部に絶縁膜を有するゲート電極を形成する。ゲート電極を形成した後、半導体基板とゲート電極を覆う第1シリコン酸化膜を形成する。第1シリコン酸化膜を形成した後、第1シリコン酸化膜を覆う第1シリコン窒化膜を形成する。第1シリコン窒化膜を形成した後、第1シリコン窒化膜を覆う第2シリコン酸化膜を形成する。第2シリコン酸化膜を形成した後、第2シリコン酸化膜をエッチングして、第2シリコン酸化膜をゲート電極の側壁部に残す。第2シリコン酸化膜をゲート電極の側壁部に残す工程の後、半導体基板に不純物拡散層を形成する。不純物拡散層を形成した後、第2シリコン酸化膜を除去する。第2シリコン酸化膜を除去した後、半導体基板を覆う第2シリコン窒化膜を形成する。

(もっと読む)

半導体集積回路装置

【課題】ダミービアが配置された半導体集積回路装置において、ダミービアに接続されたダミー配線の存在に起因する、設計容易性の低下や製造コストの増大といった問題を抑える。

【解決手段】半導体集積回路装置は、基板1と、基板1上に形成された3層以上の配線層2a〜2cとを有する。配線層2a,2bの間にダミービア11が形成されており、配線層2bにダミービア11と接続されたダミー配線12が形成されている。ダミー配線12は、スタックビア構造20の配線層2bに形成された中間配線24よりも、面積が小さい。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート配線が保護膜に覆われた構造において、保護膜に発生するクラックがゲート配線に到達することを防止することにより、ゲート−エミッタ間のショート不良を防止する。

【解決手段】第1保護膜25が表面電極17およびゲート金属配線18の間に配置されると共に、ゲート金属配線18を覆っている。また、第2保護膜26が第1保護膜25の上に形成されている。この場合、第2保護膜26は、第1保護膜25のうちの少なくともはんだ29に覆われる部分の上に形成されている。これにより、はんだ29実装前に引っかき傷等によって第2保護膜26にクラック31が発生したとしても、当該クラック31の進展を第1保護膜25と第2保護膜26との境界面で阻止することができる。

(もっと読む)

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】積層構造を有する柱状の複数のメモリセル間のショート発生を防止した不揮発性半導体記憶装置の製造方法を提供すること。

【解決手段】本発明は、マトリクス状に配置された柱状の複数のメモリセルMCを形成する工程と、直線上に並んだ一群のメモリセルの一方の底面に各々接触し、互いに平行なワードライン47a,47c,47eを形成する工程と、直線上に並んだ一群のメモリセルの他方の底面に各々接触し、互いに平行であり、かつワードラインと同一平面視で交差するビットライン56b,56dを形成する工程とを含み、ワードラインを形成する工程では、複数のメモリセルのうち同じワードラインまたはビットラインに接触する一群のメモリセルの端部に位置する端部メモリセルMCe1,MCe3と所定間隔を隔てて配置され、メモリセルMCと同じ積層構造を有するダミーメモリセルDMC1,DMC2を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート配線が保護膜に覆われた構造において、保護膜に発生するクラックがゲート配線に到達することを防止することにより、ゲート−エミッタ間のショート不良を防止する。

【解決手段】第1保護膜25が表面電極17およびゲート金属配線18の間に配置されると共に、ゲート金属配線18を覆っている。また、第2保護膜26が第1保護膜25の上に形成されている。この場合、第2保護膜26は、第1保護膜25のうちの少なくともはんだ29に覆われる部分の上に形成されている。これにより、はんだ29実装前に引っかき傷等によって第2保護膜26にクラック31が発生したとしても、当該クラック31の進展を第1保護膜25と第2保護膜26との境界面で阻止することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】プログラム後の誤読み出しを抑制でき、高い信頼性を備える半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板1上のチャンネル領域に形成されたゲート酸化膜3と、前記ゲート酸化膜3上に形成されたゲート電極4と、前記チャンネル領域の少なくとも一部に形成されたシリサイド層2と、を有し、前記シリサイド層2は、前記チャンネル領域のうち前記ゲート電極4の全体を除く領域の少なくとも一部を被覆する。

(もっと読む)

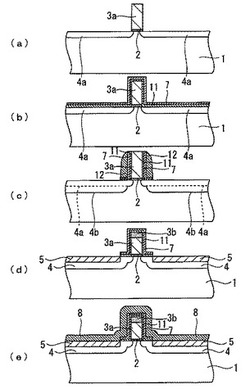

半導体装置の製造方法

【課題】ハードマスク膜による焦点深度のマージンの低下及びアライメントマークの視認性の低下を防ぎ、且つ、セルフアラインドビアの形成を可能とすることにより、配線同士のショートによる歩留まりの低下を防止すると共に、配線同士の絶縁性を高め、その信頼性を向上させるようにする。

【解決手段】半導体装置の製造方法は、基板10の上に、少なくとも1層の絶縁膜を含む層間絶縁膜12を形成し、層間絶縁膜12の上部に第1のマスク膜16を埋め込むように形成し、層間絶縁膜12及び第1のマスク膜16の上に第2のマスク膜17を形成し、第2のマスク膜17を用いて、層間絶縁膜12にビアホール19を形成し、第1のマスク膜16を用いて、層間絶縁膜12に配線溝20を形成し、ビアホール19及び配線溝20に導電性材料を埋め込むことにより、ビア及び配線を形成する。

(もっと読む)

カーボンナノチューブ配線及びその製造方法

【課題】カーボンナノチューブを有するプラグ配線において良好な電気的接続を得ることができるカーボンナノチューブ配線及びその製造方法を提供する。

【解決手段】第1配線層12上に層間絶縁膜13が形成され、層間絶縁膜13上に第2配線層14が形成されている。第1配線層12と第2配線層14との間の層間絶縁膜13内にはコンタクト孔15が形成される。コンタクト孔15内には、一端が第1配線層12に接続され、他端が第2配線層14に接続された複数のカーボンナノチューブ16が形成されている。さらに、層間絶縁膜13と第2配線層14との間にはストッパ膜17が形成され、ストッパ膜17の一部は複数のカーボンナノチューブ16の前記他端間に充填されている。

(もっと読む)

半導体装置の製造方法

【課題】 広範囲にわたって全導電性領域に、断切れ及び上層配線層との間のリーク電流の発生のない、均一な膜厚の銅配線層を形成することが可能な半導体装置の製造方法を提供すること。

【解決手段】 ガラス基板上に薄膜トランジスタ及び配線を有する半導体装置を製造する方法において、ガラス基板上に下地絶縁層を形成する工程と、前記下地絶縁層上に下地バリア層を形成する工程と、前記下地バリア層上にシード層を形成する工程と、前記シード層を前記配線に対応する形状にパターニングしてシード層パターンを形成する工程と、前記シード層パターンの表面に銅配線層を無電解めっき法で形成する工程と、前記銅配線層マスクとして前記下地バリア層をパターニングする工程と、前記銅配線層を被覆するように絶縁層を形成する工程とを備えたことを特徴する半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】従来の半導体装置は、通常のコンタクトとシェアードコンタクトとを同時に形成することが難しくなり、接合リーク不良やコンタクト抵抗の上昇が発生する等の課題があった。

【解決手段】ロジックSRAM部のゲート配線6の側壁に形成するサイドウォール9と、拡散層11の表面に形成するシリサイド層13とゲート配線6のシリサイド層15とを電気的に接続するドープトポリシリコン18と、ドープトポリシリコン18と第1層アルミ配線とを電気的に接続するWプラグ26と、ロジックSRAM部の拡散層11の表面のシリサイド層と第1層アルミ配線とを電気的に接続するWプラグ25とを備えるものである。

(もっと読む)

半導体装置及びその製造方法

【課題】層間絶縁膜の膜強度を十分に確保する。

【解決手段】第1の配線層絶縁膜と、第1の配線層絶縁膜に埋め込み形成されている複数の第1の銅配線8と、第1の銅配線8上及び第1の配線層絶縁膜上に形成されている層間絶縁膜(第2の低誘電率膜10)と、を有する。層間絶縁膜上に形成されている第2の配線層絶縁膜と、第2の配線層絶縁膜に埋め込み形成されている複数の第2の銅配線16と、を有する。第1、第2の配線層絶縁膜は、第1、第2の低誘電率膜(第1の低誘電率膜4、第3の低誘電率膜11)を含む。層間絶縁膜は、第1及び第2の配線層絶縁膜よりも高強度である。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】ソース/ドレイン領域のPN接合部とコンタクト間のリーク電流を抑制する。

【解決手段】半導体基板(1)と、半導体基板(1)に形成されたSTI(Shallow Trench Isolation)構造(2)と、半導体基板(1)に形成され、STI構造(2)に隣接する拡散領域(12)と、層間絶縁膜(15)を貫通して拡散領域(12)とSTI構造(2)とに到達する接続コンタクト(20)と、拡散領域(12)の側面と拡散領域(12)の下の半導体基板(1)の側面に形成され、接続コンタクト(20)と拡散領域(12)の側面とを電気的に絶縁し、かつ、接続コンタクト(20)と半導体基板(1)の側面とを電気的に絶縁する酸化膜(19)とを具備する半導体装置を構成する。その半導体装置では、STI素子分離とソース/ドレイン領域のPN接合部分の間のみに選択的に絶縁膜(酸化膜)を形成している。

(もっと読む)

銅の選択的かつ清浄なエッチングのための集束イオンビームプロセス

集積回路編集のための銅の集束イオンビームエッチング用のエッチング促進剤はイオンビームによる隣接する誘電体の損失を防ぎ、隣接面上のスパッタされ再堆積した銅を非導電性にして電気的短絡を回避する。促進剤は分子中にN−N結合を有し、約70〜220℃の沸点を有し、ヒドラジン及び水の溶液と、ヒドラジン誘導体と、メチル、エチル、プロピル及びブチルから選択された2つの炭化水素基によって飽和したニトロソアミン誘導体と、ニトロソアミン関連化合物と、四酸化窒素とを含み、好適にはヒドラジン一水和物(HMH)、ヒドロキシエチルヒドラジン(HEH)、CEH、BocMH、BocMEH、NDMA、NDEA、NMEA、NMPA、NEPA、NDPA、NMBA、NEBA、NPYR、NPIP、NMOR及びカルムスチン単独、又は四酸化窒素との組合せである。促進剤は高アスペクト比(深さ)の孔の銅をエッチングするのに有効である。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】配線の設計自由度が高く、ゲート電極及びソース/ドレイン領域に接続されるコンタクト部の形成に問題が生じ難く、微細化プロセスに適した半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、(a)基体21上にゲート電極31を形成し、基体にソース/ドレイン領域37及びチャネル形成領域35を形成し、ソース/ドレイン領域37上にゲート電極31の頂面と同一平面内に頂面を有する第1層間絶縁層41を形成した後、(b)第1層間絶縁層41に溝状の第1コンタクト部43を形成し、(c)全面に第2層間絶縁層51を形成した後、(d)第1コンタクト部43の上の第2層間絶縁層51の部分に孔状の第2コンタクト部53を形成し、その後、(e)第2層間絶縁層51上に、第2コンタクト部53と接続された配線61を形成する各工程から成る。

(もっと読む)

半導体装置とその製造方法

【課題】縦型トランジスタにおいて、柱状半導体層上のコンタクトと柱状半導体層の周囲に形成されるゲート電極のショートの抑制。

【解決手段】上方に平面状半導体層及び該平面状半導体層上の柱状半導体層が形成された基板に対して、柱状半導体層の上部に第2のドレイン/ソース領域を形成し、コンタクトストッパー膜を成膜し、コンタクト層間膜を成膜し、第2のドレイン/ソース領域上にコンタクトを形成し、ここでコンタクトの形成は、コンタクトのパターンを形成し、コンタクトのパターンを用いてコンタクト層間膜をコンタクトストッパー膜までエッチングすることにより、コンタクト用のコンタクト孔を形成し、コンタクト用のコンタクト孔の底部に残存するコンタクトストッパー膜をエッチングにより除去することを含み、コンタクト用のコンタクト孔の底面の基板への投影面は、柱状半導体層の上面及び側面に形成されたコンタクトストッパー膜の基板への投影形状の外周内に位置する。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体ウエハ上に形成された第1の保護膜上にポリイミド系樹脂等からなる第2の保護膜を形成するとき、半導体ウエハが反りにくいようにする。

【解決手段】 所定の相隣接する2本の配線7の接続パッド部7b間に形成された5本の引き回し線部7cおよびその両側における相隣接する2つの接続パッド部7bの周辺部を含む第1の保護膜5の上面に、スクリーン印刷法やインクジェット法等により、ポリイミド系樹脂等からなる第2の保護膜10を形成する。この場合、当該5本の引き回し線部7cの互いに平行とされた部分がエレクトロマイグレーションに起因するショートが発生しやすい領域であるので、この領域のみを第2の保護膜10で覆えば、当該領域でエレクトロマイグレーションに起因するショートが発生しにくいようにすることができる。この結果、第2の保護膜10の形成領域を可及的に小さくすることができ、これにより半導体ウエハ21が反りにくいようにすることができる。

(もっと読む)

構造体および構造体を形成する方法

【課題】 サブリソグラフィ・ピッチの構造体とリソグラフィ・ピッチの構造体との相互接続を形成する。

【解決手段】 サブリソグラフィ・ピッチを有する複数の導電線をリソグラフィでパターン形成し、複数の導電線の縦方向から45度より小さい角度の線に沿って切断することができる。代わって、ホモポリマーと混合した共重合体を陥凹エリア内に入れて自己整合し、一定幅領域内にサブリソグラフィ・ピッチを有し、台形領域で隣接線間にリソグラフィ寸法を有する複数の導電線を形成することができる。さらに代わって、サブリソグラフィ・ピッチを有する第1の複数の導電線と、リソグラフィ・ピッチを有する第2の複数の導電線は、同じレベルでまたは異なるレベルで形成することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の再配線層において配線を狭ピッチ化して隣接する配線間距離が著しく近接しても、配線間でイオンマイグレーションを効果的に抑制する。

【解決手段】一方の主面11aに半導体デバイスおよび電極11cが設けられた半導体基板11と、一方の主面11aの上に形成された層間絶縁層12と、層間絶縁層12上において個々の配線パターンに沿って複数形成されたポリイミドからなる樹脂パターン部13と、樹脂パターン部13の上にそれぞれ形成された再配線層14と、再配線層14の上を封止する封止絶縁層15とを有し、樹脂パターン部13の側面13aが、配線パターンの長手方向に垂直な断面において凹凸状とされている。

(もっと読む)

半導体装置の製造方法

【課題】

微細化したMOSトランジスタを含む半導体装置において、リーク/ショートの可能性を抑制する。

【解決手段】

半導体装置の製造方法は、活性領域上に、ゲート絶縁膜とシリコン膜とを形成し、シリコン膜上方にゲート電極用レジストパターンを形成し、レジストパターンをマスクとして、シリコン膜を厚さの途中までエッチングしてレジストパターン下方に凸部を残し、レジストパターンを除去した後シリコン膜を覆うダミー膜を形成し、ダミー膜を異方性エッチングして、凸部の側壁にダミー膜を残存させつつ、平坦面上のダミー膜を除去し、ダミー膜をマスクとして、シリコン膜の残りの厚さをエッチングしてゲート電極を形成し、ゲート電極両側の半導体基板に、ソース/ドレイン領域を形成し、シリコン領域にシリサイドを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置において、配線間距離が近接してもイオンマイグレーションを防止し、大幅に遅延化させる。

【解決手段】一端12aが半導体基板11の電極11cと導通され、他端にランド部13が設けられた再配線層12と、ランド部13の下面13bにおいて半導体基板11の一方の主面11aとの間に形成された絶縁樹脂ポスト部14と、一方の主面11aを覆い、かつランド部13の少なくとも一部が露呈されるように設けられた封止絶縁膜15とを有する半導体装置10において、再配線層12は、一方の主面11aから所定の距離をおいて一方の主面11aに平行に延在される配線部12bを有し、ランド部13の径が配線部12bの幅wよりも大きく、配線部12bは、その長手方向に垂直な断面において周囲が全周にわたって、連続体からなる同一の前記封止絶縁膜によって覆われている。

(もっと読む)

141 - 160 / 613

[ Back to top ]