Fターム[5F033XX31]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 短絡防止 (613)

Fターム[5F033XX31]に分類される特許

81 - 100 / 613

タングステンスパッタリングターゲットおよびその製造方法

【課題】基板上に成膜したW膜の膜厚面内均一性を向上させることが可能であり、さらにはパーティクルの発生を減少させることが可能なWスパッタリングターゲットおよびその製造方法を提供する。

【解決手段】Wスパッタリングターゲットは、スパッタリングされる面のX線回折により得られた結晶面(110)のピークの半値幅が0.35以下であることを特徴とする。また、本発明の高純度Wスパッタリングターゲットの製造方法は、高純度W粉末を加圧焼結後、得られた焼結体をターゲット形状に加工後、ロータリー研磨およびポリッシングの少なくとも1種の研磨を施し、さらにエッチングおよび逆スパッタリングの少なくとも1種の研磨を施すことにより仕上げ加工することを特徴とする。

(もっと読む)

半導体装置、その製造方法、および半導体装置を含む半導体パッケージ

【課題】装置特性の低下を防止するとともに、半導体基板と貫通電極の短絡を防止する半導体装置を提供する。

【解決手段】第1面と、第1面と対向してトレンチが形成された第2面とを有する基板と、基板内に形成されたビアホールを充填し、ビアホールの内壁から順にビアホール絶縁膜、障壁膜、および導電性接続部を有してなる貫通ビアと、第2面上に形成されて貫通ビアの一部領域を露出する開口部を有する絶縁膜と、トレンチ内に埋め込まれ、貫通ビアと電気的に接続される再配線と、を有し、絶縁膜は導電性接続部の一部領域と重複する。

(もっと読む)

半導体集積回路

【課題】例えばクラック発生などに起因する大量生産段階での低歩留りという問題を防止できる半導体集積回路を提供する。

【解決手段】パッドメタルの下に回路を有する半導体集積回路において、パッド開口部分のパッドメタルの少なくとも下全面に、互いに同一の電位を有する配線メタルを形成し、当該配線メタルの電位を上記パッドメタルと異なる電位に設定した。また、上記配線メタル、及び上記配線メタル以外の電位を有する別の配線メタルは、上記パッドメタルよりも下層に形成される。さらに、上記半導体集積回路の複数のパッドにおいて、バッド開口部分のパッドメタルの少なくとも下全面に形成された複数の配線メタルは互いに同一の電位に設定される。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】周辺回路における回路動作の遅延を低減できる不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板11上に所定間隔を空けて形成され、ゲート絶縁膜1、浮遊ゲート電極2、ゲート間絶縁膜3、及び制御ゲート電極4をそれぞれ有する複数のメモリセルMCと、メモリセルMCの浮遊ゲート電極2の側面、ゲート間絶縁膜3の側面、及び制御ゲート電極4の側面に形成され、空隙を有する側壁絶縁膜18Bと、基板11上に形成され、ゲート絶縁膜1、第1ゲート電極2、ゲート間絶縁膜3、及び制御ゲート電極4を有する周辺トランジスタPTと、周辺トランジスタPTの第1ゲート電極2の側面、ゲート間絶縁膜3の側面、及び制御ゲート電極4の側面に形成され、空隙19Aを有する側壁絶縁膜18Aとを備える。基板11上の最も低い位置にある空隙19Aの上端は、ゲート間絶縁膜3より基板11上の低い位置にある。

(もっと読む)

半導体装置、回路基板及び電子機器

【課題】信頼性の高い半導体装置及びその製造方法、回路基板並びに電子機器を提供することにある。

【解決手段】電極114は集積回路112に電気的に接続されている。半導体基板110の電極114が形成された面に、電極114を避けて樹脂層118が形成されている。配線122は、電極114に電気的に接続されており、樹脂層118の側面121と上面120の境目に形成された第1の部分150と、第1の部分150に接続されて樹脂層118の上面120に形成された第2の部分152と、を有する。第1の部分150は第2の部分152よりも広い幅で形成されている。外部端子124が配線122に電気的に接続されている。

(もっと読む)

半導体素子の製造方法

【課題】タングステン層の膜残りの発生を抑制する。

【解決手段】半導体基板1、コンタクトホール3を備えた絶縁膜2、絶縁膜2の表面およびコンタクトホール3の表面を被覆する被覆層4、並びに、コンタクトホール3を埋込むタングステン(W)層5を有するウエハに対し、ウエハを冷却せずに、W層5を被覆層4が露出しない範囲で高速でドライエッチングする工程と、ウエハを冷却せずに、W層5を被覆層4が露出しない範囲で、低速でドライエッチングする工程と、ウエハを冷却しつつ、被覆層4が露出するまで、W層5を低速でドライエッチングする工程と、ウエハを冷却しつつ、コンタクトホール3内のW層5を絶縁層2の高さまで低速でドライエッチングする工程と、を有する半導体素子の製造方法。

(もっと読む)

半導体装置、半導体装置の製造方法およびデータ処理システム

【課題】本発明はコンタクト開口をエッチングにより形成した場合にその下に位置する埋込絶縁膜がエッチングされないようにした構造の提供を目的とする。

【解決手段】本発明は、半導体基板と、半導体基板の主面に形成され活性領域を横断して素子分離領域まで延在するトレンチと、トレンチの下部側に形成された埋込型ゲート電極と、活性領域において埋込型ゲート電極の上方のトレンチ内を充填し、かつ、素子分離領域において埋込型ゲート電極の上方のトレンチ内を完全には充填せずにトレンチの内側面に接して配置されるサイドウォールを構成するキャップ絶縁膜と、素子分離領域においてサイドウォールの内側のトレンチを埋めて埋込型ゲート電極に接続形成されたパッドコンタクトプラグと、パッドコンタクトプラグおよびキャップ絶縁膜上を覆う層間膜と、パッドコンタクトプラグに接続するゲートコンタクトプラグとを具備してなる。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

半導体装置

【課題】配線の引き出し性が向上されているとともに、配線間の短絡などの電気的問題が生じるおそれが抑制されており、かつ、配線が形成される領域の省スペース化が図られた半導体装置を提供する。

【解決手段】半導体装置1が備える基板4上の所定の層内に、第1の配線3が複数本並べられて設けられている。各第1の配線3は、それらの並べられた方向に沿って一方の側から他方の側へ向かうに連れて長く延ばされて形成されているか、あるいは短く縮められて形成されている。それとともに、各第1の配線3は、隣接するそれぞれの一端部3aが並べられた方向と直交する方向において互いにずれた位置に配置されている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の配線間の容量低減を実現するとともに、ミスアライメント・ビアを対策する。

【解決手段】配線上及び配線間のスペース領域に絶縁膜74を形成し、隣接配線間隔が狭い配線の上面を露出するスルーホールの周辺領域の絶縁膜74をリザーバーとして残して、周辺領域以外の絶縁膜74を除去し、絶縁膜74が除去された配線間のスペース領域に空隙を残しつつ、配線上に絶縁膜77を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 アンダーフィル材を用いなくとも、柱状電極と半田端子との接合強度不足や、信頼性の低下を抑制する。

【解決手段】 半導体装置は、半導体基板と、半導体基板上に設けられた複数の配線と、複数の配線上にそれぞれ接続された複数の半田端子と、複数の配線の少なくとも一部を覆う樹脂層と、を備えている。樹脂層上には、少なくとも半田端子の周囲を覆うオーバーコート膜が被膜され、隣接する半田端子間のオーバーコート膜の高さは、半田端子の高さよりも低い。

(もっと読む)

半導体装置の製造方法

【課題】メタルゲートプロセスにおけるプリメタル層間絶縁膜の平坦性を向上できるようにする。

【解決手段】まず、半導体基板1の上に、ゲート絶縁膜3を介在させてゲート電極4を形成する。その後、半導体基板1にゲート電極4をマスクとしてソース・ドレイン領域を形成する。続いて、ゲート電極4を覆うように半導体基板1上の全面に第1の酸化シリコン膜10を形成する。その後、ゲート電極4をストップ膜とするCMP法により、第1の酸化シリコン膜10を平坦化する。続いて、ゲート電極4を含む第1の酸化シリコン膜10の上に、第2の酸化シリコン膜11を形成する。その後、ゲート電極4をストップ膜とするCMP法により、第2の酸化シリコン膜10を平坦化する。さらに、ゲート電極4を含む第2の酸化シリコン膜10の上に、第3の酸化シリコン膜12を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】封止膜の材料を容易に選定することができる半導体装置を提供する。

【解決手段】半導体基板11上に複数の接続端子12が形成された半導体デバイスウェハ10と、前記半導体デバイスウェハ10の表面を覆うとともに前記接続端子12を露出させる開口14aが設けられた第1絶縁膜14と、前記第1絶縁膜14上に形成され一端面が前記接続端子12と接続された複数の再配線30と、前記再配線30の他端面上に形成された複数の柱状電極21と、前記再配線30の側面を被覆する第2絶縁膜15と、前記再配線30及び前記第2絶縁膜15を封止するとともに前記柱状電極21の表面を露出させる封止膜22と、を備えることを特徴とする半導体装置1Bである。

(もっと読む)

半導体装置の製造方法

【課題】隣接する活性領域の間で横方向に成長するシリコン膜が連結されることを防ぎつつ、活性領域上に十分な厚みのシリコン膜を形成可能とした半導体装置の製造方法を提供する。

【解決手段】ゲート電極6aを挟んだ両側の活性領域5上に第1のシリコン膜12aを選択的にエピタキシャル成長させる工程と、複数のワード配線層WLの各間に第1のシリコン膜12aを覆うのに十分な厚みでマスク絶縁膜を埋め込んだ後、このマスク絶縁膜を第1のシリコン膜12aの表面が露出するまでエッチングにより除去する工程と、第1のシリコン膜12a上に第2のシリコン膜12bを選択的にエピタキシャル成長させる工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】接続不良の発生を抑制することのできる、信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、所定ピッチで所定の幅の素子領域が形成された半導体基板と、半導体基板上に積層された層間絶縁膜と、層間絶縁膜の上面から半導体基板の素子領域にかけて設けられ素子領域に接続される第1コンタクトとを備える。第1コンタクトは、素子領域上の層間絶縁膜に形成された素子領域の幅よりも大きい径を有するコンタクトホールと、コンタクトホールの底部に設けられ、素子領域に達する開口を有するスペーサ膜と、スペーサ膜の開口を介して素子領域に接続されるようにコンタクトホール内に埋め込まれたコンタクトプラグとを有する。

(もっと読む)

半導体装置、パターンレイアウト作成方法および露光マスク

【課題】 高集積化に有効な複数の配線パターンを含む配線パターン群を備えた半導体装置を提供すること。

【解決手段】 同一の配線用途のN(N≧3)本の配線パターンを含む配線パターン群を含む。N本の配線パターンの各々は別の層の配線郡内の配線パターンと電気的に接続するための接続領域を含む。N本の配線パターンは、配線パターンN1と、配線パターンN1の長手方向と異なる一方向に配置された二つ以上の配線パターンNi(i≧2)を含む。二つ以上の配線パターンNiはiの値が大きいほど配線パターンN1から離れた位置に配置され、二つ以上の配線パターンNiは少なくとも一つ以上のパターンNp(2≦p<N)と少なくとも一つ以上の配線パターンNq(p<q≦N)を含む。少なくとも一つ以上の配線パターンNpはpの値が大きいほど長手方向の寸法が長く、少なくとも一つ以上の配線パターンNqは、qの値が大きいほど、長手方向の寸法が短い。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクト孔に埋め込まれる金属プラグの材料が層間絶縁膜に染み出すのを防止できる半導体装置を提供する。

【解決手段】隣り合う2つのメモリセル1のサイドウォール間の不純物拡散領域に電気的接続されるコンタクトプラグ40が、層間絶縁膜18を貫通して設けられている。コンタクト孔41の側壁は、層間絶縁膜18より緻密なシール膜42で覆われている。コンタクトプラグ40は、シール膜42の表面およびコンタクト孔41の底面部を覆うように形成されたバリアメタル膜43と、バリアメタル膜43に包囲された状態でコンタクト孔41内に埋め込まれた金属プラグ44とを含む。

(もっと読む)

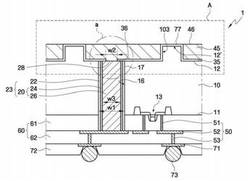

トレンチゲートMISデバイスの構造及び製造方法

【課題】より単純に製造でき、かつ平坦なトポロジを得ることができ、更にトレンチの上部曲がり部における降伏電圧の問題が解消されたトレンチゲートMISデバイスを提供すること。

【解決手段】トランジスタセルを含む活性領域と、トランジスタセルを含まないゲート金属領域と、ゲート金属層とを含み、半導体チップの表面のパターンに、活性領域からゲート金属領域に至るトレンチが形成されており、このトレンチが絶縁材料の層で裏打ちされた壁部を有し、導電性ゲート材料がトレンチ内に設けられており、導電性ゲート材料の上面が半導体チップの上面より下側に位置し、非導電層が活性領域及びゲート金属領域の上に位置し、ゲート金属領域におけるトレンチの一部の上側の非導電層に開口が形成されており、ゲート金属がトレンチ内の接触領域のゲート材料と接触するように、開口が前記ゲート金属で満たされているトレンチゲートMISデバイス。

(もっと読む)

半導体装置、電子装置、及び半導体装置の製造方法

【課題】第1インダクタと第2インダクタを構成する金属材料のマイグレーションに起因して第1インダクタと第2インダクタの絶縁が確保できなくなることを、抑制する。

【解決手段】半導体チップ100は配線基板200の第1面上に実装されており、多層配線層を有している。第1インダクタ112は多層配線層に形成されており、巻き軸方向が配線基板200と水平方向を向いている。第2インダクタ122は多層配線層に形成されており、巻き軸方向が配線基板200と水平方向を向いている。第2インダクタ122は第1インダクタ112に対向している。封止樹脂400は、配線基板200の少なくとも第1面と、半導体チップ100とを封止している。溝500は、封止樹脂400と多層配線層の界面のうち、少なくとも第1インダクタ112と第2インダクタ122の間に位置している部分の全域に形成されている。

(もっと読む)

液晶表示装置

【課題】ソース配線とゲート配線とが製造工程中の静電気によるショートを防止すること

が可能な液晶表示装置の素子構造を提供することを目的とする。

【解決手段】ソース配線が第1の半導体層、第2の半導体層、及び導電層によって構成さ

れる。そして、ソース配線とゲート配線の交差部において、ソース配線の端部の導電層を

除去して、半導体層がはみ出した形状とする。なお、ゲート配線、第1の半導体層、第2

の半導体層、及び導電層の材料はTFTを形成するために用いた材料と同一の材料からな

る。

(もっと読む)

81 - 100 / 613

[ Back to top ]