Fターム[5F033XX31]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 短絡防止 (613)

Fターム[5F033XX31]に分類される特許

61 - 80 / 613

表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

半導体装置

【課題】高い耐電圧特性、および耐リーク特性を有する配線構造を備える半導体装置、およびその製造方法を提供する。

【解決手段】本発明の実施の形態による半導体装置は、半導体素子が設けられた半導体基板と、前記半導体基板上に形成された、上下層の導電部材を電気的に接続する接続部材と、前記接続部材と同じ層に形成された第1の絶縁膜と、前記接続部材の上面の一部と接する第1の領域、および前記第1の領域上に位置し、前記第1の領域よりも幅の広い第2の領域を含む配線と、前記第1の絶縁膜上に、前記配線の前記第1の領域の側面の上側から少なくとも一部、および前記第2の領域の底面に接して形成された第2の絶縁膜と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極同士の間の突合わせ部を挟むように形成されたコンタクトプラグ同士が、当該突合わせ部の絶縁膜内に形成されたボイドを介してショートすることを防ぐ。

【解決手段】ゲート電極G2およびG5間の突合わせ部において対向するサイドウォールSW上には、ライナー絶縁膜6と層間絶縁膜7が形成されている。サイドウォールSW同士の間において、サイドウォールSWの側壁にそれぞれ形成されたライナー絶縁膜6を接触させてサイドウォールSW間を閉塞させることにより、層間絶縁膜7とライナー絶縁膜6の内部にボイドが発生することを防ぐ。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】コンタクトとアクティブエリアとの間のショートマージンを確保できる半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、半導体基板と、前記半導体基板の上層部分に形成され、前記上層部分を第1方向に延びる複数本のアクティブエリアに区画する複数本の素子分離絶縁体と、前記アクティブエリアに接続されたコンタクトと、を備える。そして、各前記アクティブエリアの上面のうち、前記第1方向における一部の領域には、前記第1方向に対して直交する第2方向において前記アクティブエリアの全体にわたって凹部が形成されている。前記第1方向において、隣り合う前記アクティブエリアにそれぞれ接続された2本の前記コンタクトの位置は相互に異なる。前記コンタクトは前記凹部の側面に接し、底面には接していない。

(もっと読む)

半導体素子及びその製造方法

【課題】絶縁膜を貫通するコンタクトプラグの抵抗を改善させられる半導体素子及びその製造方法を提供する。

【解決手段】半導体基板上に形成された第1層間絶縁膜と、前記第1層間絶縁膜を貫通して形成されたコンタクトホールと、前記コンタクトホールの内部に形成されたコンタクトプラグと、前記コンタクトホール内で前記コンタクトプラグの上部側壁を部分的に覆うスペーサと、を含む。

(もっと読む)

表面被覆方法、並びに半導体装置、及び実装回路基板

【課題】配線及び絶縁膜へダメージを与えることなく、絶縁膜上の導電性の不純物によるめっきの異常成長を抑制することができる表面被覆方法、並びに該方法を用いて製造される半導体装置、及び実装回路基板の提供。

【解決手段】水溶性樹脂、有機溶剤、及び水を含有する表面被覆材料を、表面に露出した絶縁膜及び表面に露出したパターニングされた金属配線を有する積層体の少なくとも前記絶縁膜の表面を覆うように塗布し、前記絶縁膜の表面に被膜を形成する表面被覆方法である。

(もっと読む)

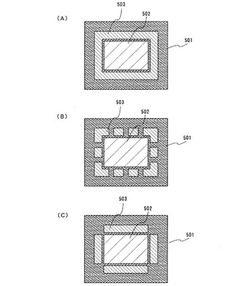

半導体装置

【課題】半導体装置の小型化、特に、狭ピッチ化に対する技術を提供する。

【解決手段】半導体チップ1C上に設けられたパッド2と、プローブ領域10Aおよび接続領域10Bのパッド2上に開口部11を有し、半導体チップ1C上に設けられたパッシベーション膜3と、接続領域10Bのパッド2上に開口部12を有し、パッド2上およびパッシベーション膜3上に設けられたパッシベーション膜5と、パッド2と電気的に接続され、接続領域10B上およびパッシベーション膜5上に設けられた再配線7とを備える。接続領域10Bより半導体チップ1Cの外周部側に設けられたプローブ領域10Aのパッド2にプローブ痕100が存在し、接続領域10Bから半導体チップ1Cの中央部側に延びて再配線7が存在している。

(もっと読む)

半導体装置

【課題】隣接するビット線同士の短絡が抑制されており、かつ層間絶縁膜が平坦に研磨された半導体装置を提供する。

【解決手段】磁気抵抗素子MRDが複数配置されたメモリセル領域と、平面視においてメモリセル領域の周囲に配置された周辺回路領域とを備える。磁気抵抗素子MRDは、磁化固定層と磁化自由層とトンネル絶縁層とを含んでいる。磁気抵抗素子MRDの上方には、主表面に沿った方向に向けて延びる複数の第1の配線BLを有している。上記周辺回路領域には、第1の配線BLと同一レイヤにより構成される第2の配線BL2と平面視において重なるように、磁化自由層と同一材質の層、トンネル絶縁層と同一材質の層および磁化固定層と同一材質の層が積層された積層構造DMMが配置されている。積層構造DMMは、周辺回路領域にて平面視において隣接する1対の第2の配線BL2の両方と重ならない。

(もっと読む)

半導体装置の製造方法及び製造装置

【課題】半導体装置のエッチングを精度良く行い、再生率を低減させる

【解決手段】基板にトランジスタを形成し、トランジスタを覆うように第1層間絶縁膜22を形成する。さらに、第1層間絶縁膜22の上方に形成したレジスト膜27を用いて第1層間絶縁膜22をエッチングし、トランジスタのソース/ドレイン領域に到達するコンタクトホール31を形成する。この際、レジスト膜27の開口部27Aの半径rと、開口部27Aが設計位置からずれている位置ずれ量ΔXとを測定し、コンタクトホール31に必要な半径Rxと、コンタクトホール31を形成可能な限界距離Sとから、r+ΔX−S<ES<r−Rxを満たす半径差ESを決定し、半径差ESからエッチング条件を決定する。

(もっと読む)

半導体装置の製造方法

【課題】層間絶縁膜に空隙が発生することを抑制し、半導体装置の製造における歩留まりの向上を図ることができる。

【解決手段】半導体装置100の製造方法は、一面に互いに隣接する少なくとも2つの凸部90を有する半導体基板10の一面上に、2つの凸部90間における膜厚が2つの凸部90のうち少なくとも一方の高さの1.2倍以上となるように絶縁膜50を形成する工程と、絶縁膜50上に、絶縁膜50よりも硬い絶縁膜60を形成する工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の絶縁膜内へのCu溶出を抑制すると共に、配線間におけるショートの発生を抑止し、信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】MCMの半導体装置において、ベアチップ1,2間を接続する配線4aをCu材料13を用いてダマシン法で形成する際に、上面が有機絶縁膜11の表面から上方に突出し、上面の配線幅方向の中央部位が端部位よりも厚い配線4aを形成し、配線4aのCu材料13上のみにメタルキャップ膜5を形成する。

(もっと読む)

ダミーパターンの設計方法

【課題】チップ面積の増大を抑えつつ半導体集積回路装置の金属配線パターンPTの寄生抵抗に起因する動作不良を抑制可能なダミーパターンの設計方法を提供する。

【解決手段】ビアPTがマトリクス状に配置されたデータ、第1配線PTを含む第1配線層データ、第1配線PTに対して重なり領域を有する第2配線PTを含む第2配線層データ、第2配線PTに対して第1値だけオーバーサイズしたデータ、第1配線PTからオーバーサイズPTとの重なり領域を消去した図形データ、図形を第2値だけアンダーサイズし、第2値以下の図形が消去されたデータ、アンダーサイズPTを第2値だけオーバーサイズして元のサイズに戻した第1ダミーPTデータ、複数のビアPTから第1ダミーPTに対応する領域内のビアPTを抽出したデータ、第2配線PTと第1ダミーPTとを合成した第2配線層データ、上記第2配線層の隙間を埋める第2ダミーPTデータを各々作成する。

(もっと読む)

埋め込みビットラインを備えた半導体装置の製造方法

【課題】埋め込みビットラインの抵抗を減少させることができる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板201に活性領域203を分離するトレンチ202をエッチングにより形成するステップと、活性領域203の何れか1つの側壁の一部を露出させた開口部207を有する絶縁膜205を形成するステップと、絶縁膜205上にトレンチ202を部分的に埋め込み、開口部207を埋め込むようにシリコン膜パターン208Aを形成するステップと、シリコン膜パターン208A上に金属膜209を形成するステップと、金属膜209及びシリコン膜パターン208Aを反応させて、埋め込みビットラインとなる金属シリサイド膜211を形成するステップとを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】DRAMセルとロジックを混載したLSIデバイスにおけるアスペクト比の大きいコンタクト構造において、素子分離絶縁膜および不純物拡散層のオーバエッチングを抑制して、接合リークを抑制することを課題とする。

【解決手段】周辺MOSトランジスタを覆う第1エッチングストッパ層121と、DRAMメモリセルのキャパシタ部上層に第2エッチングストッパ層122が形成され、周辺MOSトランジスタの不純物拡散層113は、第1、第2エッチングストッパ層121、122を貫通する電極層131により、上記キャパシタ部上層に形成された金属配線層と接続され、不純物拡散層113の少なくとも一つは素子分離絶縁膜102の境界上に電極層131を接続し、素子分離絶縁膜102上に形成された電極層131の底部の不純物拡散層113表面からの深さ寸法は、不純物拡散層113の接合深さ寸法もより短く形成されたものである。

(もっと読む)

絶縁膜形成方法、及び絶縁膜形成装置

【課題】成膜温度が180℃以下で形成される絶縁膜の絶縁性を高めることの可能な絶縁膜の形成方法及び該絶縁膜を形成する成膜装置を提供する。

【解決手段】

マスフローコントローラMFC1から原料タンクTKにArガスを供給することによって押し出されたZr(BH4)4ガスと、マイクロ波プラズマ源PLで励起することによって活性状態にされた酸素原子を含むガスとを、シャワープレート36に設けられた複数の孔から別々に基板S表面の空間に供給する。この際、活性状態にされた酸素原子を含むガスの供給を連続的に行う間に、Zr(BH4)4昇華ガスの供給を間欠的に複数回行ってもよい。これにより、ジルコニウムと、ホウ素と、酸素とを含む絶縁膜であるZrBO膜を基板Sの表面及び該基板Sの有する貫通孔の内面に形成する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート配線が保護膜に覆われた構造において、保護膜に発生するクラックがゲート配線に到達することを防止することにより、ゲート−エミッタ間のショート不良を防止する。

【解決手段】半導体素子の第1領域と接続される表面電極17、および通路12の少なくとも一部に、半導体素子の第2領域と接続される第1金属配線18を形成する。その後、はんだ29が実装されない通路12bに形成する第1保護膜25の高さが、はんだ29が実装される通路12aに形成する第1保護膜25の高さよりも高くなるように、注入器32を用いて第1保護膜25を通路12に塗布する。続いて、表面電極17および第1保護膜25の上に金属層27、28を形成してはんだ29が実装されない通路12bに形成した第1保護膜25が金属層27、28から露出するように、はんだ29が実装されない通路12bに形成した第1保護膜25の一部および金属層27、28を切削する。

(もっと読む)

半導体装置

【課題】半導体装置を高集積化する。

【解決手段】本実施形態の半導体装置は、絶縁体内に設けられ、半導体集積回路を含んでいる半導体基板70と、絶縁体の開口部POPを介してその上面が露出するパッド90と、パッド90下方において半導体基板70のキャパシタ領域91内に設けられる複数のキャパシタ1と、を具備し、キャパシタ1は、所定の被覆率を満たすように、パッド90下方のキャパシタ領域91内に設けられ、キャパシタ1の2つの電極にそれぞれ接続されるコンタクト18A,18Gは、開口部POPと上下に重ならない位置に設けられている。

(もっと読む)

機能性膜の形成方法、積層構造体、多層配線基板、アクティブマトリクス基板及び画像表示装置、並びに図面製造装置、インクジェット装置、積層構造体製造装置

【課題】インクジェット法により微細なパターンでショートさせることなく機能性膜を形成することができる機能性膜の形成方法を提供する。

【解決手段】被印刷面上に、低表面エネルギー領域を隔てて隣接する高表面エネルギー領域231,241を有する表面において、高表面エネルギー領域231,241の形状及び機能液の着弾範囲に基づいて、高表面エネルギー領域231(241)に機能液を供給する際に該機能液が高表面エネルギー領域231(241)のみに触れるための滴下許容範囲231A(241A)を決定し、ついで滴下許容範囲231A(241A)内の任意の位置を高表面エネルギー領域231(241)に対する機能液の滴下位置231C(241C)として決定し、高表面エネルギー領域231(241)の滴下位置231C(241C)にインクジェット法を用いて選択的に機能液を供給して所定パターンの機能性膜を形成する。

(もっと読む)

半導体装置、その製造方法、および半導体装置を含む半導体パッケージ

【課題】装置特性の低下を防止するとともに、半導体基板と貫通電極の短絡を防止する半導体装置を提供する。

【解決手段】第1面と、第1面と対向してトレンチが形成された第2面とを有する基板と、基板内に形成されたビアホールを充填し、ビアホールの内壁から順にビアホール絶縁膜、障壁膜、および導電性接続部を有してなる貫通ビアと、第2面上に形成されて貫通ビアの一部領域を露出する開口部を有する絶縁膜と、トレンチ内に埋め込まれ、貫通ビアと電気的に接続される再配線と、を有し、絶縁膜は導電性接続部の一部領域と重複する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体層の表面から貫通孔絶縁層が後退した場合においても、半導体層と貫通電極との絶縁性を確保する。

【解決手段】貫通孔6には、貫通孔絶縁層7、8を介して貫通電極9が埋め込まれ、貫通孔絶縁層7、8は、半導体層3の表面から後退するようにして形成され、半導体層3と貫通電極9との間には、貫通孔絶縁層7、8の後退部分の対応した凹部10が形成され、貫通電極9の側壁には、凹部10に埋め込まれたサイドウォール絶縁膜12が形成される。

(もっと読む)

61 - 80 / 613

[ Back to top ]