Fターム[5F033XX32]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 遮光 (95)

Fターム[5F033XX32]に分類される特許

41 - 60 / 95

電磁波検出素子の製造方法

【課題】電磁波検出素子の製造に際し、フォトダイオードなどの半導体層の下層に配置される層間絶縁膜の材料制約を緩和する。例えば、有機系材料からなる層間絶縁膜の配置を可能にする。

【解決手段】TFTアレイが形成された基板1の上に、TFTアレイを覆うように層間絶縁膜12を形成した後、PIN型のフォトダイオード層6の形成前に、フォトダイオード層6よりエッチング速度の遅いIZO膜14を形成し、フォトダイオード層6の一部を、IZO膜14が露出するまでドライエッチング処理により除去してパターニングした後、露出したIZO膜14をフォトリソグラフィー技術により除去してパターン化することにより下部電極14aを形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】生産性を向上することができ、凹部の計測を正確に行うことができる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置1は、第一絶縁膜11中に形成された平膜状の第一遮光膜12と、この第一遮光膜12の上部に設けられ、複数の凹部131が形成された第二絶縁膜13とを有する。遮光膜12は、平面視において、中心から外郭までの距離が2μm以上であり、遮光膜12上に第二絶縁膜13の複数の凹部131が位置する。

(もっと読む)

表示装置用基板、表示装置及び表示装置用基板の製造方法

【課題】表示装置用基板において十分な遮光性を有する多層配線構造を提供する。

【解決手段】画素電極と、これを駆動するためにゲート電極、ソース電極及びドレイン電極を備えた薄膜トランジスタと、各電極の層及び各電極を接続する配線の層で構成される多層配線とを形成した表示装置用基板であって、多層配線は、第1配線層6と、その上に配された第2配線層15と、両配線層6,15の間に配され且つ両配線層から層間絶縁膜7,9で絶縁された金属遮光層8とを含む。第1配線層6と第2配線層15は、層間絶縁膜7,9を貫通して形成されたコンタクトホールを介して互いに電気的に接続している。コンタクトホールは、その側壁に露出した金属遮光層8の端面を電気的に絶縁被覆するためにサイドウォール13aが形成されている。

(もっと読む)

半導体装置

【課題】横方向および斜め上方向からの光の進入を低減でき、特性の変動が抑制されたフローティングゲート電極を有する不揮発性メモリの半導体装置を提供する。

【解決手段】メモリセルの周囲に設けられた第1遮光壁50により画定された第1被遮光領域10Aと、メモリセルの周囲に設けられた第2遮光壁により画定された第2被遮光領域10A´と、第1遮光壁50に設けられた第1開孔52と、第2遮光壁に設けられ第1開孔52と対向して位置する第2開孔52´と、メモリセルと接続され、第1開孔52から第1被遮光領域10Aの外側に引き出された第1配線層24a,24b,24cと、メモリセルと接続され、第2開孔52´から第2被遮光領域10A´の外側に引き出された第2配線層24a´,24b´,24c´と、少なくとも、第1被遮光領域10Aと第2被遮光領域10A´とに挟まれた領域の上方に設けられた遮光膜と、を含む。

(もっと読む)

半導体装置

【課題】 横方向および斜め上方向からの光の進入を低減でき、特性の変動が抑制された半導体装置を提供する。

【解決手段】 本発明の半導体装置は、第1半導体素子120を含み、その周囲に設けられた第1遮光壁50により画定された第1被遮光領域10Aと、

第2半導体素子120´を含み、その周囲に設けられた第2遮光壁50´により画定され、前記第1被遮光領域10Aと隣り合う位置に設けられた第2被遮光領域10A´と、 前記第1遮光壁50に設けられた第1開孔52と、

前記第2遮光壁50´に設けられ前記第1開孔52と対向して位置する第2開孔52´と、

前記第1半導体素子120と接続され、前記第1開孔52から前記第1被遮光領域10Aの外側に引き出された第1配線層24と、

前記第2半導体素子120´と接続され、前記第2開孔52´から前記第2被遮光領域10A´の外側に引き出された第2配線層24´と、

少なくとも、前記第1被遮光領域10Aと前記第2被遮光領域10A´とに挟まれた領域の上方に設けられた遮光膜60と、を含む。

(もっと読む)

半導体装置の作製方法

【課題】材料や形成されたパターンが異なる複数の層が積層された構造の半導体装置において、CMP法による研磨処理やSOG膜成膜による平坦化処理を行わなくても平坦化でき、さらに基板材料を選ばず、簡便に平坦化を行う方法を提供することを課題とする

【解決手段】異なる層が複数積層されて形成された半導体装置において、絶縁膜に開口部を形成し、その開口部内に配線(電極)または半導体層を形成することにより、絶縁膜および配線(電極)または半導体層上に形成される絶縁膜に対してCMP法による研磨処理またはSOG膜の成膜による平坦化を行わなくても表面の平坦化を行うことができる。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】MONOS型不揮発性半導体記憶装置において、製造時にメモリセルを紫外線から保護する紫外線遮光膜を安定して形成できるようにする。

【解決手段】半導体基板1の上部にX方向に延びるビット線拡散層9と、半導体基板1の上にY方向に延びると共に電荷トラップ膜4及びゲート電極5からなるゲート構造体とを有する不揮発性半導体記憶装置に、ビット線拡散層3と接続される第1のコンタクト9が形成された第1の層間絶縁膜8と、該第1の層間絶縁膜8の上に形成された紫外線遮光膜10及び第2の層間絶縁膜11を貫通して下端部が第1のコンタクト9と接し且つ上端部が金属配線13と接続される第2のコンタクト12とを設ける構成とする。

(もっと読む)

半導体装置の製造方法

【課題】記憶情報のセキュリティ性の高い半導体装置を製造工程数の増加を抑えて製造することのできる技術を提供する。

【解決手段】半導体基板10の主面に細い配線M1aと太い配線M1bとを形成した後、高密度プラズマCVD法によりこれら配線M1a,M1bを覆う絶縁膜26を堆積し、さらに遮光膜27および下層絶縁膜28aを順次堆積する。続いて下層絶縁膜28aの表面をCMP法により研磨して太い配線M1bの上の遮光膜27を露出させ、さらに太い配線M1bの上の遮光膜27を研磨して除去した後、上層絶縁膜28bを堆積する。続いて太い配線M1bの上の絶縁膜26および上層絶縁膜28bに、太い配線M1bに達する接続孔29aを形成した後、接続孔29aの内部にプラグ31を埋め込む。

(もっと読む)

半導体装置

【課題】受光素子への不要な光の浸入を防止することで、半導体装置の特性ずれを防止することを主たる目的とする。

【解決手段】半導体基板2の表面には、ホトダイオードから成る複数の受光素子3が島状に形成されている。半導体基板1の表面には、受光素子3で変換された電気信号を増幅するためのトランジスタ素子(増幅素子)等から成る集積回路4が形成されている。半導体基板2の側面及び裏面全体は絶縁膜10で被覆されている。絶縁膜10上には、パッド電極6と電気的に接続された配線層11が形成されている。配線層11上には電極接続層12及びバンプ電極14が形成されている。各受光素子3は、垂直方向から見た場合にバンプ電極14の領域よりも内側に形成されている。

(もっと読む)

配線構造およびその製造方法

【課題】下層構造の影響を抑制して高精度にパターン形状管理を行うことができる配線構造およびその製造方法を提供すること。

【解決手段】基板1上の絶縁膜111に形成された配線パターン118と、基板1上の絶縁膜111における配線パターン118とは異なる領域に形成されて測定光が照射される測定用パターン119と、測定用パターン119の直下に形成された光透過抑制膜109とを備え、測定用パターン119は、配線パターン118と同一のパターンであり、光透過抑制膜109は、測定用パターン119を構成する絶縁膜111の材料の光透過率よりも小さい光透過率を有する材料からなることを特徴とする配線構造。

(もっと読む)

半導体装置およびその製造方法

【課題】紫外線から受けるダメージを抑制することができ、且つ、小型化にも対応することが可能な半導体装置およびその製造方法を提供すること。

【解決手段】本発明は、半導体基板10上に設けられたシリコン粒子36を含む第1絶縁膜40と、半導体基板10と第1絶縁膜40との間に設けられた電荷蓄積層14を含むONO膜からなる第2絶縁膜34と、第2絶縁膜34と第1絶縁膜40との間に設けられたゲート電極20と、ゲート電極20を挟むように半導体基板10内に設けられたビットライン22と、を具備する半導体装置およびその製造方法である。

(もっと読む)

半導体装置、電気光学装置および半導体装置の製造方法

【課題】下地絶縁層の下層側に支持基板と別の材料からなる層を形成する場合でも、支持基板と半導体基板との貼り合わせ技術を好適に適用することのできる半導体装置、電気光学装置、および半導体装置の製造方法を提供する。

【解決手段】液晶装置などといった電気光学装置の素子基板などとして用いられる半導体層10xでは、支持基板10dの上に下地絶縁層12が形成されているとともに、下地絶縁層12の表面に電界効果型トランジスタ10yが形成されている。支持基板10eにおいて、電界効果型トランジスタ10yのチャネル領域1xに対向する位置には凹部10eが形成され、この凹部10eには埋め込みゲート電極4xが形成されている。

(もっと読む)

薄膜トランジスタアレイ基板、その製造方法および液晶表示装置

【課題】TFTアレイ基板において、各配線間のクロストークを低減する。

【解決手段】TFTアレイ基板は、透明基板上に配置され、ゲート電極4aが分岐して延在するゲート配線1と、下部絶縁膜を介してゲート電極4aの上方を覆う半導体層3と、半導体層3を介してゲート電極4aの上側にそれぞれ一部が重なりかつゲート配線1とは交差しないようにそれぞれ別個に配置されたソース/ドレイン電極4b,4cと、ソース/ドレイン電極4b,4cを覆う上部絶縁膜と、この上部絶縁膜の上側においてゲート配線1と交差する方向に配置され、ソース電極4bに接続された上部ソース配線8と、ドレイン電極4cに電気的に接続された透明な画素電極11とを備え、少なくともゲート配線1と上部ソース配線8とが交差する交差部21では、ゲート配線1と上部ソース配線8との間に上記上部絶縁膜が配置されている。

(もっと読む)

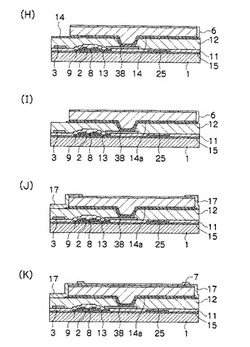

埋込配線の形成方法、表示装置用基板及び当該基板を有する表示装置

【課題】 埋込配線が形成される絶縁性基板の材料が耐熱性の高いものに限定されず、当該埋込配線の端子部の耐食性を向上でき、パターニングが少ない工程で且つ良好な膜厚精度で確実に行われる埋込配線の形成方法を提供する。

【解決手段】 絶縁性基板1の表面に形成したマスク17を用いて絶縁性基板1の表面を選択的に除去し、配線パターンに対応する平面形状を持つ溝18を形成する。マスク17を除去せずに絶縁性基板1の表面全体に金属ナノ粒子インクを塗布し、加熱により仮硬化させて金属ナノ粒子インク膜20を形成する。マスク17の剥離により膜20の当該マスク上にある部分を選択的に除去して溝18の内部に膜20を残す。加熱により溝18内の膜20を本硬化させ所望のゲート配線2を得る

(もっと読む)

半導体装置

【課題】 EPROMを搭載するICチップにおいて、データを消去するメモリ素子(書換え可能な)とデータを消去したくないメモリ素子(データ冗長用)を同時に有する半導体装置を提供する。

【解決手段】 特定のメモリ素子の上に紫外光線を反射、吸収する遮光物を形成する。このことによりデータ消去性を調整できるようなメモリ素子を形成できるようにする。また、遮光物に開口することで、より消去制御性のよりメモリ素子とすることができる。

(もっと読む)

半導体装置及びヒューズ素子の切断方法

【課題】信頼性を確保しつつヒューズ素子の配列ピッチを狭くすることが可能な半導体装置を提供する。

【解決手段】レーザビームの照射により切断可能な複数のヒューズ素子101〜105と、平面的に見て複数のヒューズ素子間に位置し、レーザビームを減衰可能な減衰部材140とを備える。減衰部材140は複数の柱状体によって構成されている。これにより、切断すべきヒューズ素子から半導体基板側へ漏れ出したレーザビームLは、複数の柱状体によって構成された減衰部材140によって吸収されるとともに、フレネル回折によって散乱する。これにより、このため、柱状体が過度のエネルギーを吸収することによって絶縁膜にクラックなどが生じることがなく、効率的にレーザビームを減衰させることが可能となる。

(もっと読む)

半導体装置

【課題】特に、横方向および斜め上方向からの光の進入を低減でき、特性の変動が抑制された半導体装置を提供する。

【解決手段】本発明の半導体装置は、半導体層に設けられた半導体素子と、

前記半導体素子の周囲に設けられた遮光壁50と、

前記半導体素子に電気的に接続された配線層26であって、前記遮光壁50の設けられていない開孔52から該遮光壁50の外側に延伸された配線層26と、を含み、

前記配線層26は、前記開孔52に位置している第1部分26Aと、該開孔52の外側に位置し、該配線層26の延伸方向と交差する分岐部28を有することで該開孔52の幅と同一以上の幅を有する第2部分26Bと、を含むパターンを有し、

前記分岐部28において、前記遮光壁50の外側を向いた面は、その表面に凸部を有する。

(もっと読む)

半導体装置

【課題】特に、横方向および斜め方向からの光の進入を低減でき、特性の変動が抑制された半導体装置を提供する。

【解決手段】本発明の半導体装置は、半導体層10に設けられた半導体素子と、

前記半導体素子の周囲に設けられた遮光壁50と、

前記半導体素子に電気的に接続された配線層26であって、前記遮光壁50の設けられていない開孔52から該遮光壁50の外側に延伸された配線層26と、を含み、

前記配線層26は、前記開孔52に位置している第1部分26Aと、該開孔の外側に位置し該第1部分26Aと比して大きい幅を有する第2部26B分と、を含むパターンを有し、

前記第2部分26Bの幅は、前記開孔52の幅と同一以上の幅である。

(もっと読む)

半導体装置

【課題】特に、横方向および斜め方向からの光の進入を低減でき、特性の変動が抑制された半導体装置を提供する。

【解決手段】本発明の半導体装置は、半導体層10に設けられた半導体素子と、

前記半導体素子の周囲に設けられた遮光壁50と、

前記半導体素子に電気的に接続された配線層26であって、前記遮光壁50の設けられていない開孔52から該遮光壁50の外側に延伸された配線層26と、を含み、

前記配線層26は、前記開孔52に位置している第1部分26Aと、該開孔の外側に位置し該第1部分26Aと比して大きい幅を有する第2部26B分と、を含むパターンを有し、

前記第2部分26Bの幅は、前記開孔52の幅と同一以上の幅である。

(もっと読む)

半導体装置及びその製造方法、並びに電子部品

【課題】ウエハレベルCSP化された半導体装置において、所定の入光面以外の面から光が入射することを抑制し、搭載された集積回路やデバイスなどが赤外〜紫外域の電磁波によって誤作動を生じないパッケージを実現するための構造を有する、半導体装置及び製造方法、並びにこの半導体装置を用いた電子部品を提供する。

【解決手段】本発明の半導体装置10は、一方の面に電極3を備える半導体からなる基板2、前記基板の一方の面に配された絶縁部4、前記基板の他方の面に配された第一保護部6、を少なくとも備えた構造体11を有する。また、半導体装置10は、前記構造体の側面部の一部又は全部を被覆する第二保護部7を有することにより構成され、前記第一保護部及び前記第二保護部は何れも、遮光性を有することを特徴とする。

(もっと読む)

41 - 60 / 95

[ Back to top ]