Fターム[5F038AC10]の内容

Fターム[5F038AC10]に分類される特許

221 - 232 / 232

集積回路とキャパシタンス素子とを備える電子装置

電子装置(ICD)は、集積回路(AIC)とキャパシタンス素子(PIC)とを備えている。集積回路(AIC)には、複数の回路接点対(CI)が設けられている。キャパシタンス素子(PIC)には、複数のキャパシタンス接点対(CC)が設けられている。キャパシタンス接点対(CC)の少なくとも一部のそれぞれの間にはキャパシタンスが存在する。複数のキャパシタンス接点対(CC)は、複数の回路接点対(CI)と対向する。キャパシタンス接点対(CC)の少なくとも一部は、回路接点対(CI)の少なくとも一部に対して、対ごとに電気的に結合される。  (もっと読む)

(もっと読む)

容量素子及びその製造方法及びこの容量素子を有する半導体装置及びその製造方法

【課題】誘電体に生じる電解集中を解消して容量素子を小型化可能とした容量素子及びその製造方法及びこの容量素子を有する半導体装置及びその製造方法を提供する。

【解決手段】一対の電極間に誘電体を設けて構成した容量素子、及びこの容量素子を有する半導体装置であって、誘電体が積層される電極の積層面に窒化チタン層を形成した容量素子、及びこの容量素子を有する半導体装置において、窒化チタン層の上面をイオン照射またはプラズマ処理した後に有機溶剤で洗浄して平滑化する。特に、有機溶剤はフッ化アンモン系有機溶剤とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 下部電極の上端近傍で酸化タンタル膜が薄膜化するのを防ぎ、この部分での下部電極と上部電極の間のリークを防ぐことができる半導体装置及びその製造方法を得る。

【解決手段】 本発明に係る半導体装置は、凹部を有するシリコン酸化膜と、凹部内に形成された下部電極と、下部電極の上端近傍に設けられたシリコン窒化膜と、下部電極を覆うように形成された酸化タンタル膜と、酸化タンタル膜上に形成された上部電極とを有する。

(もっと読む)

固体撮像装置

【課題】高精細化に伴って画素数が増えると、垂直信号線に接続される画素数が増え、信号処理回路のキャパシタへの負荷が増大するため、キャパシタとしてより大きい容量のものが必要になる。

【解決手段】画素アレイ部12の垂直画素列ごとに配されるS/H、CDS回路151のキャパシタC11,C12を、従来の平面型キャパシタに代えて、スタック/トレンチキャパシタを用いて形成することで、キャパシタC11,C12の平面的な占有面積を変えることなく、キャパシタC11,C12の容量値を増大可能とする。

(もっと読む)

半導体装置及びその製造方法

【課題】下部電極形成工程を別途設けることなく、少ない占有面積で大きな容量を持つMIMキャパシタを備えた半導体装置及びその製造方法を提供する。

【解決手段】MIMキャパシタ形成領域Aの第2の絶縁膜6には、Ta/TaNのようなバリア膜からなる下部電極12とAl2O3のような金属酸化膜からなる容量絶縁膜13とTiNのようなバリア膜からなる上部電極14とを有するMIMキャパシタ15が形成されている。一方、配線形成領域Bの第2の絶縁膜6には、上部に設けられた第2配線部W2と下部に設けられた第2プラグ部P2が一体化形成されたバリア膜8bと導電膜9bからなる第2層配線10bが形成されている。そして、MIMキャパシタ15の下部電極12と第2層配線10bのバリア膜8bは共通のバリア膜を用いて同時に形成されたものである。

(もっと読む)

デュアル・ダマシン構造におけるMIMキャパシタの構造および製作方法

【課題】MIM(金属−絶縁体−金属)キャパシタ(242/252)構造およびそれを形成する方法を提供すること。

【解決手段】第1パターン(216)および第2パターン(218)を有するデュアル・ダマシン・パターンで、半導体デバイス(200)の誘電体層(214)をパターニングする。第2パターン(218)は、第1パターン(216)よりも深い。第1パターン中の誘電体層(214)の上に導電層(226)を形成し、第1パターン(216)中のこの導電層の上に導電層を形成する。第2パターン(218)の導電層(226)の上に、誘電体層(232)、導電層(234)、誘電体層(236)、および導電層(238)を配設する。導電層(234)、誘電体層(232)、および導電層(226)が、第1のMIMキャパシタ(252)を形成する。導電層(238)、誘電体層(236)、および導電層(234)が、第1のMIMキャパシタ(252)に並列な第2のMIMキャパシタ(242)を形成する。  (もっと読む)

(もっと読む)

電子集積回路の製造方法及びそれによって得られる電子集積回路

基板(100)上に一時的な材料の部分(1)の形成を含む集積回路の製造方法であって、その基板の一部は吸収材料からなる集積回路の製造方法である。一時的な材料は、コバルト、ニッケル、チタン、タンタル、タングステン、モリブデン、ガリウム、インジウム、銀、金、鉄及び/又はクロムを含む。硬質部分(3、4)は、吸収材料からなる基板の部分に対向する一時的な材料(1)の部分の一側で基板と接触して形成される。前記回路は、一時的な材料が吸収材料からなる基板の部分に吸収される方法で加熱される。従って、実質的に材料が無い領域(V)は、一時的な材料(1)の部分の場所に形成される。その実質的に空の領域は、キャパシタの補強材の間に位置する誘電材料に置き換わることができる。  (もっと読む)

(もっと読む)

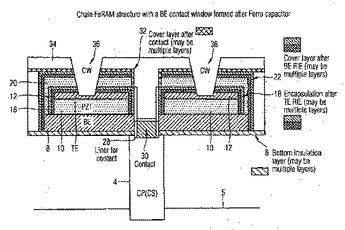

強誘電体コンデンサ装置におけるコンタクトプラグの酸化防止装置およびその方法

本発明は、強誘電体コンデンサ装置およびその製造方法にかかる。この製造方法は、基板を形成する工程と、この基板を貫通するようにコンタクトプラグを形成する工程とを含む。基板の上には電気絶縁層が形成され、この電気絶縁層上に第1の電極が形成される。さらに、第1の電極上には強誘電体層が形成され、強誘電体層上には第2の電極が形成される。第1の電極は、電気絶縁層を貫通して、プラグに電気接続されている。  (もっと読む)

(もっと読む)

金属・絶縁体・金属キャパシタ及びその製造方法

【課題】 銅相互接続技術と両立性があるMIM構造体及びその製造方法を提供する。

【解決手段】 MIMキャパシタのための方法及び構造体であり、この構造体は、半導体基板上に形成された層間誘電体層と、層間誘電体層内に形成され、上面が層間誘電体層の上面と同一平面にある銅製下部電極と、該下部電極の上面と直接接する導電性拡散障壁と、導電性拡散障壁の上面と直接接するMIM誘電体と、MIM誘電体の上面と直接接する上部電極とを備える電子デバイスを含む。銅の下部電極内に導電性拡散障壁を凹ませることができ、又は付加的な凹まされた導電性拡散障壁を設けることもできる。

(もっと読む)

基板上に多機能誘電体層を形成する方法

本発明は、多機能誘電体層を基板上、特に基板上に露出している金属配線系上に形成する方法に関する。本発明の目的は、銅による配線を形成するための多機能パッシベーション層を容易に形成する方法を提供するとともに、エレクトロマイグレーション、ストレスマイグレーション、および接着性を向上させる方法を提供することにある。本発明によれば、更なる金属層(5)を、露出した金属配線(3)の表面上に堆積することによって、本発明の目的は達せられる。この金属層は少なくともその一部が非導電性の金属酸化物に変換され、誘電体層となっている。  (もっと読む)

(もっと読む)

金属−絶縁物−金属キャパシタおよび配線構造

【課題】 金属−絶縁物−金属キャパシタおよび配線構造を提供する。

【解決手段】 ダマシン工程を利用してMIMキャパシタおよび配線構造を含む半導体装置を製造する。前記MIMキャパシタおよび配線構造は静電容量を増やしつつ同じ深さで形成する。

(もっと読む)

電子デバイス、アセンブリ、電子デバイスの製造方法

半導体基板は、共通の誘電層を有する垂直相互接続部および垂直キャパシタの両方を備えている。基板は、アセンブリを形成するために更なるデバイスと適切に組み合わせることができる。基板は、一方の面を第1のステップを含むエッチング処理で形成した後、基板の他方の面を第2のステップを含む処理で形成することができる。  (もっと読む)

(もっと読む)

221 - 232 / 232

[ Back to top ]