Fターム[5F038AC10]の内容

Fターム[5F038AC10]に分類される特許

21 - 40 / 232

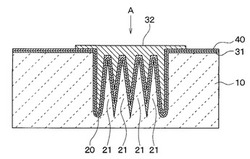

キャパシタ構造体およびその製造方法

【課題】シリコン基板に設けられた穴の内部に導電体と誘電体を配置することにより、キャパシタを構成してなるキャパシタ構造体において、穴をより深くしたり、穴の平面形状を複雑な形状とすることなく、導電体間の対向面積を増加させて容量値の増大が実現できるようにする。

【解決手段】穴20は、シリコン基板10の一方の主面に開口する有底穴であり、穴20の内部にはシリコン基板10よりなる突起21が設けられ、穴20の底面は、突起21による凹凸面とされており、穴20の内部では、穴20の底面および側面に、これらの面側から第1の導電体31、誘電体40、第2の導電体32が順次積層されているとともに、第1の導電体31および誘電体40は、突起21による凹凸面の形状を承継した層形状とされている。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板に設けられた穴に、絶縁体を介して2つの導電体を充填してなる電極部を有する半導体装置において、2つの導電体間の容量を大きくするのに適した構成を提供する。

【解決手段】半導体基板10の第1の領域1には、表面11に開口する複数個の有底穴20が設けられ、第2の領域2には貫通穴30が設けられ、有底穴20は貫通穴30よりも小さい穴幅を有する。絶縁体50を両導電体40、60で挟んでなる積層構造体が、有底穴20および貫通穴30に充填され、さらに、第1の領域1において複数個の有底穴20間にて連続して形成されており、第1の領域1は、当該積層構造体による容量形成部として構成される。有底穴60における各導電体40、60は、それぞれ貫通穴30における各導電体40、60に電気的に接続されて、半導体基板10の表裏両面11、12に取りだされている。

(もっと読む)

キャパシタ装置及びその製造方法

【課題】本発明は、大容量化及び小面積化の要請に応えつつ、電圧依存性の低いキャパシタ装置及びその製造方法を提供することを目的とする。

【解決手段】シリコン31、32からなる下部電極30上に、容量絶縁膜40と上部電極50が順次積層形成されたキャパシタ装置であって、

前記下部電極は、互いに導電極性の異なるN型領域20とP型領域10とが所定比率で混在配置されているとともに、前記N型領域の表面が前記P型領域の表面よりも窪んだ凹凸構造を有することを特徴とする。

(もっと読む)

半導体装置

【課題】補償容量素子を構成する容量絶縁膜が破壊されることのない半導体装置を提供する。

【解決手段】第1の電圧が供給される第1の電源端子29と、第2の電圧が供給される第2の電源端子23と、容量絶縁膜42と該容量絶縁膜42を挟んで形成される第1及び第2電極とを其々備えており、前記第1及び第2の電源端子間に直列に設けられる複数の補償容量素子4と、奇数番目の前記補償容量素子4と次の偶数番目の前記補償容量素子4とを各々接続する第1の配線層に形成された第1の容量接続配線と、偶数番目の前記補償容量素子4と次の奇数番目の前記補償容量素子4とを各々接続する第2の配線層に形成された第2の容量接続配線と、前記第1及び第2の容量接続配線のいずれか一方に隣接して設けられ、実質的に固定された電圧が供給されるシールド配線5と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】エッチング装置の経時変化や状態変化等によらずトレンチの深さのばらつきを低減することができる半導体装置の製造方法を得る。

【解決手段】まず、所望の深さよりも浅い深さを持つトレンチ16をSi基板10の主面に形成する。次に、トレンチ16の深さを測定する。トレンチ16の底面からSi基板10に酸素イオン18を注入する。この際に、測定したトレンチ16の深さと所望の深さの差に基づいて酸素イオン18の注入エネルギーを調整して、Si基板10の所望の深さに酸素イオン18が注入されるようにする。次に、熱処理を行って酸素イオン18を注入した位置にSiO2膜22を形成する。次に、SiO2膜22をエッチングストッパとして用いて、トレンチ16の底面からSi基板10を更にエッチングしてトレンチ24を形成する。その後、SiO2膜22を除去する。

(もっと読む)

半導体装置

【課題】低電位領域と高電位の配線が交差することの無い優れた耐圧性能を示す半導体装置を提供することを課題とする。

【解決手段】本発明の半導体装置は、ロジック回路(501)と、ロジック回路からの制御信号に従い低電位側パワー素子を駆動する低電位側駆動回路(502)と、ロジック回路からの制御信号がレベルシフト回路を介して入力され、高電位側パワー素子(506)を駆動する高電位側駆動回路(505)と、複数に重なったトレンチ分離領域により、前記高電位側パワー素子を含む高電位島を分離する多重トレンチ分離領域(508)と、を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子の平面形状を大きくせずに、その容量を大きくすることができ、かつ容量素子のリーク電流が増大することを抑制する。

【解決手段】下部電極410は、表層に、厚さが2nm以下の金属含有酸化層414を有している。金属含有酸化層414は、下部電極410の表面を酸化することにより形成されている。そして誘電膜420は、バルク状態において常温で出現する第1相と、バルク状態において第1相より高温で出現する第2相と、を含んでいる。第2相は第1相より比誘電率が高い。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】補償容量素子のキャパシタ構造に起因したリーク電流の増加を抑制するとともに、立体構造のキャパシタ構造を採用して、占有面積を削減した半導体装置を提供する。

【解決手段】メモリセル領域に形成されたクラウン型のキャパシタ21aと、周辺回路領域に形成されたコンケイブ型の補償容量素子10と、を有することを特徴とする半導体装置20を提供する。また、第1層間絶縁膜上にパッド47a,47bを形成する工程と、パッド47a,47b上に有底筒形状の下部電極66a,66bを形成する工程と、メモリセル領域の下部電極66aの内壁面及び外壁面と、周辺回路領域の下部電極66bの内壁面のみを誘電体膜67a,67bで覆う工程と、誘電体膜上に上部電極69a,69bを形成する工程と、を有することを特徴とする半導体装置20の製造方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】簡易な追加工程を設けることで、基板のベベル部から膜が剥離することを抑制する。半導体装置の製造歩留まりの低下を抑制すると共に、製造コストの増加を抑制する。

【解決手段】半導体基板上の全面に、1以上の膜を有する構造を形成した後、膜構造上にパターンを有する第1のマスクを形成する。ベベル部上の第1のマスクを覆うように第2のマスクを形成する。第1のマスク及び第2のマスクを用いて、膜構造をエッチングした後、残留した第1のマスク及び第2のマスクを除去する。

(もっと読む)

半導体装置およびその製造方法

【課題】高温熱処理をせずに形成可能、かつ、信頼性劣化が少なく、かつ、従来のトレンチキャパシタと同様に、安定した容量値の供給、及び、大容量化が可能な、半導体キャパシタ、及び、その製造方法を提供する。

【解決手段】半導体基板の表面にLOCOS法およびウェットエッチングを用いて台形状トレンチを設け、台形状トレンチ表面に下部電極層5を形成し、下部電極層の上に容量絶縁膜6と上部電極7を順次積層する。

(もっと読む)

キャパシタ、集積装置、高周波切替装置及び電子機器

【課題】能動素子で扱う信号の影響を抑制しつつ、十分な容量密度を得られるキャパシタ、集積装置、高周波切替装置及び電子機器を提供する。

【解決手段】絶縁層12と、絶縁層12の上に設けられた半導体層13と、半導体層13において、能動素子が形成されるアクティブ領域とは電気的に分離して設けられたダミーアクティブ領域20と、を有する基板10と、基板10におけるダミーアクティブ領域20の上に、互いに対向して配置された第1電極31及び第2電極32と、第1電極31と、第2電極32と、の間に設けられた第1誘電体部40と、を備える。

(もっと読む)

半導体装置

【課題】体格の増大が抑制された半導体装置を提供する。

【解決手段】絶縁分離トレンチによって半導体基板が複数の素子形成領域に区画され、各素子形成領域に少なくとも1つの電子素子が形成された半導体装置であって、半導体基板の厚さ方向に垂直な平面方向において、1本の絶縁分離トレンチを介して、2つの素子形成領域が互いに隣接するように、絶縁分離トレンチの平面方向に沿う形状が、格子状となっている。

(もっと読む)

半導体装置およびその製造方法

【課題】高容量・高精度なMIM静電容量素子を少ない工程で製造する技術を提供する。

【解決手段】第1層間絶縁膜17上に静電容量素子の下部電極21と第2層配線22とを同時に形成した後、第1層間絶縁膜17上に堆積した第2層間絶縁膜24に開口部34を形成する。次に、開口部34内を含む第2層間絶縁膜24上に順次堆積した容量絶縁膜27、第2金属膜および保護金属膜29を順次堆積し、第2層間絶縁膜24上の保護金属膜29、第2金属膜および容量絶縁膜27をCMP法で研磨・除去することによって、開口部34内に容量絶縁膜27、第2金属膜からなる上部電極28および保護金属膜29を残す。

(もっと読む)

半導体装置

【課題】ノイズが高周波である場合においても、多層配線層を介してデジタル回路とアナログ回路の間でノイズが伝播することを抑制する。

【解決手段】回路分離領域40は第1回路領域20と第2回路領域30の間に位置している。回路分離領域40には複数の第1導体及び複数の第1ビアが設けられている。複数の第1導体は、電源ライン110より下層に設けられ、電源ライン110に対向しており、かつ繰り返し配置されている。複数の第1ビアは多層配線層の中に、複数の第1導体それぞれごとに設けられており、各第1導体を電源ライン110に接続している。

(もっと読む)

半導体装置,半導体装置の製造方法及び半導体製造装置

【課題】膜厚を増大させることなく,キャパシタ容量の低下を抑制する。

【解決手段】キャパシタ100を有する半導体装置において,キャパシタ100は,下部電極112と上部電極16と,下部電極112と上部電極16とに挟まれた絶縁膜14とを備えている。下部電極112は窒化チタンからなり,当該下部電極112の絶縁膜14側の表面がさらに窒化されて窒素リッチ層118が形成されている。下部電極112の表面に窒素リッチ層118が形成されることにより,下部電極112の上面の酸化が効果的に抑制される。特に,DRAMにおいては,キャパシタの容量が大きくなるため,その効果が大きい。またキャパシタ内部のリーク電流も減る。

(もっと読む)

半導体装置

【課題】MIM構造の容量素子を有する半導体装置において、容量素子の信頼性を向上させることのできる技術を提供する。

【解決手段】下部電極DEと、容量絶縁膜CELと、上部電極UEとからなる容量素子において、下部電極DEを、半導体基板1の主面上の絶縁膜に形成された電極溝17aの内部に埋め込まれた金属膜によって構成し、上部電極UEを、TiN膜(下層金属膜)22と、TiN膜(下層金属膜)22上に形成されたTi膜(キャップ金属膜)23との積層膜によって構成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】少ない工数の追加でロジック回路とメタル容量素子とを混載し、かつ、ロジック動作特性の劣化を生じることがない半導体装置の製造方法を提供する。

【解決手段】基板11上に第1層間絶縁膜13を形成し、第1層間絶縁膜13に導電体柱14A、14Bを形成する。第1層間絶縁膜13の上面に溝配線部絶縁膜15を形成する。導電体柱14Bの上方において溝配線部絶縁膜15を除去して容量用開口部151を形成し、第1層間絶縁膜15の上面に容量素子用絶縁膜16を形成する。導電体柱14Aの上方において容量素子用絶縁膜16および第1層間絶縁膜15を除去して配線用溝152を形成する。容量用開口部151および配線用溝152に金属体17A、17Bを埋め込む。容量用開口部152の金属体17Aを容量素子の上部電極とし、配線溝152の金属体17Bをロジック配線とする。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】キャパシタ素子の配置面積低減が可能な半導体記憶装置を提供する。

【解決手段】メモリセル領域5及び周辺回路領域6を複数の素子形成領域に分離し、半導体基板11表面より上に上面を有する素子分離絶縁膜17と、メモリセル領域5の素子領域7上に、順に、トンネル絶縁膜13a、第1下層電極層15a、第1電極間絶縁膜19a、及び第1上層電極層25aとを有するメモリセル及び選択ゲートトランジスタ41、43と、周辺回路領域6の素子形成領域上に、上端に凹部18が加工された第2下層電極層15b、この凹凸面及び素子分離絶縁膜17上に配設され、第1電極間絶縁膜19aと同じ膜厚の第2電極間絶縁膜19b、及び第2電極間絶縁膜19b上に第2下層電極層15bに対応した凹凸の下面の第2上層電極層25bを有し、凹部18の底面が第1下層電極層15aの上面と同じ高さであるキャパシタ素子45とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化によってキャパシタが小型化された場合であっても、キャパシタの実効的なキャパシタ容量の低下を抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】下部電極に形成した凹部開口の内周面を含む下部電極上に誘電膜を形成し、凹部開口内を含む誘電膜上に下部電極と対向する上部電極を形成する。さらに、下部電極を、第1導電膜と、絶縁膜と、不純物がドープされた低抵抗の第2導電膜とを順次積層して形成し、第1導電膜と第2導電膜とを接続する。

(もっと読む)

高い絶縁破壊電圧の埋め込まれたMIMキャパシタ構造体

高い絶縁破壊電圧の埋め込まれた複数のキャパシタに関連する方法及び装置が提供される。半導体装置は、絶縁体(209)に埋め込まれたゲート材料(204)、複数の金属接触部(213)及び複数のキャパシタ(C1−C4)を含み得る。複数のキャパシタは、下部電極(217)、下部電極の表面を覆うように形成される誘電体(219)及び誘電体に形成される上部電極(221b、c)を含み得る。さらに、複数の接触部は、複数のキャパシタの下部電極の各々をゲート材料に接続し得る。複数のキャパシタは、ゲート材料を介して直列に接続され得る。  (もっと読む)

(もっと読む)

21 - 40 / 232

[ Back to top ]