Fターム[5F038AR13]の内容

Fターム[5F038AR13]に分類される特許

121 - 140 / 220

バッテリと、該バッテリの電極内の活性種の濃度変化によって抵抗が制御される可変抵抗器とを有する固体構造

現在、IC設計での利用が想定される、集積抵抗器の多くのバリエーションがある。しかしながら、電気回路に応じて、しばしば、一定の値を示さず、可変制御可能な値を示す抵抗器が必要となる。本発明は、固体可変抵抗器に関する。また本発明は、そのような可変抵抗器を有する電子装置に関する。さらに、本発明は、固体可変抵抗器を製造する方法に関する。  (もっと読む)

(もっと読む)

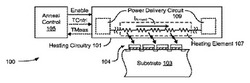

オペレーション上の退化を反転する内蔵型加熱回路を有する集積回路

集積回路デバイス(100)は、使用に応じた性能劣化(例えば、フラッシュメモリセルのトンネル酸化物内で蓄積された欠陥、又は、電荷蓄積層内でトラップされた電荷)を示す構造(104)と、構造に近接して配置され、劣化を反転する温度に構造を加熱する加熱回路(101)とを備える。メモリデバイスのワード線又はビット線を加熱素子(107)として使用する。 (もっと読む)

電極構造体及びその製造方法、並びに電子デバイス

【課題】 ナノサイズの間隙部を有する電極構造体を、生産性よく、確実に製造することのできる電極構造体の製造方法、及びその製造方法によって作製される電極構造体並びに電子デバイスを提供すること。

【解決手段】 まず、絶縁性基板1に細線2を配置する。次に、絶縁性基板1の、細線2の側方に位置する領域を被覆するように、導電性微粒子3からなる導電性微粒子層4を配置する。導電性微粒子層4は、単粒子層であるのが望ましく、例えばラングミュア−ブロジェット(LB)法を用いて形成する。次に、電極5および6を形成する領域に存在する導電性微粒子3に電子線を照射して、導電性微粒子3同士を融着させ、細線2を間に挟んで対向する2つの電極5および6を形成する。次に、細線2を除去して、2つの電極5および6間に間隙部7を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】従来の半導体装置においては、受動素子を形成するための工程を追加する必要がある。

【解決手段】半導体装置1は、半導体基板10、FET(電界効果トランジスタ)20、コンタクトプラグ30、抵抗素子40(特定部材)、および配線50を備えている。FET20には、コンタクトプラグ30が接続されている。このコンタクトプラグ30と同一の層(配線層60の最下層)中に、抵抗素子40が設けられている。コンタクトプラグ30および抵抗素子40は、同一の材料によって形成されている。抵抗素子40の上面の一部に、配線50が接続されている。

(もっと読む)

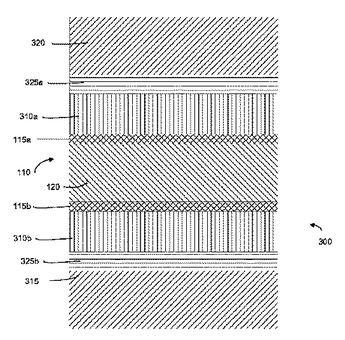

封入された金属抵抗器

この方法は、構造内に形成された抵抗層を隣接層からの汚染種から保護する構造を形成するための半導体構造および方法を実現する。汚染種の拡散に抵抗する材料中に抵抗層を封入することにより、該構造を製造するのに必要な処理中に抵抗材料を保護することが可能である。  (もっと読む)

(もっと読む)

磁気検出装置

【課題】 磁気抵抗効果を利用した可変抵抗素子と参照抵抗素子との中間から出力を得る磁気検出装置において、抵抗値のバランスを、簡単で且つ広い範囲で調整できるようにする。

【解決手段】 直列に接続された抵抗調整部3と参照抵抗素子4と可変抵抗素子5および、可変抵抗素子6と参照抵抗素子と抵抗調整部とに電圧が印加される。所定の大きさの磁界が与えられると、可変抵抗素子5,6の抵抗値が変化し、検出出力14,15の電位が変化する。抵抗調整部3,8には、複数の抵抗素子が並列に接続された並列部が設けられ、この並列部が直列に接続されている。並列に接続されている一方の抵抗素子を非導通にすることにより、抵抗調整部の抵抗値を変えることができる。

(もっと読む)

磁気検出装置およびその製造方法

【課題】 磁気抵抗効果素子を使用した磁気検出装置において、多層構造の膜の抵抗値をダメージを与えることなく、簡単に調整できるようにする。

【解決手段】 基板の表面に、磁気抵抗効果素子層11と参照抵抗層21とが直列に接続されて形成され、参照抵抗層22と磁気抵抗効果素子層12とが直列に接続されて形成されている。そして、電力供給層31と接地層32との間に電圧が印加される。第1の出力導電層33と参照抵抗層21とが平行に延び、その一部が接続層35で導通されている。また、参照抵抗層22と第2の出力導電層34とが平行に延び、その一部が接続層36で導通されている。接続層35と36の位置を可変することにより、参照抵抗層21,22の抵抗値を調整できる。

(もっと読む)

トランジスタの駆動回路

【課題】 トランジスタを駆動する回路において、トランジスタがターンオフする過渡期間に存在するサージ電圧とターンオフ損失の間のトレードオフ関係を打破すること。

【解決手段】 駆動回路10は、トランジスタ20のゲート電極Gに電気的に接続している可変抵抗体R12を備えている。その可変抵抗体R12の電流経路の幅が、トランジスタ20のドレイン・ソース間電圧Vdsに応じて伸縮する空乏層によって調整されることを特徴としている。

(もっと読む)

半導体装置

【課題】専用電源を必要としないガードリングを提供する。

【解決手段】ノイズから保護すべき回路の電源に、ガードリングをも接続する。位置関係が特定されているノイズ源に対して、保護すべき回路を挟んだ反対側に、ガードリングの接続コンタクトを設ける。

(もっと読む)

ラダー抵抗の調整パターン構造及びこれを有する電子部品

【課題】粗調整と微調整の2つの工程を要することなく、1つの工程によるトリミング作業により、高精度な抵抗値調整が可能なラダー抵抗の調整パターン構造及びこれを有する電子部品を提供する。

【解決手段】基板上に形成された第1及び第2の柱部と、第1及び第2の柱部の間に並列に形成された複数のラダー部と、を有し、少なくとも第2の柱部が他の部分と比べて比抵抗の小さい材料で形成されたことを特徴とするラダー抵抗の調整パターン構造とする。

(もっと読む)

半導体装置

【課題】薄膜抵抗である第1の多結晶シリコン膜3と配線用のコンタクト部が接続される第2の多結晶シリコン膜6の接触抵抗およびそのバラツキの増大を防止する。

【解決手段】半導体基板1上に第1の絶縁膜2を介して形成された第1の多結晶シリコン膜3と、第1の多結晶シリコン膜3上に形成され、開口窓5を有する第2の絶縁膜4と、第2の絶縁膜4上および開口部5に形成された第2の多結晶シリコン膜6と、第2の多結晶シリコン膜6および第2の絶縁膜4の上に形成された層間絶縁膜8と、層間絶縁膜8に形成され、第2の多結晶シリコン膜6と電気的に接続するプラグ層10とを備え、第1の多結晶シリコン膜3は、第2の多結晶シリコン膜6より膜厚が薄い高抵抗体であることを特徴とする。

(もっと読む)

半導体装置

【課題】本発明の目的は、配線の、幅の異なる部分の連結部分に生じる応力を減らすことにある。

【解決手段】半導体装置は、半導体チップ10と、幅の異なる第1、第2の配線の連結部分34と、連結部分34とオーバーラップする位置に形成されたパッド40と、パッド40上に形成されてなるバンプ44と、連結部分34とパッド40との間に位置して連結部分34の全体を覆うように形成されてなる緩衝層50と、連結部分34と緩衝層50との間及び緩衝層50とパッド40との間に、それぞれ形成されてなる無機絶縁層60,62と、を含む。緩衝層50は、樹脂を除く材料であって、無機絶縁層60,62よりも柔らかい材料から形成されてなる。

(もっと読む)

抵抗分割回路を具える集積回路およびその製造方法

本発明は、シリコン本体(60)を設ける工程を具える抵抗分割回路を製造する方法を提供し、シリコン本体は、シリコン本体自体から伸びる複数の対向する一対の中間タップを有する。各中間タップは、比較的幅広のシリコンプラットフォーム(62)を支持する薄いシリコンステム(61)を具える。シリサイド化保護(silicidation protection:SIPROT)層(S)は、シリコン本体(60)および中間タップの上方に堆積され、その後、シリコンプラットフォーム(62)が露出するようパターニングされる。シリサイド化プロセスは、比較的低抵抗のコンタクトパッドを形成するために、プラットフォームをシリサイド化するよう行われる。  (もっと読む)

(もっと読む)

磁気センサ及びその製造方法

【課題】 従来に比べて、適切に、中点電位のずれを小さくすることが可能な磁気センサ及びその製造方法を提供することを目的としている。

【解決手段】 固定抵抗素子9の側方に導体35が接続されている。前記導体35は、複数の分割経路片35a〜35dと、各分割経路片間を繋ぐ共通経路片35eとで構成され、前記共通経路片35eの一部分35e1を切断することで前記導体35の素子長手方向(図示Y方向)への電流経路長を変化させて抵抗調整を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置及びその製造技術、特に、抵抗素子を有する半導体装置に適用し、半導体装置の小型化を実現することが可能な技術を提供する。

【解決手段】第1の絶縁膜3上に、島状の半導体層4及び前記半導体層を囲む第2の絶縁膜7を形成し、前記半導体層の上面と平面的に重なるようにして導電膜からなる抵抗素子13(例えばポリシリコン抵抗素子)を配置する。多数のポリシリコン抵抗が集中して配置される領域では特に効果が大きい。

(もっと読む)

半導体装置

【課題】ドレイン電流の大きさが規格上の電流を満足しつつ、ドレイン電流に起因するノイズの発生を抑制し、かつゲート幅の長寸化に起因するサイズの大型化を回避することが困難であった。

【解決手段】ゲート電極が第1のポリシリコンから形成されたMOSトランジスタと、MOSトランジスタのドレイン電極に接続された抵抗素子であって、MOSトランジスタを第1のポリシリコンから形成するときにゲート電極の長さについて施された加工と実質的に同一な加工を抵抗素子の幅について施されて第2のポリシリコンから形成された抵抗素子とを含む。

(もっと読む)

トレンチ・キャパシタとトレンチ抵抗器とを含む半導体構造物

【解決手段】構造物および該構造物を製造する方法は、トレンチ・キャパシタのためのキャパシタ・トレンチ(CT)と、トレンチ抵抗器のための抵抗器トレンチ(RT)とを使用する。この構造物は一般に半導体構造物である。第1の例では、キャパシタ・トレンチ(CT)が、抵抗器トレンチ(RT)よりも幅が狭い線幅寸法(LWC)を有する。トレンチ線幅のこの違いが、トレンチ・キャパシタおよびトレンチ抵抗器を製造する効率的な方法を提供する。第2の例では、トレンチ抵抗器が、抵抗器トレンチ(RT)の周縁に導体材料(18a、18b)を含み、抵抗器トレンチ(RT)の中心部分に抵抗器材料(20)を含む。 (もっと読む)

多層抵抗線路および高周波増幅装置

【課題】簡単に周波数特性をもたせることが実現できる多層抵抗線路を提供する。

【解決手段】基板上6に金属層4と抵抗体層3とが重ね合わせて形成されており、かつ、抵抗体層3が金属層4の上に形成されており、かつ、引き出し金属配線1に接続されている。抵抗体層3と金属層4を重ね合わせた多層構造は、低周波では多層構造全体で平均的に電界が加わり、高周波域では下層側に電界が集中する。そのため、簡単に周波数特性をもたせることが可能となる。

(もっと読む)

ポリシリコンヒューズおよび半導体装置

【課題】溶断効率を高め、微少電流と低電圧で溶断するポリシリコンヒューズおよびそれを備えた半導体装置を提供する。

【解決手段】所定線路幅を有する狭幅領域NAと、その狭幅領域NAを挟んだ線路幅の広い2つの広幅領域WAを有するポリシリコンからなる抵抗体1を備え、広幅領域WAの幅方向(X軸方向)の両端付近に同電位の電極4Aと4Cおよび4Bと4Dをそれぞれ形成する。また2つの広幅領域WAの電極形成位置の間を抵抗体非形成部17とする。

(もっと読む)

半導体装置およびその製造方法

【課題】加工精度による抵抗値のバラツキが低く、抵抗素子全体の形状に自由度のある半導体装置およびその製造方法を提供する。

【解決手段】半導体基板1に抵抗素子を備える。抵抗素子は、導電膜4と拡散層5を含む2種類以上の導電層と、導電膜と同一材料により構成され、半導体基板1に領域を規定する位置規定部4aとを備える。拡散層5は、位置規定部4aにより規定された領域の半導体基板1の表面上に形成されて形状が規定され、導電膜4と拡散層5が直列に接続される。

(もっと読む)

121 - 140 / 220

[ Back to top ]