Fターム[5F038AR13]の内容

Fターム[5F038AR13]に分類される特許

41 - 60 / 220

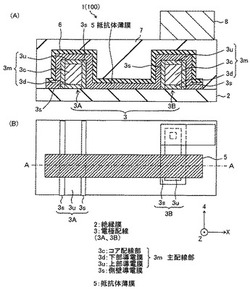

薄膜抵抗素子、および、その製造方法

【課題】安定して配線と抵抗体薄膜との接触が可能な接続構造をもつ薄膜抵抗素子を実現する。

【解決手段】互いに離間する2つの電極配線(3A,3B)に、抵抗体薄膜5を接続させている。2つの電極配線の各々が、主配線部3mと、当該主配線部3mのコア配線部3cより酸化されにくい導電材料で側面に形成されている側壁導電膜3sとを有する。抵抗体薄膜5は、2つの電極配線の各々に対して、側壁導電膜3sを介して電気的に接続している。

(もっと読む)

回路シミュレーション方法

【課題】半導体抵抗素子の端子部寄生抵抗を正確に見積もることができる回路シミュレーション方法。

【解決手段】半導体抵抗素子102と、半導体抵抗素子102の端子部上に、半導体抵抗素子102の幅方向と長手方向とにそれぞれ等間隔に配置された複数のコンタクトCTと、複数のコンタクトCT上に形成された配線101と、を備えた半導体回路のシミュレーション方法。1つのコンタクトCTの抵抗値と、長手方向において隣接するコンタクトCT間の半導体抵抗素子102による寄生抵抗値との比を、定数kとして定義し、半導体抵抗素子102の端子部と、複数のコンタクトCTと、を含む寄生抵抗ネットを、定数kを用いることによりモデル化する。

(もっと読む)

電子デバイス

【課題】製造工程数や面積の増大を招くことなく、金属薄膜抵抗の抵抗率を異ならせる素子構造を提案する。

【解決手段】基板に形成された積層構造における絶縁層間の導電膜配置階層の1つに、抵抗素子の抵抗値を規定する抵抗膜5が配置されている。また、抵抗膜5の厚さ方向の少なくとも一方の他の導電膜配置階層に、水素吸蔵金属3が、抵抗膜5と絶縁された状態で、かつ金属抵抗膜の少なくともコンタクトエッジ間の領域の全域と平面視で重なる位置と大きさで配置されている。

(もっと読む)

半導体装置の製造方法

【課題】金属薄膜抵抗体を備えた半導体装置において、金属薄膜抵抗体の抵抗値及び配線パターンとの接触抵抗の安定化を実現する。

【解決手段】下地絶縁膜5上に、金属薄膜抵抗体23の両端部の形成予定領域に対応して配線パターン11を形成する。配線パターン11上を含む下地絶縁膜5上に平坦化された絶縁膜19を形成する。平坦化された絶縁膜19に、金属薄膜抵抗体23の両端部の形成予定領域及び配線パターン11に対応して接続孔21を形成する。接続孔21内を含み絶縁膜19に対してArスパッタエッチング技術によりエッチング処理を施して、接続孔21の内壁にサイドウォール22を形成するとともに、接続孔21の上端部21aをテーパー形状にする。接続孔21内及び絶縁膜19上に金属薄膜抵抗体23を形成するための金属薄膜を形成する。接続孔21にも金属薄膜を残存させるように金属薄膜をパターニングして金属薄膜抵抗体23を形成する。

(もっと読む)

ICチップの基板が薄くなった箇所を検出する装置

【課題】ICチップの基板が薄くなった箇所を検出する装置を提供する。

【解決手段】ICチップの基板が薄くなった箇所を検出する装置は、基板の活性領域に、ホイートストン・ブリッジとして接続された、棒形状の分散された複数の抵抗を備え、ブリッジの第1の対向する抵抗の組は、第1の方向に向いており、ブリッジの第2の対向する抵抗の組は、第2の方向に向いており、第1及び第2の方向は、基板が薄くなった箇所がブリッジの不均衡値を変化させる方向である。

(もっと読む)

半導体装置およびその製造方法

【課題】チップサイズの縮小化と抵抗値のばらつきの低減化とが両立された抵抗体を有する半導体装置及びその製造方法を提供する。

【解決手段】アナログ回路を構成する半導体装置21であって、シリコン基板1と、シリコン基板1上に形成されたシリコンを主成分とする線状の抵抗体3と、抵抗体3の両端部のうちいずれかの端部に接して形成された金属シリサイドからなる複数のコンタクト形成領域7と、抵抗体3及び複数のコンタクト形成領域7の上に形成された層間絶縁膜4と、層間絶縁膜4を貫通し、複数のコンタクト形成領域7のそれぞれと層間絶縁膜4上に形成された金属配線6とを電気接続する複数のコンタクトプラグ5とを有し、複数のコンタクト形成領域7のそれぞれの面内パターンは、抵抗体3から、少なくとも2箇所で面内屈曲していることにより、コンタクト形成領域7の一部が抵抗体3に並行して形成されている。

(もっと読む)

半導体保護装置

【課題】

抵抗とダイオードを同一n型不純物領域で形成した半導体保護装置において、半導体保護装置のEMIフィルタ特性を維持してパッド部を離間する場合には抵抗Rの幅Wを広くし、パッド部下方のpn接合容量を小さくする必要がある。この場合、パッド部下方のpn接合容量小さくなることによりESD耐量が劣化する問題があった。

【解決手段】

半導体保護装置の抵抗となるn型不純物領域とダイオードとなるn型不純物領域を離間し、抵抗となるn型不純物領域の面積をEMIフィルタ特性において必要な最小限の面積とすることで、ダイオードとなるn型不純物領域の総面積を最大限に確保できる。これによりESD耐量を従来より向上しつつパッド部間を離間できる。

さらに半導体保護装置の抵抗となるn型不純物領域両端の面積を抵抗の幅より拡大し、これと離間して抵抗となるn型不純物領域両端と同等の面積の他のn型不純物領域を設けてダイオードとすることで、ESD耐量の向上が実現する。

(もっと読む)

半導体装置およびその製造方法

【課題】 設計値に近似の抵抗値を有するポリシリコン抵抗素子を備えた半導体装置およびその製造方法を提供する。

【解決手段】 本発明の半導体装置では、半導体基板の主面を含む内部にMOSトランジスタが形成され、このMOSトランジスタを取り囲んで素子分離絶縁膜3が形成されている。この素子分離絶縁膜3上方には、端子部11とこの端子11間に形成された抵抗部12とを備えたポリシリコン抵抗素子10が形成されている。そして、ポリシリコン抵抗素子10の抵抗部12は、同一形状、および同一寸法の複数の網目13を有する網構造に構成されており、かつ隣接する網目13の間隔が全て同一に形成されている。

(もっと読む)

抵抗アレイ及びそれを用いた集積回路

【課題】微細化した抵抗アレイ及びそれを用いた集積回路において、局所的な温度分布の影響を軽減して相対精度を向上する。

【解決手段】抵抗アレイは、素子分離膜102を有する半導体基板101上に形成された複数の抵抗素子103を含む。それぞれの抵抗素子103は、少なくともシリコンを含む多結晶体からなる抵抗部と、シリサイド層を含むコンタクト部104とを備える。それぞれの抵抗素子103の少なくとも一部が、素子分離膜102よりも膜厚の薄い絶縁膜301を介して半導体基板101上に配置されている。

(もっと読む)

半導体装置

【課題】容量素子と抵抗素子とを立体に構成した素子においては、その容量素子の上部電極と抵抗素子とが兼用されているため、容量素子の容量値を大きくできないという問題があった。

【解決手段】

本発明の半導体装置の構造は、容量素子と抵抗素子とを立体に構成しても容量素子の容量値を大きくすることができる。すなわち、容量素子の下部電極に凹部または段差部を設け、そこに上部電極を入り込むように設けている。このような構成にすることにより、上部電極と下部電極との接触面積が増えるため、上部電極を抵抗素子としていても、その抵抗値を下げることなく、容量素子の容量値を大きくすることができる。また、下部電極に凹部または段差部を設けているため、平坦化することができる。

(もっと読む)

半導体装置

【課題】 抵抗部と分離部の間のリーク電流を抑える技術を提供する。

【解決手段】 半導体装置100は、半導体基部10と分離部20と抵抗部30と電流補償部40を備えている。抵抗部30は、高電位側に接続される高電位側接続部位30Hと、低電位側に接続される低電位側接続部位30Lを有する。分離部20は、抵抗部30の高電位側接続部位30Hに隣接する第1部位20Hが高電位側に接続され、抵抗部30の低電位側接続部位30Lに隣接する第2部位20Lが低電位側に接続される。電流補償部40は、第1部位20Hと第2部位20Lの間の少なくとも一部に配置されている。電流補償部40と分離部20の間の抵抗値は、抵抗部30と分離部20の間の抵抗値よりも小さい。

(もっと読む)

半導体装置

【課題】シールリングを加工することなく、半導体装置周辺部の異常を検出可能な半導体装置を提供する。

【解決手段】多層配線層が形成された半導体基板2上に、複数の電極端子5,6,7,8,9を設けるとともに、半導体基板2の外周部に設けられたシールリング3,4と、電極端子5,6,7,8,9とを電気的に接続する不純物注入領域(ドープ領域)2a,2b,2cを半導体基板2に形成することで、電極端子5,6,7,8,9間の抵抗などを測定することにより、半導体装置1周辺部の異常が検出可能になる。

(もっと読む)

抵抗素子の製造方法

【課題】本発明は、プラズマ原子層堆積法(プラズマALD法)の下地の絶縁膜の絶縁性能を低下させず、プラズマALD法での膜形成により高精度の抵抗素子の形成を可能にする。

【解決手段】表面が絶縁性(例えば絶縁層12)を有する基板10に、熱的原子層堆積法によって第1抵抗層21を形成する第1工程と、プラズマ原子層堆積法によって前記第1抵抗層21上に前記第1抵抗層21と同種の第2抵抗層22を形成する第2工程を有する。

(もっと読む)

半導体装置

【課題】高精度の抵抗回路が設計できるように比精度良く多結晶シリコン抵抗が作成できる方法を提供する。

【解決手段】多結晶シリコン抵抗を構成する低濃度不純物領域の低濃度不純物領域を覆う金属部分の占有面積を調節する構成をもつことで、抵抗値のあわせ込みをおこなったあともさらに比精度のあわせ込みを行える半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】拡散抵抗領域の長手方向の端部と該拡散抵抗領域の長手方向にある絶縁分離用トレンチ内の(ドープド)ポリシリコン膜との電気的接続に要する表面面積を少なくすることのできる半導体装置およびその製造方法を提供すること。

【解決手段】前記拡散抵抗領域7はトレンチ3aより相互に絶縁分離され、前記トレンチ3aの側壁にゲート絶縁膜4aを介して設けられているポリシリコン5aが、前記拡散抵抗領域3のいずれか一方の端部のp+コンタクト領域7bのみに接続され、短絡されている半導体装置とする。

(もっと読む)

半導体装置およびその製造方法

【目的】電気的な絶縁性を必要とする2本の電極配線の間にある層間絶縁膜の段差部にバリアメタルの残渣が残らない半導体装置およびその製造方法を提供する。

【解決手段】温度検出用ダイオードを形成するポリシリコン端面のテーパー角θ1を45°以下とすることで、ポリシリコン18上の層間絶縁膜段差部の外角θ2を90°以上にすることができて、電気的に絶縁性を必要とする箇所にバリアメタル残渣を残さないようにできる。その結果、温度検出用ダイオードを有する半導体素子において、温度検出用ダイオードのアノード電極配線とカソード電極配線間の電気的な絶縁性を確保できて、正確な温度の検出ができる。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】半導体装置の材料コスト、製造コストを低減可能な半導体装置およびその製造方法を提供する。

【解決手段】本発明にかかる半導体装置の製造方法は、シリコンサーメット膜5を形成する工程と、シリコンサーメット膜5を保護する保護膜4を形成する工程と、保護膜4をプラズマエッチングすることでコンタクトホール6を形成する開口工程と、を備える。そして、開口工程におけるエッチングの終点を検出するためのエッチング検出層3が保護膜4と接するように形成されている。保護膜4とエッチング検出層3の少なくとも一方には、保護膜4に含まれる元素とエッチング検出層3に含まれる元素のうち両方に共通しない元素が含まれている。開口工程において、両方に共通しない元素のプラズマ発光に基づき保護膜4のエッチングの終点を検出する。

(もっと読む)

抵抗変化型素子および抵抗変化型素子製造方法

【課題】書換え可能で不揮発性の抵抗変化型素子およびその製造方法を提供する。

【解決手段】本発明の抵抗変化型素子Xは、P型半導性を有する酸化物部4と、相互に離隔して酸化物部4に接合する一対の電極1と、一対の電極1の間において酸化物部4に接合する電極2と、酸化物部4を介して電極2に対向する部位を有して酸化物部4に接合する電極3とを備える。本発明の抵抗変化型素子製造方法は、例えば、基材S上に導電材料膜を形成する工程と、P型半導性を有する酸化物膜を導電材料膜上に形成する工程と、相互に離隔する一対の電極1および当該電極1間に位置する電極2を酸化物膜上に形成する工程とを含む。

(もっと読む)

半導体装置

【課題】抵抗素子の抵抗値の基板電圧依存性をなくす。

【解決手段】基板領域(25A,25B)上に互いに直列に接続される抵抗素子(R1、R2)において、抵抗素子の基板領域と対応の抵抗素子の間の平均電位が逆極性でかつ大きさが等しくなるように、抵抗素子端部と対応の基板領域とをバイアス配線(27A,27B)で接続する。

(もっと読む)

半導体装置

【課題】通信距離が極端に短い場合においても正常に動作し、かつ、信頼性の高い半導体装置(RFタグ)を提供する。

【解決手段】無線によりデータの交信が可能な半導体装置(RFタグ)を構成する素子を保護するための保護回路(リミッタ回路)を設ける。整流回路において生成された直流電源電位が所定の値(基準値)以上となるときに保護回路が動作するようにし、生成される直流電源電位の値を小さくする。一方、整流回路において生成された直流電源電位が所定の値(基準値)以下となるときは、保護回路が動作しないようにし、生成された直流電源電位の値をそのまま用いる。

(もっと読む)

41 - 60 / 220

[ Back to top ]