Fターム[5F038BE07]の内容

Fターム[5F038BE07]に分類される特許

201 - 220 / 1,173

半導体集積回路および電子回路

【課題】簡易な工程で保護ダイオードが有する寄生容量を内部回路から分離し、半導体集積回路の高速化を実現することが可能な半導体集積回路および電子回路を提供することを目的とする。

【解決手段】信号端子120と内部回路132とを接続する信号ライン134と、信号ライン134から分岐して接続されるヒューズ素子F1と、ヒューズ素子F1を介して信号ライン134と接続し、正電源VDDまたは負電源VSSが直接接続される通電端子136と、ヒューズ素子F1の通電端子136側に接続され、信号ライン134と正電源VDDまたは負電源VSSとの間をそれぞれ逆方向に接続する保護ダイオードD1、D2と、を備えることを特徴とする。

(もっと読む)

テスト回路

【課題】レイアウトが複雑になることを抑える。

【解決手段】テスト対象とされる複数の出力バッファ11のそれぞれに対応してサブテスト回路1aを備える。それぞれのサブテスト回路1aは、前段のサブテスト回路1aの出力が後段のサブテスト回路1aの入力に接続されてチェーン構成をなし、初段のサブテスト回路1aの入力には信号TDIを入力し、最終段のサブテスト回路1aの出力から信号TDOを出力する。サブテスト回路1aは、対応する出力バッファ11の出力値と入力における入力値とが異なる場合に、出力に信号TDIの論理値とは異なる論理値を出力する。

(もっと読む)

半導体集積回路装置

【課題】フリップチップ構造を有する半導体集積回路装置において、パッドからチップ内部素子へ加わる応力の影響に起因するタイミング信頼性の劣化を低コストで防止する。

【解決手段】フリップチップ構造を有する半導体集積回路装置において、応力の影響を受ける半導体チップ101の外周列におけるパッド102の構造及び配置位置等について、応力の影響に起因するLSIの動作不具合が発生しにくいように予めレイアウトする。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通電極を有する半導体装置の信頼性を向上させる。

【解決手段】半導体基板1は、素子形成面である第1の面1a及びその反対側の第2の面1bを有する。第1の面1aから第2の面1bまで半導体基板1を貫通するように貫通孔20が形成されている。貫通孔20の内壁上に絶縁膜21及びバリア膜22が順次形成されている。絶縁膜21及びバリア膜22が形成された貫通孔20が埋まるように導電部23が形成されている。貫通孔20の周辺に位置する部分の半導体基板1における少なくとも第1の面1a側にゲッタリングサイト30が形成されている。

(もっと読む)

半導体集積回路装置

【課題】電極パッドからESD保護回路に十分なサージ電流が流れず、入出力回路が破壊されやすくなる。

【解決手段】半導体集積回路装置201の回路ブロック21の上層に、電極パッド22が設けられている。電極パッド202,213と、内部回路208およびESD保護回路206との間の接続配線に、分岐点A204,分岐点B212が設けられている。分岐点A204,分岐点B212は、電極パッド202,213よりもESD保護回路206に近い位置に、配置されている。

(もっと読む)

半導体素子及び半導体装置の製造方法

【課題】隣接した半導体素子領域(IC領域)を同時に検査しても、検査用のプローブが外部電極から食み出し難くい、半導体素子、半導体ウエハ、及び半導体装置の製造方法を提供する。

【解決手段】外周に沿って配置された複数の外部電極28を有する、矩形の半導体素子38であって、前記外部電極の対向する二辺が、前記半導体素子の一の対角線34に垂直な方向36を向いている半導体素子。

(もっと読む)

高周波半導体装置

【課題】FETセルごとに電源を用意・制御することなく、所望の出力電力値に合わせて、出力電力値を調整可能な高周波半導体装置を提供する。

【解決手段】分配・入力整合回路32と入力伝送線路パターン36とを搭載した分配・入力整合回路基板14と、複数の入力キャパシタセル40を搭載した入力キャパシタ基板16と、複数の電界効果トランジスタセルを搭載した半導体基板18と、複数の出力キャパシタセル41を搭載した出力キャパシタ基板20と、出力伝送線路パターン38と合成・出力整合回路34とを搭載した合成・出力整合回路基板22とを備え、所望の出力電力値に合わせて複数のセルからなる電界効果トランジスタのセル数を接続・非接続により、総ゲート電極長を実質的に変化させて、出力電力値を調整可能な高周波半導体装置30。

(もっと読む)

半導体装置及び半導体装置の試験方法

【課題】テストコストの低減及び不良解析の精度向上を図った半導体装置を提供する。

【解決手段】半導体装置100は、被調整電源13の出力である被調整電源出力電圧Vaを調整するトリミングコードTRMC(=TRMC1)を変化させながら発生し、被調整電源出力電圧Vaが入力電圧Vinに対応する値となった場合、電圧供給回路25の出力電圧Voutの基準電圧Vrefと同じ電圧レベルに出力変更し、入力初段回路へ供給する。また、トリミングコードTRMCをトリミングコード記憶回路16に記憶し、記憶したトリミングコードTRMC(=TRMC2)に基づき被調整電源出力電圧Vaを設定する。

(もっと読む)

半導体装置

【課題】 同時に入出力されるデータビット数が異なる半導体装置では、プリント基板の半田ボールと半導体チップのパッド位置が、左右の領域に分かれ、ボールとパッド間の配線ができなくなり、ビット数が異なる製品を、1つのチップで共用することができないという問題がある。

【解決手段】 同時に入出力されるデータビット数が8、16、32ビットのいずれかに変更可能で、複数のパッド電極がチップの中央部に少なくとも2列に配列された半導体チップを有した半導体装置は、前記複数のパッド電極の中の所定のパッド電極が、データ入出力数が16ビットのときのみに使用される16ビット専用のパッド電極と、データ入出力数が32ビットのときのみに使用される32ビット専用のパッド電極と、を備えることを特徴とする。

(もっと読む)

半導体装置および半導体装置の制御方法

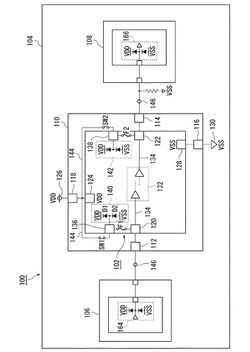

【課題】簡単な構成により、用途が異なるパッドを同一のパッドで兼用することができる半導体装置および半導体装置の制御方法を提供する。

【解決手段】半導体装置100は、共用パッド120と、電源電位を生成する内部発生電源部110と、共用パッド120と内部発生電源110との間を接続状態または非接続状態にするNMOSスイッチ140と、共用パッド120に電源電位と異なる特定電位が供給された場合には、NMOSスイッチ140を非接続状態にするとともに、特定機能を指示する特定指示信号を出力し、共用パッド120に特定電位が供給されない場合には、NMOSスイッチ140を接続状態にする制御部130と、を含む。

(もっと読む)

半導体メモリ装置及びそれを含む半導体パッケージ

【課題】高性能及び低電力が要求される多様な装置及びシステムを支援できる、マルチチャネルインタフェース方式のワイド入出力を有する半導体メモリ装置及びそれを含む半導体パッケージを提供する。

【解決手段】本発明の一実施形態に係る半導体メモリ装置は、複数のメモリセルアレイを含む半導体ダイからなり、半導体ダイの中央部に形成される入出力バンプパッド部を含む。入出力バンプパッド部は、前記それぞれのメモリセルアレイを外部装置と独立的に接続するための複数のチャネルを提供する。マルチチャネル方式のワイド入出力インタフェースを通じて動作周波数の減少及びバンド幅の拡張を図ることによって、高性能の装置及びシステムを支援すると同時に電力消耗を減少させる。

(もっと読む)

半導体装置、及びその設計方法

【課題】小さいチップサイズで、ノイズを低減することできる半導体装置、及びその設計方法を提供すること。

【解決手段】本発明の一態様に係る半導体装置は、入力に応じて容量が変化する素子13を備え、所定の機能を有する機能マクロ11と、機能マクロ11の不使用時において、素子13によって機能マクロ11の容量を制御するものである。これにより、小さいチップサイズで、ノイズを低減することできる半導体装置、及びその設計方法を提供することができる。

(もっと読む)

半導体装置および検査システム

【課題】破壊を伴うことなく正確に半導体装置の接続状態の検査を行うことを目的とする。

【解決手段】実装基板2に半導体チップ3を実装して構成され、外部から供給される電源を半導体チップ3の内部回路30に伝送する電源伝送部を備える半導体装置1であって、電源伝送部は、実装基板2上に設けられ、外部から供給される電源を入力するための電源入力端子と、実装基板2上に設けられ、この実装基板2と半導体チップ3との間の接続状態の検査を行うための検査入力端子と、電源入力端子から入力した電源を分配して内部回路30に伝送する複数の電源経路と、各電源経路に一端が接続され、他端が合流されて検査入力端子に接続される複数の分岐経路と、各分岐経路上に設けられ、各分岐経路が合流する前に設けた抵抗26と、を備えている。

(もっと読む)

半導体装置

【課題】一つの半導体装置をボンディングオプションにより機能の異なる製品に切り替える場合に、その半導体装置で使用される内部電源の安定化容量を、それぞれの製品において最適化することができる半導体装置を提供する。

【解決手段】半導体装置10は、異なる電源電位の電圧が供給される2つのインナーリード12A、12Bに選択的にワイヤーボンディングされるボンディングオプション用パッド14と、ボンディングオプション用パッド14に接続されるインバータ16と、短絡されたソース及びドレインがインバータ16に接続され、ゲートが内部電源IVから電源電圧が出力される電源出力ライン18に接続された、内部電源IVの出力レベルを安定化させるためのNMOSトランジスタ20と、を備える。

(もっと読む)

半導体装置

【課題】チップ容量自体が変化する場合においても、システム全体の電源設計を最適化する。

【解決手段】半導体チップ23にコンデンサ7〜9および選択スイッチ14〜16を設け、コアブロック1〜3のうちのいずれかを停止させた場合、そのコアブロック1〜3に対応した選択スイッチ14〜16をオンさせることにより、そのコアブロック1〜3に対応したコンデンサ7〜9を電源ライン24に接続する。

(もっと読む)

配線構造

【課題】電源・信号間の干渉および結合の抑制と、電源ノイズの抑制と、信号間の干渉・クロストークの抑制と、インピーダンス不連続による信号反射の抑制とを、全てバランスよく満たす低コストな高速デバイスを提供する。

【解決手段】信号用ボンディングワイヤ31d、31eと、グランド用ボンディングワイヤ31b、31gと、電源用ボンディングワイヤ32a、32c、32f]とを、次のように配置する。すなわち、グランド用ボンディングワイヤまたは電源用ボンディングワイヤの一方が、信号用ボンディングワイヤと同じ第1の包絡面に含まれ、他方は別の第2の包絡面に含まれる。ここで、第2の包絡面に含まれるボンディングワイヤおよび信号用ボンディングワイヤの間の電磁結合が、第1の包絡面に含まれる2本のボンディングワイヤの間の電磁結合よりも小さくなるようにする配線構造。

(もっと読む)

半導体集積回路

【課題】チップ面積が増大することなく設計において大きな後戻りをしなくてすむ半導体集積回路を提供すること。

【解決手段】一列に配列された各IOバッファ1〜5と、各IOバッファ1〜5に対応して配列されたパッド接続用配線21〜25と、各IOバッファ1〜5に対応して一列に配列されるとともに、IOバッファ1〜5及びパッド接続用配線21〜25と異なる層にて対応するパッド接続用配線の一部と重なるように配置され、かつ、対応するパッド接続用配線の隣の他のパッド接続用配線まで延長して配線されたIOバッファ切替用配線31〜35と、を備え、各IOバッファ切替用配線31〜35は、隣の他のIOバッファ切替用配線と短絡しないように同じ形状に形成され、各IOバッファ1〜5は、同じ位置にて対応するIOバッファ切替用配線31〜35と電気的に接続される。

(もっと読む)

電界効果トランジスタ、電子装置、電界効果トランジスタの製造方法及び使用方法

【課題】 チップ面積を大きくし過ぎることなく、過電圧、過電力が加わっても破壊されない電界効果トランジスタを提供する。

【解決手段】 本発明の電界効果トランジスタは、

半導体層上に、ゲート電極110と、ドレイン電極109と、ソース電極108と、保護ダイオード(保護ダイオード電極)111とが配置され、

ドレイン電極109が、保護ダイオード111の周囲の一部もしくは全部を囲む状態で形成されているか、または、

ドレイン電極109は、複数であり、複数のドレイン電極109の少なくとも一対のドレイン電極間に、保護ダイオード111が配置されるように形成されていることを特徴とする。

(もっと読む)

半導体装置、半導体装置の試験方法、及びデータ処理システム

【課題】インターフェースチップを用いるタイプの半導体装置において、インターフェースチップとコアチップ間の複数の貫通電極にそれぞれ関する複数の電流パスで大きなAC特性の差がないことの確認試験を行えるようにする。

【解決手段】インターフェースチップ及びコアチップと、これらを電気的に接続するそれぞれが貫通電極を含む測定対象信号線130及び基準信号線131と、を備え、インターフェースチップは、信号発生回路100が発生したテストクロックをコアチップへ送出し、コアチップは、信号発生回路101がテストクロックから所定の測定信号を発生し、且つ所定の測定信号を測定対象信号線130及び基準信号線131へ同時に送出し、更に、インターフェースチップは、更に、測定対象信号線130及び基準信号線131を介して入力した複数の所定の測定信号の位相差をオペアンプ117によって検出し、判定回路102が試験結果を出力する。

(もっと読む)

半導体集積回路

【課題】電源プレーンと内部回路とを接続パッドを介して接続する、接続経路のインピーダンスに応じた適切な放電能力の保護回路を有する半導体集積回路を提供する。

【解決手段】本発明に係る半導体集積回路1aは、半導体チップ10aと、半導体チップ10aに電位を供給するパッケージ2とを有し、半導体チップ10aは、内部回路と、接続パッドと、内部回路と接続パッドの間に接続され、内部回路を保護する保護回路とを有し、パッケージ2は、外部端子と、パッケージ2と半導体チップ10aを接続するための内部端子と、電源プレーンと、電源プレーンと内部端子とを接続する第1の配線と、内部端子と接続パッドとをそれぞれ接続する複数の第2の配線とを有する。保護回路の放電能力の大きさは、電源プレーンと接続パッドとの接続経路である、第1の配線、内部端子および第2の配線のインピーダンスに応じて設定される。

(もっと読む)

201 - 220 / 1,173

[ Back to top ]