Fターム[5F038BE07]の内容

Fターム[5F038BE07]に分類される特許

141 - 160 / 1,173

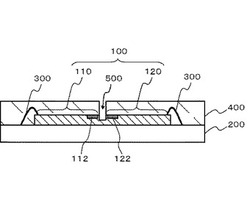

半導体装置、電子装置、及び半導体装置の製造方法

【課題】第1インダクタと第2インダクタを構成する金属材料のマイグレーションに起因して第1インダクタと第2インダクタの絶縁が確保できなくなることを、抑制する。

【解決手段】半導体チップ100は配線基板200の第1面上に実装されており、多層配線層を有している。第1インダクタ112は多層配線層に形成されており、巻き軸方向が配線基板200と水平方向を向いている。第2インダクタ122は多層配線層に形成されており、巻き軸方向が配線基板200と水平方向を向いている。第2インダクタ122は第1インダクタ112に対向している。封止樹脂400は、配線基板200の少なくとも第1面と、半導体チップ100とを封止している。溝500は、封止樹脂400と多層配線層の界面のうち、少なくとも第1インダクタ112と第2インダクタ122の間に位置している部分の全域に形成されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】プローブ跡を除去でき、かつ、製造コストが増加することを抑制できる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】この半導体装置は、回路が形成された基板100と、この基板100上に形成され、表面に保護絶縁膜300が形成された多層配線層と、この多層配線層の最上層の配線層に位置し、上記回路に接続し、かつ、表面が保護絶縁膜と略同一面となっている電極パッド200と、を備える。また、このような半導体装置の製造方法は、回路が形成された基板100上に、この回路に接続し、かつ、保護絶縁膜300から突出した突出部201を有する電極パッド200を形成する工程と、プローブ端子500を電極パッド200に接触させることにより、回路の動作テストを行う工程と、突出部201の少なくとも表面を研磨する工程と、有する。

(もっと読む)

半導体集積回路装置

【課題】半導体基板の表側に配置された回路が半導体基板の裏側から解析されることを検出する技術を提供することを目的とする。

【解決手段】回路ブロックが配置された第1面と、第1面の反対側の第2面とを有する半導体基板と、半導体基板を搭載する実装基板と、実装基板のうち、回路ブロックの保護対象の部分と重なる領域に配置された導電パターンと、導電パターンに改変が加えられたことを検出する検出回路とを有する半導体集積回路装置が提供される。半導体基板の第2面と実装基板とが対向するように、半導体基板が実装基板に搭載されている。

(もっと読む)

半導体集積回路装置

【課題】保護対象の回路ブロックの上に配置された導電パターンに加えられた改変の検出精度を向上するための技術を提供することを目的とする。

【解決手段】半導体基板に配置された回路ブロックと、回路ブロックのうち保護対象の部分の上層に配置された導電パターンと、導電パターンの第1部分の電位を基準電位にリセットするリセット部と、第1部分を電流供給ラインに接続する接続部と、第1部分の電位を基準電位にリセットした後に第1部分を電流供給ラインに接続してから一定時間経過後の第1部分の電圧が事前に設定された範囲に含まれるか否かを判定し、一定時間経過後の電圧が事前に設定された範囲に含まれない場合に導電パターンに改変が加えられたことを検出する検出回路とを有する半導体集積回路装置が提供される。第1部分の電圧の変化は、導電パターンの回路定数に依存する。

(もっと読む)

モータ制御用半導体装置

【課題】モータ制御用半導体装置に対するコンタクト用ピンからの影響を低減する

【解決手段】ホール素子102からの出力のオフセット電圧を取り除くオフセットキャンセル回路104に含まれるオシレータ回路12と、オフセットキャンセル回路104からの出力信号を受けて、当該出力信号と基準信号とを比較して比較信号を生成して出力するコンパレータ回路106と、モータを駆動するための駆動信号を生成して出力する出力回路110と、モータの制御に関係しないテスト回路112と、を有し、オシレータ回路12の回路パターン上、コンパレータ回路106の回路パターン上、及び、テスト回路112の回路パターン上のいずれか1つに重なるようにパルス幅変調信号の入出力パッドP1を形成する。

(もっと読む)

ヒータ配線付き半導体チップ

【課題】半導体チップの高信頼実装技術を提供。

【解決手段】半導体チップ4は、基板100と、前記基板の一方の面に形成されたデバイス層80と、電磁波の輻射により発熱するヒータ配線302と、前記デバイス層と電気的に接続される電極103とを備えることを特徴とする。半導体チップ4を実装基板に実装する際には、ヒータとしての金属配線膜302を発熱させることにより、固着材料を溶かして半導体チップを実装基板と接続させる。

(もっと読む)

半導体装置

【課題】安定した静電気保護機能を有する半導体装置を提供すること。

【解決手段】半導体装置は、シリコン柱を有するシリコン基板、シリコン柱の側壁に沿って形成されたゲート電極、ゲート電極とシリコン柱との間に形成されたゲート絶縁膜シリコン柱の上部に形成された上部拡散層、及びシリコン基板において上部拡散層より下方に形成された下部拡散層、を有する縦型MOSトランジスタと、下部拡散層と電気的に接続されたパッドと、を備える。サージ電圧が印加された際に下部拡散層と基板との間においてブレイクダウンが発生する。

(もっと読む)

半導体集積回路および半導体集積回路装置

【課題】 電源電圧の安定した供給が可能な半導体集積回路および半導体集積回路装置を提供する。

【解決手段】 半導体集積回路40において、半導体基板の表面の、コア領域に、第1の電源が供給されて動作するコア回路が形成されるとともに、前記半導体基板の表面の前記コア領域の外側のI/O領域に、第2の電源が供給されて動作するI/O回路が形成された半導体集積回路40であって、前記半導体基板内に、該半導体基板を貫通して、前記第1の電源を供給する貫通ビア51が設けられ、前記半導体基板の表面のI/O領域に、前記第2の電源を供給するパッド46が設けられたことを特徴とする。

(もっと読む)

多層回路基板、基板装置、および多層回路基板の異常判定方法

【課題】スイッチング素子の駆動により生じる熱について精度よく検出することのできる多層回路基板を提供する。

【解決手段】パワー基板4の基板本体10は、積層された複数の絶縁層11,12,13の間に導電層21,22が配置された構成を有している。基板本体10の上面10aにベアチップ実装された半導体チップ15は、スイッチング素子28と、上温度センサ29と、を含んでいる。CPU7は、上温度センサ29の検出温度T1、およびスイッチング素子28の発熱量Q1を用いて疑似熱抵抗TR1を演算する。CPU7は、疑似熱抵抗TR1が大きいとき、パワー基板4に異常が生じていると判定する。

(もっと読む)

高周波スイッチ

【課題】出力特性が優れた高周波スイッチを提供する。

【解決手段】本発明の実施形態の高周波スイッチは、入力端子ANT1と複数のスイッチング素子と複数の高周波信号線と複数の出力端子RF1〜RF8とからなる高周波スイッチ回路部を有する高周波スイッチICチップ10を備える。前記入力端子ANT1と前記複数の出力端子の各出力端子RF1〜RF8は、それぞれ等しい長さの高周波信号線H1〜H8で接続される。前記複数の出力端子RF1〜RF8は、前記高周波スイッチICチップの外周の表面上に配置される。前記入力端子ANT1は、前記高周波スイッチ回路部の中心に配置される。

(もっと読む)

素子チップ、素子内蔵基板及び電子機器

【課題】素子チップの厚み方向に素子チップを押圧しても曲げ応力が加わり難い構造の素子チップを提供する。

【解決手段】回路基板13に接着剤12を介して実装される素子チップ1にかかわる。基板2上にスパイラルインダクターを構成するインダクター配線5と、インダクター配線5に沿ってインダクター配線5の一部を覆う第1樹脂膜6と、第1樹脂膜6に覆われていないインダクター配線5の他の一部と基板2との間に位置する第2樹脂膜7を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】多層配線層の層間における剥離の有無を簡便な手法で検出できるようにする。

【解決手段】第1電極412は多層配線層20に形成されている。第2電極422は、絶縁膜22の一部を介して第1電極412と対向している。第1電極パッド430は第1電極412に接続している。第2電極パッド432は第2電極422に接続している。そして少なくとも2層以上の絶縁膜22のそれぞれが、第1電極412及び第2電極422に挟まれている。そして第1電極412及び第2電極422により、センサ40の少なくとも一部が形成されている。センサ40は、多層配線層20の層間における剥離の有無を検出するために用いられる。

(もっと読む)

DC−DCコンバータ

【課題】配線抵抗及び寄生インダクタンスを低減し、スパイク状のノイズの低減を図る。

【解決手段】DC−DCコンバータ110の半導体装置20は、第1スイッチ素子Q1と、第2スイッチ素子Q2と、入力電位Vinが与えられる第1配線層と、インダクタLと接続される第2配線層と、基準電位GNDが与えられる第3配線層と、インダクタLと接続される第4配線層と、を有し、これらが同一層において一方向に並んで配置される。実装用基板10は、入力電位Vinが与えられ、第1配線パターンと導通し、半導体装置の実装領域に対して一方側に隣接して配置された第5配線パターン15と、基準電圧GNDが与えられ、第3配線パターンと導通し、実装領域に対して一方側に隣接して配置された第6配線パターン16と、第2配線パターン及び第4配線パターンと導通し、実装領域に対して他方側に隣接して配置された第7配線パターン17と、を有する。

(もっと読む)

熱特性推定装置及び方法、並びに、温度推定装置及び方法、並びに、半導体装置

【課題】 半導体装置が装置に実装された状態での熱特性を求めて、ジャンクション温度の推定に適用する。

【解決手段】 本発明は、ジャンクション温度が制限温度を超えると、当該半導体装置の負荷を低下させる熱保護手段を備えた半導体装置の熱特性を推定する熱特性推定装置と、熱特性を利用して半導体装置のジャンクション温度を推定する温度推定装置に関する。そして、本発明の熱特性推定装置は、半導体装置のジャンクション温度が制限温度となる消費電力で半導体装置を動作させた状態で半導体装置の周囲の雰囲気温度を測定する手段と、測定した温度を利用して、半導体装置の熱特性を推定する手段とを有することを特徴とする。

(もっと読む)

システムインパッケージおよびソケット

【課題】サイズやコストを増大させることなく、テスト容易なシステムインパッケージを実現するとともに、そのシステムインパッケージをテストボードとして活用する。

【解決手段】テスト容易化回路内装SIP1cは、少なくともその1つに集積回路チップが搭載された複数のコア基板を、絶縁樹脂層を介して貼り合わせて構成するとともに、コア基板に形成された配線層を、スルーホールを介して接続して構成される。そのコア基板の1つであるテスト容易化回路内装基板10cには、テスト対象の集積回路であるDUT121を装着するソケット122が搭載されており、また、そのソケット122内に設けられたポゴピン1220には、インピーダンス整合用のチップ抵抗1224、インダクタ1225などの受動素子が設けられている。

(もっと読む)

半導体装置

【課題】電源配線と接地配線とを有する半導体装置において、配線の一部における電圧ドロップや、電圧ドロップに伴うマイグレーションの発生を抑制することが可能な半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、主表面に沿うように層状に広がる電源シート状配線PPWRと、主表面に沿うように、主表面に交差する方向に関して電源シート状配線と一定の距離を隔てて層状に広がる接地シート状配線PGNDと、上記主表面上に形成され、主表面内の一の方向に延在する電源配線PWRと、主表面上に形成され、一の方向に沿う方向に延在し、電源配線PPWRと一定の距離を隔てて形成された接地配線GNDとを備える。上記電源シート状配線PPWRは、電源配線PWRと電気的に接続されており、接地シート状配線PGNDは、接地配線GNDと電気的に接続されている。

(もっと読む)

半導体装置

【課題】コモンノイズを低減する。

【解決手段】半導体装置10は、直列に接続された半導体スイッチング素子11,12と、正極端子13と、負極端子14と、出力端子15とを具備する半導体モジュール16と、半導体モジュール16に絶縁されたボディ17とを備える。ボディ17と各端子13,14との間の各浮遊容量C1,C3に対して、出力端子15とボディ17との間で、出力端子15の浮遊容量C2と浮遊容量C1とが直列接続または出力端子15の浮遊容量C2と浮遊容量C3とが直列接続になるようにして、各端子13,14,15が配置されている。

(もっと読む)

半導体チップ及びそれを搭載した半導体モジュール

【課題】半導体チップに安定した電源電流を供給したり、電源から信号系へ混入する雑音を低くするための、半導体デバイスの電源流入及び電源流出端子の端子数の低減と、前記半導体チップを搭載した実装面積の低減を可能とする半導体モジュールを提供する。

【解決手段】半導体チップ20の両面に電源系と信号系の電気的接続端子を振り分けて配置する。大電流が流れる流路の許容電流値を大きくする構成により、少ない端子数でも安定な電源供給が可能、信号系への雑音混入を低減、ピン数の低減による実装面積の低減、放熱効果の増大などが可能となる。また、この半導体チップ20を搭載した半導体モジュールにより、大電流が流れる高速動作でも安定した特性を実現できる。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子のビア構造物及び導電構造物を提供する。

【解決手段】前記ビア構造物は、平坦部及び突出部を含む表面を有する。前記導電構造物は前記平坦部のうち、少なくとも一部上に形成され、前記突出部のうち、少なくとも一部上には形成されない。例えば、前記導電構造物は前記平坦部上のみに形成されて前記突出部上には全く形成されない。これによって、前記導電構造物と前記ビア構造物との間に高品質の接続を形成することができる。

(もっと読む)

ハイパワーGaNベースFET用のレイアウトデザイン

【課題】FETを提供する。

【解決手段】FETは、基板と、基板上に配置されたバッファ層と、バッファ層上に配置されたチャネル層と、チャネル層上に配置された障壁層とを含む。ソース、ゲート及びドレイン電極は障壁層上に配置されて長手方向に延伸する。チャネル及び障壁層の一部分は長手方向に延伸するメサ部を形成し、ソース及びドレイン電極がメサ部の縁を超えて延伸する。ゲート電極はメサ部の縁側壁に沿って延伸する。導電性ソース相互接続部は障壁層上に配置されソース電極に電気的に接続された第一の端部を有する。第一の誘電体層はバッファ層及びソース相互接続部上に配置される。ゲートビアは第一の誘電体層に形成される。導電性ゲートノードがバッファ層に沿って延伸して前記メサ部の側壁に沿って延伸するゲート電極の一部分に電気的に接続する。ゲートパッドはメサ部に隣接する第一の誘電体層上に配置される。

(もっと読む)

141 - 160 / 1,173

[ Back to top ]