Fターム[5F038BE07]の内容

Fターム[5F038BE07]に分類される特許

121 - 140 / 1,173

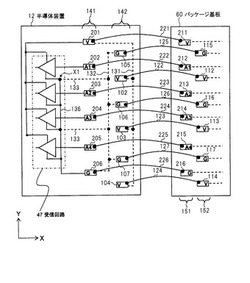

半導体パッケージ

【課題】ボンディングワイヤのループインダクタンスを低減した半導体パッケージを提供する。

【解決手段】所定の方向に交互に配置された信号用パッドおよび補助パッドのそれぞれが複数設けられた半導体装置と、信号用ボンドフィンガー、電源電圧用ボンドフィンガーおよび接地電位用ボンドフィンガーのそれぞれが複数設けられたパッケージ基板と、を有する。複数の信号用パッドのそれぞれが複数の信号用ボンドフィンガーのそれぞれと第1のワイヤを介して接続され、複数の電源電圧用ボンドフィンガーおよび複数の接地電位用ボンドフィンガーのそれぞれが複数の補助パッドのそれぞれと第2のワイヤを介して接続されている。第1のワイヤが、電源電圧用ボンドフィンガーに接続された第2のワイヤと接地電位用ボンドフィンガーに接続された第2のワイヤとの間に配置されている。

(もっと読む)

半導体装置、半導体集合部材及び半導体装置の製造方法

【課題】様々なオン抵抗の素子を容易に製造することができる半導体装置、半導体集合部材及び半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、素子部と、第1の電極部と、第2の電極部と、延出部と、を備える。素子部は、基板に設けられる。第1の電極部は、素子部の上に設けられ、素子部と導通する。第2の電極部は、素子部の上において第1の電極部と離間して設けられ、素子部と導通する。延出部は、素子部の上に設けられ、第1の電極部及び第2の電極部の周縁部から基板の周縁部に向けて延出して設けられる。

(もっと読む)

半導体パッケージ

【課題】ボンド・ワイヤの寄生インダクタンスを小さくし、高周波特性を良好とすることができる半導体パッケージを提供する。

【解決手段】高周波信号が入力される入力整合回路を有しダイボンド領域に配された半導体集積回路チップと、前記ダイボンド領域の周辺に配されたリード端子と、を備え、前記半導体集積回路チップが有する各端子と前記各リード端子とがボンド・ワイヤにより接続された半導体パッケージにおいて、前記ダイボンド領域の中央部より前記入力整合回路に高周波信号を入力させるための前記リード端子である高周波入力端子側および/または前記入力整合回路のグランド接続用の前記リード端子であるグランド端子側にシフトした位置に前記半導体集積回路チップは配される構成とする。

(もっと読む)

高周波スイッチおよび高周波モジュール

【課題】挿入損失およびチップサイズの増大を生じることなく、歪特性に優れた高周波スイッチおよび高周波モジュールを提供する。

【解決手段】高周波スイッチであって、高周波信号を入出力するための複数の入出力端子101〜103と、2つの入力端子101、103間に設けられた基本スイッチ部104、105と、基本スイッチ部104、105の導通および遮断を制御するための制御電圧が入力される制御端子106、107とを備え、基本スイッチ部104、105は、メアンダ形状のゲート電極を有するメアンダ型のFET110〜113及びFET120〜123が多段に接続されて形成され、FET110〜113、及び120〜123のうち、入出力端子103からの電気的距離が最も短いFET113、及び120のフィンガー長は、他のFET110〜112、及び121〜123のフィンガー長よりも短い。

(もっと読む)

半導体装置

【課題】内部回路の動作時における電源ノイズの影響を抑え、少ピン化および小面積化を実現する半導体装置を提供することである。

【解決手段】第1の内部回路102に対する電源線PL1と第2の内部回路104に対する電源線PL2とは共通のピン端子30aに接続され、第1の内部回路102に対する接地線SL1と第2の内部回路104に対する接地線SL2とは共通のピン端子30bに接続される。第1の内部回路102の動作時に電源線PL1上に発生した電源ノイズは、電源線PL1に介挿され、ゲートが接地線SL1に接続されたPチャネルMOSトランジスタP1および電源線PL1および接地線SL1の間に設けられたキャパシタC1により吸収される。接地線SL1上に発生した電源ノイズは、接地線SL1に介挿され、ゲートが電源線PL1に接続されたNチャネルMOSトランジスタN1およびキャパシタC1により吸収される。

(もっと読む)

半導体チップ及びこれを備える半導体装置

【課題】出力バッファのスイッチングに伴う電源ノイズがストローブ出力バッファに伝搬することを防止する。

【解決手段】データ信号DQ0を出力するデータ出力バッファOB0と、データ出力バッファOB0に電源電位VDDQを供給する電源パッド110v1と、電源パッド110v1に接続される電源配線120v1と、ストローブ信号DQSを出力するストローブ出力バッファOBdqsと、ストローブ出力バッファOBdqsに電源電位VDDQを供給する電源パッド110v2とを有し、電源配線120v1と電源パッド110v2は、互いに電気的に独立している。これにより、データ出力バッファOB0のスイッチングに伴う電源ノイズがストローブ出力バッファOBdqsに伝搬しないことから、ストローブ信号DQSの信号品質を高めることが可能となる。

(もっと読む)

半導体集積回路装置

【課題】入力回路ブロックの入力配線と出力回路ブロックの出力配線を短くする。

【解決手段】半導体集積回路装置30において、入力回路ブロック32用の外部接続用電極P2及びP3は、入力回路ブロック32と出力回路ブロック33との間に複数配置されており、出力回路ブロック33用の外部接続用電極P1及びP4は、出力回路ブロック33とリード電極34及び35との間に複数配置されており、金属細線Wb1及びWb2を介して外部接続用電極P1及びP2に接続されるリード電極34と、金属細線Wb3及びWb4を介して外部接続用電極P3及びP4に接続されるリード電極35は、いずれも、入力回路ブロック32、外部接続用電極P2及びP3、出力回路ブロック33、外部接続用電極P1及びP4、リード電極34及び35の順に配置された方向と平行する方向に複数配置されている。

(もっと読む)

電子装置およびその製造方法

【課題】半導体基板に設けられた貫通穴に、絶縁体を介して2つの導電体を充填してなるキャパシタ構造体を有する電子装置において、2つの導電体間の容量を大きくするのに適した構成を提供する。

【解決手段】半導体基板10の表裏両主面11、12間を貫通する貫通穴30には、当該穴の内面側から第1の導電体40、絶縁体50、第2の導電体60が順次充填されてキャパシタ構造体20が形成されており、キャパシタ構造体20は、貫通穴30の内部から半導体基板10の両主面11、12まで連続して形成され、キャパシタ構造体20の静電容量は、キャパシタ構造体20のうち貫通穴30に位置する部位の容量と両主面11、12に位置する部位の容量との合計とされている。

(もっと読む)

半導体装置及び電源装置

【課題】半導体装置において、抵抗が増大して変換効率が低下してしまうのを防止する。

【解決手段】半導体装置を、基板2上に形成されたGaN系半導体積層構造3を有する第1トランジスタQ1と、GaN系半導体積層構造を有する第2トランジスタQ2とを備え、第1トランジスタが、複数の第1フィンガ8AXを有する第1ゲート電極8Aと、複数の第1ドレイン電極9Aと、複数の第1ソース電極10Aとを備え、第2トランジスタが、複数の第2フィンガ8BXを有する第2ゲート電極8Bと、複数の第2ドレイン電極9Bと、複数の第2ソース電極10Bとを備え、複数の第1ドレイン電極の上方又は下方に接続されたドレインパッド15と、複数の第2ソース電極の上方又は下方に接続されたソースパッド25と、複数の第1ソース電極及び複数の第2ドレイン電極に接続された共通パッド35とを備えるものとする。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板に設けられた穴に、絶縁体を介して2つの導電体を充填してなる電極部を有する半導体装置において、2つの導電体間の容量を大きくするのに適した構成を提供する。

【解決手段】半導体基板10の第1の領域1には、表面11に開口する複数個の有底穴20が設けられ、第2の領域2には貫通穴30が設けられ、有底穴20は貫通穴30よりも小さい穴幅を有する。絶縁体50を両導電体40、60で挟んでなる積層構造体が、有底穴20および貫通穴30に充填され、さらに、第1の領域1において複数個の有底穴20間にて連続して形成されており、第1の領域1は、当該積層構造体による容量形成部として構成される。有底穴60における各導電体40、60は、それぞれ貫通穴30における各導電体40、60に電気的に接続されて、半導体基板10の表裏両面11、12に取りだされている。

(もっと読む)

周波数特性の調整方法、半導体装置の製造方法及び半導体装置

【課題】寄生容量が回避できないSi半導体基板上に集積回路と一緒に製造するオンチップアンテナにおいて、その周波数特性をウエハプロセス製造工程後に自在に所望値へ制御する。

【解決手段】Si半導体基板に対して第1のプロセスで形成される集積回路部及びアンテナ部を備える半導体装置において、該アンテナ部の周波数特性を調整する方法であって、アンテナ部と集積回路部との間に非連続的な複数の導線パターンを前記第1のプロセスにおいて形成し、第1のプロセスの終了後に、複数の導線パターンの一部又は全部を選択して、選択した前記導線パターンが直列的となるようにボンディングワイヤを懸架する。

(もっと読む)

保護装置

【課題】 差動信号ラインに、第1入力端子と第2入力端子を有し、ダイオードにより構成される1パッケージの保護装置を接続する場合、第1入力端子と第2入力端子間のアイソレーションを十分確保し、また、第1入力端子に接続するダイオードと第2入力端子に接続するダイオードの部品ばらつきを抑制する必要がある。また、差動信号ラインに用いる保護装置の場合、部品容量とESD破壊耐量を所望の範囲に収めるようにする必要がある。

【解決手段】 p半導体基板上にp型半導体層を積層し、その表面にpn接合を形成し、互いに離間する第1n+型不純物領域、第2n+型不純物領域、第3n+型不純物領域を設け、第1入力端子に接続する第1n+型不純物領域と、第2入力端子に接続する第3n+型不純物領域との間に、接地端子に接続する第2n+型不純物領域を配置して、横型の双方向pn接合ダイオードによる保護装置を提供する。

(もっと読む)

電源状態判定回路を有する集積回路

【課題】電源オープン検出回路の動作マージンを大きくする。

【解決手段】電源端子とグランド端子と入力端子と内部回路とが形成された集積回路において,入力端子と電源端子との間に設けられ,入力端子から前記電源端子への方向の一方向性回路と,電源端子が外部電源と接続しているか否かを検出して電源オープン検出信号を出力する電源状態判定回路とを有する。一方向性回路は,電源端子の電圧がゲートに印加される第1のトランジスタと,第1のトランジスタに直列に接続された第2のトランジスタとを有し,入力端子には外部電源の電圧が入力される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】入出力端子と半導体スイッチとの間を接続する配線同士が交差する箇所が発生しても、端子間のアイソレーション特性を向上させつつ、サイズ及びコストを抑制可能な半導体装置を提供する。

【解決手段】半導体スイッチ回路(20)は、複数の入力端子(31,32)のうち任意の入力端子を配線層(51)又は再配線層(251)を介して複数の出力端子(41〜44)のうち任意の出力端子と接続させるように構成される。複数の入力端子及び複数の出力端子のうち、ある端子と半導体スイッチ回路との間を接続する配線と、他の端子と半導体スイッチ回路との間を接続する配線とが交差している箇所において、交差する配線のうち、一方の配線を配線層とし、他方の配線を再配線層とする。

(もっと読む)

半導体装置

【課題】リードフレーム上に半導体チップが載置された半導体装置において、サージに対する耐性の向上を図る。

【解決手段】ICチップ10Aを構成するP型の半導体基板10の表面には、N型の埋め込み層11及びエピタキシャル層12と、P型の半導体層13が配置されている。半導体基板10の裏面には金属薄膜30が配置され、その金属薄膜30と、金属のアイランド51の間には銀粒子等を含む導電性ペースト40が挟まれている。半導体層13の表面に配置されたパッド電極16にサージが印加されると、半導体層13から半導体基板10に流れるサージ電流は、金属薄膜30を通って金属のアイランド51に向かう。

(もっと読む)

保護装置

【課題】 USBコネクタと被保護部品間の信号ラインに接続されるESD破壊の保護装置として、双方向pn接合ダイオードが用いられるが、従来の構造では製造工程が複雑、煩雑で保護装置の低コスト化や耐圧の汎用性に限界があった。

【解決手段】 p半導体基板上にp型半導体層を積層し、その表面に互いに離間する第1n+型不純物領域および第2n+型不純物領域を設け、これらの周囲に互いに離間する第1p+型不純物領域と第2p+型不純物領域を設け、第1n+型不純物領域とコンタクトし、入力端子に電気的に接続する第1電極と、第2n+型不純物領域にコンタクトし、接地端子に電気的に接続する第2電極とを設ける。第1n+型不純物領域および第2n+型不純物領域は140μm以上離間され、それぞれ角丸四角形状でp+型半導体基板の対角線に沿って配置される。

(もっと読む)

半導体装置およびバイパスキャパシタモジュール

【課題】バイパスキャパシタは、半導体基板上に形成される半導体装置と一体化されて形成されているが、半導体装置の製造工程が複雑になると言う欠点がある。

【解決手段】バイパスキャパシタをシート状にモジュール化して、半導体装置に対して外付けできるように構成されたバイパスキャパシタモジュールが得られる。

(もっと読む)

半導体装置及びそのレイアウト方法

【課題】再配線層形成工程、メタルポスト形成工程及び樹脂封止工程を経てウェハレベルで樹脂封止される半導体装置について、パッケージング工程の前後での素子の特性変動を低減させる。

【解決手段】素子が形成された半導体基板に対して、再配線層形成工程、メタルポスト形成工程及び樹脂封止工程を経てウェハレベルで樹脂封止される半導体装置について、上方から見てメタルポスト21の周縁と重なる位置に素子33,35,37を配置しないようにする。また、製造時におけるメタルポスト21に起因して生じる応力の影響を受ける、メタルポスト21の周縁から所定の範囲に素子の配置禁止領域21aを設け、配置禁止領域21aに素子33,35,37を配置しないようにする。

(もっと読む)

半導体装置

【課題】パッケージのピン数が変更された場合でも設計変更を必要としない半導体装置を提供する。

【解決手段】半導体装置に設けられた第1の選択部50は、機能ブロック群23と複数のパッド33との間の信号の経路に設けられ、各パッドごとに、標準設定として割当てられた複数の信号うち1つの信号を選択する。レジスタ61は、少なくとも第1または第2のデータを保持する。第2の選択部51は、第1の選択部50と複数のパッド33との間の信号の経路に設けられる。第2の選択部51は、レジスタ61に第1のデータが保持されたときに、第1の選択部50によって選択された各信号を標準設定のパッドを介して外部との間で入出力可能にし、レジスタ61に第2のデータが保持されたとき、第1の選択部によって選択された複数の信号のうち少なくとも一部の信号を標準設定と異なるパッドを介して外部との間で入出力可能にする。

(もっと読む)

半導体素子、半導体装置及び半導体素子の作製方法

【課題】半導体領域に酸化物半導体を用いた、高耐圧で、大電流の制御が可能であり、かつ量産性に優れた半導体素子を提供することを課題の一とする。また、該半導体素子を用いた半導体装置を提供することを課題の一とする。また、該半導体素子の作製方法を提供することを課題の一とする。

【解決手段】半導体領域に酸化物半導体を用いたトランジスタと、トランジスタのゲート電極層、ソース電極層及びドレイン電極層の各々と電気的に接続した貫通電極を備えた半導体チップを積層し、トランジスタを電気的に並列接続することによって、実質的にW長の長い半導体素子を提供する。

(もっと読む)

121 - 140 / 1,173

[ Back to top ]