Fターム[5F038BE07]の内容

Fターム[5F038BE07]に分類される特許

61 - 80 / 1,173

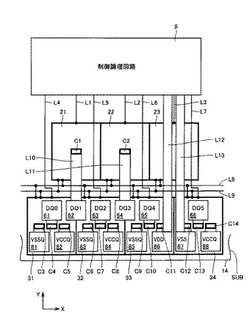

半導体装置

【課題】従来の入出力セルよりも回路面積の大きな入出力セルを面積効率良く配置する。

【解決手段】半導体装置において、複数の第1バッファセル31〜34は、基板の一辺に沿って1列に設けられる。複数の第2バッファセル21,22は、複数の第1バッファセルよりも基板の中央寄りの位置に、複数の第1バッファセルの配列方向に沿って1列に設けられる。複数の第1パッド81〜88は、複数の第1バッファセルの上部に上記配列方向に沿って1列に設けられる。複数の第2パッド61〜66は、複数の第1パッドよりも基板の中央寄りの位置に、上記配列方向に沿って1列に設けられる。複数の第2パッド61〜66は、各々が、複数の第1バッファセルのいずれか1つと個別に接続される複数の第3のパッド61,63,65,66と、各々が、複数の第2バッファセルのいずれか1つと個別に接続される複数の第4パッド62,64とを含む。

(もっと読む)

半導体装置

【課題】ブートストラップ方式のドライブ回路を有する半導体装置において、ブートストラップダイオードの順バイアス時にp-基板側に流れるホールによるリーク電流を抑制することができる半導体装置を提供することにある。

【解決手段】ブートストラップダイオードDb下にSON構造の空洞3を形成し、ブートストラップダイオードDbとグランド電位(GND)となるGNDp領域4との間のn-エピ層2にその空洞3に達するフローティングp領域5を形成することで、外部のブートストラップコンデンサC1充電時のp-基板1へのホールによるリーク電流を抑えることができる。

(もっと読む)

電力増幅器

【課題】MMICとMMIC外部回路とを接続するボンディングワイヤの影響を比較的簡単な構成で低減し、かつ省スペース化された電力増幅器を提供する。

【解決手段】MMIC基板と、MMIC基板上に配置された高周波プローブパッドと、MMIC基板上に高周波プローブパッドに隣接して配置され、MMIC外部回路とのボンディングワイヤ接続用のメタルプレートとを備える。

(もっと読む)

半導体装置

【課題】ドライバの故障による出力異常を救済することが可能な故障検出救済回路を含んだ半導体装置を提供すること。

【解決手段】故障検知部1は、ドライバ10の出力の期待電位の逆電位となるようにドライバ10の出力にプルアップ抵抗15またはプルダウン抵抗18を接続し、ドライバ10の入力電位と出力電位とを比較することによりドライバ10の故障を検出する。故障救済部2は、故障検知部1によってドライバ10の故障が検出された場合に、期待電位と同電位となるようにドライバ10の出力にプルアップ抵抗26またはプルダウン抵抗29を接続してドライバ10の故障を救済する。したがって、ドライバ10の故障による出力異常を救済することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】MIMキャパシタを備え、バイアホールを必須とせず、小さなチップサイズにおいても大きなキャパシタ容量を実現することができ、MIMキャパシタの内部電極と外部電極の電位の設定自由度が高い半導体装置を提供する。

【解決手段】半導体装置2は、半導体チップ10と、半導体チップ10の表面10Tに形成された電子回路と、半導体チップ10の少なくとも1つの側面10L、10Rに形成され、半導体チップ10側から内部電極21と絶縁膜22と外部電極23との積層構造を有するMIMキャパシタ20とを備えている。半導体装置2は、半導体チップ10の表面10T上から側面10L、10Rに形成されたMIMキャパシタ20上に平面的に延びて、MIMキャパシタ20の内部電極21に接触した表面電極30を備えている。

(もっと読む)

半導体集積回路装置

【課題】配線層間膜の平坦化を行いながら、クラックの伝搬と配線層間膜の剥がれを抑制することを目的とする。

【解決手段】電極パッド113形成領域の、低誘電率膜より誘電率の高い配線層間膜からなる多層配線層領域において、ダミービアを形成しないことにより、配線層間膜の平坦化を行いながら、クラックの伝搬と配線層間膜の剥がれを抑制することができる。

(もっと読む)

半導体装置ならびにその製造方法

【課題】半導体ウエハ同士を接合させてなる構造体を提供する。

【解決手段】 複数の半導体ウエハを貫通するビアを形成する。ただしウエハを積層する前に各チップを検査し、不良チップが発見された場合は、ビアランドと貫通ビアが電気的に接続することがないように、予め、薬液その他の手段を用いて、ビアランドの一部を除去する。その上で、半導体ウエハ同士を積層する。さらに、貫通ビアを接合面と反対側の面より形成する。ビアランドの一部を除去した結果、貫通ビアと不良チップとは、電気的に接続されていないような構成をとることが可能となる。

(もっと読む)

半導体装置

【課題】絶縁耐量を改善することができる半導体装置を得る。

【解決手段】Si基板10(基板)上にゲート抵抗7(下配線)が設けられている。ゲート抵抗7を層間絶縁膜12が覆っている。層間絶縁膜12上に、互いに分離したアルミ配線5a,5b(第1及び第2の上配線)が設けられている。アルミ配線5a,5bを半絶縁性の保護膜4が覆っている。ゲート抵抗7の直上であってアルミ配線5aとアルミ配線5bとの間の領域に、保護膜4が設けられていない。

(もっと読む)

半導体装置

【課題】LSIチップの製造コストを低減することが可能な半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板に形成され、第1の電源配線を含む第1の電源配線層を備える複数のLSI領域と、前記半導体基板に形成された第1の電源端子と、前記LSI領域の間のダイシングライン領域に、前記LSI領域と前記ダイシングライン領域とを区画するダイシングラインに沿って形成され、前記第1の電源配線と前記第1の電源端子とを電気的に接続する第2の電源配線を含む第2の電源配線層と、を備える。少なくとも前記LSI領域において、前記第1の電源配線と前記第2の電源配線との境界にバリアメタル膜が形成されている。

(もっと読む)

半導体装置

【課題】第1の半導体集積回路と第2の半導体集積回路とをフリップチップ工法で1つの基板上に搭載して半導体装置とする場合に、第1の半導体集積回路のパッド列を複数段としながら、第1の半導体集積回路から第2の半導体集積回路への配線をビアを介さずに行い得るようにする。

【解決手段】第1の半導体集積回路32と第2の半導体集積回路33とが基板31上に配置される。前記第1の半導体集積回路32には、その辺方向に延びる外側パッド列34Rが備えられる。また、前記第1の半導体集積回路32の外側パッド列34Rの内方には、前記外側パッド列34Rと並行に延びる内側パッド列35が備えられる。前記外側パッド列34Rのうち、前記内側パッド列35に対向する部分のパッド列34Raは、前記基板31に配置された金属配線36により、前記第2の半導体集積回路33の各パッド33aに電気的に接続される。

(もっと読む)

半導体装置と制御手段とを備えるシステム、及び、半導体装置を流れる電流の制御方法

【課題】メイン素子に流れる電流に応じて適切に半導体装置を制御することができる技術を提供する。

【解決手段】半導体装置と制御手段とを備えるシステム。半導体装置の半導体基板には、メイン素子と、第1検出素子と第2検出素子が形成されている。制御手段は、第1検出素子の電流密度Id1と、第2検出素子の電流密度Id2と、係数K1と、係数K2から、Im=K1Id1+K2Id2の数式により得られる値Imに基づいて半導体装置を流れる電流を制御する。半導体装置を動作させたときに、メイン素子が形成されている領域の中で、第1検出素子の温度に近い温度となる領域の面積が面積SHであり、第2検出素子の温度に近い温度となる領域の面積が面積SLである。係数K1と係数K2の比K1/K2が、面積SHと面積SLの比SH/SLと略等しい。

(もっと読む)

半導体装置

【課題】パッケージ応力に起因する回路部品の電気特性変動のバラツキによって出力信号が変動する内部回路について、パッケージ応力に起因する出力信号の変動を防止する。

【解決手段】半導体チップ5に形成された内部回路はその回路を構成する複数の回路部品の電気特性の変動のバラツキによって出力信号が変動するものである。チップタブ3の平面サイズは半導体チップ5の平面サイズよりも小さい。上方から見てチップタブ3の配置位置の全部が半導体チップ5の配置位置と重なっている。さらに、封止樹脂13に起因して半導体チップ5に加わる応力の大きさがチップタブ3上で均一になる位置関係でチップタブ3の周縁と上記半導体チップ5の周縁は間隔をもって配置されている。上記回路部品は半導体チップ5内部で上記チップタブ3上に配置されている。

(もっと読む)

無線通信デバイス、受動素子の製造方法、及び無線通信機器

【課題】高周波回路のワンチップ化を実現し、上層回路と下層回路との間におけるアイソレーション特性を向上し、かつ量産性の高い無線通信デバイスを提供する。

【解決手段】RFICと、キャパシタ32と、インダクタ24とが積層配置され、キャパシタ32の少なくとも一部がRFICとインダクタ24との間に位置するようにして前記RFICに対して積層して実装される受動素子チップ12と、を備えることを特徴とする。このような特徴を有する無線通信デバイスでは、受動素子チップ12は、キャパシタ32の上部電極26を構成する金属パターンとインダクタ24を構成する金属パターンとを横並びに備え、キャパシタ32の下部電極を構成する下層金属パターン18をインダクタ24を構成する金属パターンの下部にまで延設して構成すると良い。

(もっと読む)

半導体装置

【課題】半導体素子が短絡破壊したとき、ヒューズを設けることなく、主電流を遮断できる半導体装置を提供すること。

【解決手段】半導体装置100を構成するパワー半導体素子を小さな半導体素子1に分割し、この小さな半導体素子1にそれぞれ1本のボンディングワイヤ17を接続する。小さな半導体素子1が短絡破壊したとき、破壊した小さな半導体素子1に接続するワイヤ17(ヒューズの役割をさせる)を溶断し、且つ、制御回路30からオフ信号を健全な半導体素子1に与える。このようにして、半導体装置100が短絡破壊したとき、ヒューズを設けることなく、主電流を遮断することができる。

(もっと読む)

半導体装置及びそのレイアウト方法

【課題】再配線層形成工程、メタルポスト形成工程及び樹脂封止工程を経てウェハレベルで樹脂封止される半導体装置について、パッケージング工程で発生する応力を利用してPMOSFETの電流駆動能力を制御する。

【解決手段】メタルポスト21の形成に起因して半導体基板に圧縮応力が生じる範囲内にPMOSFET31が配置されている。PMOSFET31はそのチャネル方向がメタルポスト23の配置範囲の重心O及びPMOSFET31のチャネル領域の配置範囲の重心Gを通る直線と直交する向きに配置されている。重心Gで、メタルポスト21の形成に起因して半導体基板に生じる圧縮応力は、重心Gの位置で、重心Gと中心Oを通る直線に直交する方向に印加される。重心Gでの圧縮応力の方向とPMOSFET31のチャネル方向は一致するので、PMOSFET31の電流駆動能力は、当該圧縮応力が印加されない場合に比べて向上する。

(もっと読む)

半導体装置

【課題】複数の半導体チップの各々の信号端子が共通の外部端子に接続される場合であっても、半導体装置のオープン不良を検出する。

【解決手段】半導体装置は、複数の半導体チップと、外部と接続される電源端子、第1及び第2の外部端子と、を備え、複数の半導体チップのそれぞれは、第1の信号端子(第1の信号パッドT1)に供給される信号に基づくクロック信号によって計数を行うカウンタ部42と、複数の半導体チップの中で自己の半導体チップを固定的に識別し、識別情報を出力する識別情報認識部と、カウンタ部42の出力と識別情報を比較し、比較した比較結果に基づいて、第2の信号端子(第2の信号パッドT2)と電源端子との導通/非導通状態を制御する比較回路43と、を有し、複数の半導体チップの各々の第1の信号端子は、共通の第1の外部端子に接続され、複数の半導体チップの各々の第2の信号端子は、共通の第2の外部端子に接続される。

(もっと読む)

I/O積層体を含むシステム及びこのシステムを製造する方法

【課題】入出力(I/O)積層体を含むシステムを提供する。

【解決手段】入出力(I/O)積層体を含むシステム及びこのシステムを製造する方法が記述されている。一実装において、本方法は、I/O素子を含むと共に論理素子を含まないI/Oダイを積層するステップを有する。又、一実装において、本方法は、I/Oダイに対して集積回路ダイを積層するステップを更に含む。集積回路は、論理素子を含み、且つ、I/O素子を含まない。集積回路ダイからI/Oダイを分離することにより、それぞれのダイの独立的な開発や従来のダイのものとの比較におけるI/OダイのI/O基板上のI/O素子用の相対的に大きな空間などの様々な利益が得られる。空間の増大により、多数の論理素子を集積回路ダイの基板の同一の表面積内に収容する集積回路ダイの新しいプロセス世代が可能となる。

(もっと読む)

半導体装置

【課題】小型化、薄型化、軽量化を実現した半導体装置の提供を課題とする。また、作製時間を短縮し、歩留まりを向上することができる半導体装置の作製方法の提供を課題とする。

【解決手段】トランジスタと、トランジスタ上に設けられた絶縁層と、絶縁層に設けられた開口部を介して、トランジスタのソース領域又はドレイン領域に電気的に接続された第1の導電層(ソース配線又はドレイン配線に相当)と、絶縁層及び第1の導電層上に設けられた第1の樹脂層と、第1の樹脂層に設けられた開口部を介して、第1の導電層に電気的に接続された導電性粒子を含む層と、第2の樹脂層及びアンテナとして機能する第2の導電層が設けられた基板とを有する。上記構成の半導体装置において、第2の導電層は、導電性粒子を含む層を介して、第1の導電層に電気的に接続されている。また、第2の樹脂層は、第1の樹脂層上に設けられている。

(もっと読む)

半導体装置、及びその製造方法

【課題】ピラーを確実に配置することが可能な半導体装置、及びその製造方法を提供する。

【解決手段】本発明の一態様にかかる半導体装置30は、内部回路領域20と、内部回路領域20の外側に設けられたI/O領域10と、を備える半導体チップ1と、半導体チップ1とフリップチップ接続されたパッケージ基板6と、半導体チップ1とパッケージ基板6との間に配置され、半導体チップ1の最上層配線層12に含まれる2本以上の接地配線12a上に形成されて、2本以上の接地配線12aを接続する導電性のピラー4と、を備えるものである。

(もっと読む)

多チップモジュール用ESD回路を含む集積回路及びその方法

【課題】集積回路の多チップモジュールの静電放電保護に関する。

【解決手段】ESD損傷から保護されたりされなかったりするI/O回路を含む集積回路を提供する。ESD損傷からの保護は、I/O回路の1つまたはそれ以上において、選択的に非作動にされたり、作動されたり、少しも存在しなくなったりする。使用時、集積回路は、他の集積回路に接続されて多チップモジュールを形成し、そこで、モジュール間のI/O回路のESD保護が非作動にされるかまたは存在しなくなる。これは、多チップモジュールが形成されると、このI/O回路へのESD損傷の見込みが減るので好都合である。蒸気の包括的な説明と以下の詳細な説明は共に、本発明の模範的なものであって制限的なものではないことが理解されるべきである。

(もっと読む)

61 - 80 / 1,173

[ Back to top ]