Fターム[5F038BE07]の内容

Fターム[5F038BE07]に分類される特許

81 - 100 / 1,173

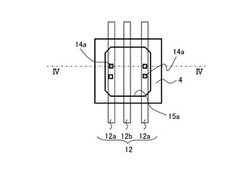

半導体装置、及びその製造方法

【課題】ピラーを確実に配置することが可能な半導体装置、及びその製造方法を提供する。

【解決手段】本発明の一態様にかかる半導体装置30は、内部回路領域20と、内部回路領域20の外側に設けられたI/O領域10と、を備える半導体チップ1と、半導体チップ1とフリップチップ接続されたパッケージ基板6と、半導体チップ1とパッケージ基板6との間に配置され、半導体チップ1の最上層配線層12に含まれる2本以上の接地配線12a上に形成されて、2本以上の接地配線12aを接続する導電性のピラー4と、を備えるものである。

(もっと読む)

半導体装置

【課題】隣接する2つのトランジスタ同士が接続された構成を有し、省スペースと電流集中による信頼性の低下の抑制とを両立させた半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1のトランジスタ101と接続された第1のバス111、第2のトランジスタ102と接続された第2のバス112と、第1のバス111と第2のバス112との間に形成され、第1のバス111と第2のバス112とを接続するバス間配線121とを備えている。バス間配線121は、第1のバス111における第2のバス112と対向する辺の一部及び第2のバス112における第1のバス111と対向する辺の一部と接続されている。第1のコンタクトパッド131は、第1のバス111の一部と接続され、第2のコンタクトパッド132は、第2のバス112の一部と接続されている。

(もっと読む)

半導体装置

【課題】マルチフィンガーFETセル内のループ発振を抑制させ、かつチップ面積の増大を抑制する。

【解決手段】ユニットフィンガーの並列接続からなるマルチフィンガー単位FETセルと、マルチフィンガー単位FETセルのゲートフィンガーを並列接続する指定ゲートバスラインと、指定ゲートバスラインに接続されたゲート引き出しラインとを備え、ゲート引き出しラインと指定ゲートバスラインの接続点をマルチフィンガー単位FETセル内の中心からずらすことによって、接続点の一方に接続されたゲートフィンガー数が、他方に接続されたゲートフィンガー数よりも多くする。

(もっと読む)

半導体装置および半導体集積回路の設計方法

【課題】本発明は、半導体集積回路を備えた半導体装置および半導体集積回路の設計方法に関し、IO領域を有効に利用しつつパッケージの高さ寸法の増大を有効に抑えた接続を可能とする。

【解決手段】半導体基板の表面の第1の辺に沿って、第1のIOセルと、第2のIOセルとを交互に配置したIO領域を有し、第1のIOセルは、第1の辺から所定の距離の位置に配置されたボンディングパッドを有し、第2のIOセルは、第1のIOセルのボンディングパッドより第1の辺から遠い位置にボンディングパッドを有し、かつ、第1のIOセルの少なくとも1つは、第1の辺から所定の距離の位置に配置された第1のボンディングパッドに加えて、第2のIOセルのボンディングパッドより第1の辺から遠い位置に、第2のボンディングパッドを有する第3のIOセルに置きかえられている。

(もっと読む)

半導体装置

【課題】実装上の自由度を低下させることのない螺旋状インダクタを実現する技術を提供する。

【解決手段】半導体装置100は、実質的に平行に配置された第1半導体基板1及び第2半導体基板2と、第1半導体基板1の第2半導体基板2に対向する面である第1対向面1aに形成され、相互に略平行となる複数の第1パターン3と、第2半導体基板2の第1半導体基板1に対向する面である第2対向面2aに形成され、相互に略平行となる複数の第2パターン4と、複数の第1パターン3と複数の第2パターン4を交互に導通させることで螺旋状インダクタLを形成する複数のバンプ電極5と、を備える。

(もっと読む)

ナノ物体を外部電気システムに接続する素子、及びその素子を作る方法

【課題】ナノ物体を外部電気システムに接続する素子、及びその素子を作る方法を提供する。

【解決手段】特に分子の特性評価に適用される本発明によると、以下を備える素子が作られる:ナノ物体(2)に接続される上部接触パッド(8)を備えた上部層(16);外部電気システム(4)に接続される下部接触パッド(12)を備えた下部層(18);前記下部層上にあり、前記下部パッドと接触する電気的貫通ビア(22)を備えた接着層(20);前記接着層と前記上部層の間にあり、前記上部パッドを前記下部パッドに接続するための導電ライン(25)及び電気的ビア(26)を備えた少なくとも2つの層(22、24)。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極の電界集中を緩和して耐圧の更なる向上を実現することに加え、デバイス動作速度を向上させ、アバランシェ耐量が大きく、サージに対して強く、例えばインバータ回路等に適用する場合に外部のダイオードを接続することを要せず、ホールが発生しても安定動作を得ることができる信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成されたフィールドプレート用リセス2Dをp型半導体で埋め込み、化合物半導体積層構造2とp型半導体層8aで接触するフィールドプレート8を形成する。

(もっと読む)

半導体装置

【課題】キャパシタ構造の信号線およびGND電極を抵抗成分やインダクタンス成分を最小限にできる構造の配線基板を有する半導体装置を提供する。

【解決手段】信号線の一部を構成する中心導体2cの周囲に誘電体2bを介して同心円状にシールド線を構成する外側導体2aを備えるキャパシタ構造部2を有した構成とする。そして、2つのスルーホール3内に設けた各キャパシタ構造部2の中心導体2cについては、配線基板の表面側で各中心導体2cが上面配線5に電気的に接続され、裏面側でもう一方のキャパシタ構造部2の中心導体2cと第1下面配線6を介して電気的に接続され、さらに、各キャパシタ構造部2の外側導体2aについては、配線基板の裏面側に全面に一様に形成された第2下面配線7で覆われた状態で電気的に接続されるようにする。

(もっと読む)

電子回路

【課題】簡易な構成でありながら正確に同期したクロックを各基板に分配することができる電子回路を提供すること。

【解決手段】第1コイルL1と第1キャパシタC1による第1共振回路を含む第1発振器21を有する第1基板11と、第2コイルL2と第2キャパシタC2による第2共振回路を含む第2発振器22を有する第2基板12とを備え、前記第1コイルL1と第2コイルL2が誘導結合して前記第1発振器21と第2発振器22が結合共振することを特徴とする電子回路。

(もっと読む)

半導体集積回路

【課題】内側のセル列と外側のセル列とでセルの形状が同じ場合において、内側のセル列におけるセルの配列ピッチを外側のセル列におけるセルの配列ピッチより大きくしなくても外側のセル列のセルに接続される配線のための領域を確保することができる。

【解決手段】半導体集積回路は、半導体チップの外周11に沿って配置される複数の第1セル40と、複数の第1セル40の内側で外周11に沿って配置される複数の第2セル40とを具備する。複数の第1セル40及び複数の第2セル40は同一の長方形形状に形成される。複数の第1セル40のそれぞれの長辺4aは外周11に平行である。複数の第2セル40のそれぞれの長辺4aは外周11に垂直である。

(もっと読む)

垂直集積システム

【課題】コストのかかる空間をとらずに電子部品内に個別パッシブ部品を組み込むことが可能な垂直集積システムを提供する。

【解決手段】集積回路システム100は、半導体ダイ110の前面上に製造された第一のアクティブ層と、半導体ダイ110の裏面上の第二の予め製造された層とを含み、その第二の予め製造された層は、その中に埋め込まれた電気部品を有し、その電子部品は、少なくとも一つの個別パッシブ部品140を含む。また、集積システム100は、第一のアクティブ層及び第二の予め製造された層を結合する少なくとも一つの電気経路150も含む。

(もっと読む)

半導体装置

【課題】規格により規定された速度による信号の転送を実現し、半導体装置やそれを内蔵した電子機器の誤動作を防止する。

【解決手段】第1の半導体素子101の導体配線層106に、パッケージ基板100の信号端子103と第2の半導体素子102の信号端子117とを接続する信号線導体113aと、パッケージ基板100の電源端子104と第2の半導体素子102の電源端子118とを接続する電源導体114とを、信号線導体113aが導体配線層106において、信号線導体113aとの間に水平方向に一定の間隔をあけて隣接する電源導体114に挟まれるように形成する。

(もっと読む)

半導体集積回路及びその制御方法

【課題】積層されたチップの面積を効率的に使用し、リペア動作のための非同期パラメータを減少させることができるようにした半導体集積回路及びその制御方法を提供する。

【解決手段】半導体集積回路100は、マスターチップである第1チップ及び第1チップに積層されたスレーブチップである第2チップを備え、第2チップに第1メモリ領域BK0〜BK7が形成されるとともに、第1チップに前記第1メモリ領域の不良をリペアするための第2メモリ領域BK0SRAM〜BK7SRAMが形成される。

(もっと読む)

集積回路および中継基板

【課題】本発明は、マイクロ波帯やミリ波帯において、1つの集積回路で複数の機能を実現する集積回路と、その集積回路が表面実装される中継基板とに関し、特性の劣化の原因となる広帯域設計をすることなく、多様に異なる帯域に柔軟に対応可能とすることを目的とする。

【解決手段】基板上に個別に形成された複数の回路と、前記基板上で前記複数の回路に隔たって形成され、前記複数の回路の何れにも接続され得る特定の回路とを備え、前記特定の回路と前記複数の回路とは、表面実装型の中継基板との突起電極を介する接続に供されるパッドを有する。

(もっと読む)

半導体回路、半導体装置、及び電池監視システム

【課題】過大電流による素子の破壊を防止することができる、半導体回路、半導体装置、及び電池監視システムを提供する。

【解決手段】短絡保護回路30のPMOSトランジスタMP3により短絡状態の場合は、電源電圧VDDからFETゲート電圧出力端子FET_PAD(外部FET0)に電流が流れる経路をPMOSトランジスタMP0及び短絡電流検出用抵抗素子R0を経由する経路から、PMOSトランジスタMP1及び抵抗素子Rpuを経由する抵抗値が大きい経路に切り替えるため、短絡電流を制限することができ、従って、短絡により、電池監視IC14が破壊されるのを防止することができる。

(もっと読む)

半導体装置

【課題】兼用パッドのサイズを専用パッドよりも大きくするとともに、半導体装置のサイズ増大を抑制する。

【解決手段】半導体装置は、第1の方向に延伸された第1のエッジE1と、第1の方向と実質的に直交する第2の方向に延伸された第2のエッジE2とを含む半導体チップ10と、半導体チップ上に形成され、互いに第2の方向に沿った長さが実質的に等しい複数の第1グループパッドGP1と、半導体チップ上に形成され、第2の方向に沿った長さが、複数の第1グループパッドの第2の方向に沿った長さよりも長い、第2グループパッドGP2と、を備える。複数の第1グループパッドと第2グループパッドとは、第2グループパッドと第2のエッジとの間に複数の第1グループパッドのいずれをも含まずに、第1の方向に沿って一列に並んで配置されている。

(もっと読む)

高性能サブシステムの設計および組立体

【課題】ESD保護回路および入出力回路を持たない構造の集積回路チップ間のチップ間通信を行う多重集積回路チップ構造を提供する。

【解決手段】多重集積回路チップ構造は、テストおよびバーン・イン手順中に外部テスト・システムと通信するためのESD保護回路387および入出力回路389を有するインターフェース回路385をテストするため集積回路の内部回路を選択的に接続するチップ間インターフェース回路360を有する。多重配線集積回路チップ構造は、集積回路チップを相互に物理的かつ電気的に接続するため1つ以上の第2の集積回路チップ310へ取付けられた第1の集積回路チップ305を有する。

(もっと読む)

半導体装置

【課題】電源ノイズを一層効果的に解消する技術を提供する。

【解決手段】半導体装置1は、所定動作を実行するための内部回路6と、内部回路6に対して高電位電圧を供給するための電源ライン7と、内部回路6に対して低電位電圧を供給するためのグラウンドライン8と、ウェハテスト用電極パッド9と、ウェハテスト用電極パッド9を内部回路6に接続するための電気線10と、電気線10を内部回路6に対して非導通状態にすると共に、電気線10を電源ライン7とグラウンドライン8のうち何れか一方に対して選択的に導通状態とする接続切替部11と、を備える。

(もっと読む)

高周波半導体モジュール

【課題】段間の整合状態を観測して整合回路の調整を行うことのできる高周波半導体モジュールを提供する。

【解決手段】複数の半導体増幅素子7、8を直列に接続して増幅を行う多段型の高周波半導体モジュールであって、パッケージ3内に配置される回路基板4、5,6に、半導体増幅素子7、8間の段間における高周波信号をモニタするためのモニタ回路を具備する。

(もっと読む)

半導体装置

【課題】大量生産が可能で、かつ従来の小型素子とは異なる構造を有する半導体装置を提供する。また、強度を向上させることが可能であり、作製段階における素子の破壊を抑制することができ、信頼性及び歩留まりの高い半導体装置の構造、及び半導体装置の作製方法を提供することを目的としている。

【解決手段】集積回路を有する層と、集積回路を有する層上に形成され、集積回路を有する層と電気的に接続された第1の端子と、第1の端子上に形成され、第1の端子と電気的に接続されたアンテナとして機能する導電層と、集積回路を有する層上に形成され、集積回路を有する層と、アンテナとして機能する導電層と、第1の端子と電気的に接続されていない第2の端子を有する。

(もっと読む)

81 - 100 / 1,173

[ Back to top ]