Fターム[5F038BH05]の内容

Fターム[5F038BH05]に分類される特許

81 - 100 / 639

増幅回路装置

【課題】意図しない低周波信号の入力を防止することにより、規格値を超過するドレイン電流を発生することを回避できる接合形電界効果トランジスタを用いた増幅回路装置を提供する。

【解決手段】J−FET1の封止部材内で、ゲートと直列に容量を付加し、当該容量とJ−FET1のゲート−ソース間に接続される抵抗2とによってハイパスフィルタ5を構成する。ハイパスフィルタ5の遮断周波数を20Hz未満に設定することで、音声信号を低下させることなく、可聴周波数帯の下限より低い周波数を遮断できる。チップを構成する基板の裏面にイオン注入によりn型不純物層を設け、p+型半導体基板とpn接合を形成して接合容量をハイパスフィルタ5の容量4とする。

(もっと読む)

半導体装置

【課題】安定した静電気保護機能を有する半導体装置を提供すること。

【解決手段】半導体装置は、シリコン柱を有するシリコン基板、シリコン柱の側壁に沿って形成されたゲート電極、ゲート電極とシリコン柱との間に形成されたゲート絶縁膜シリコン柱の上部に形成された上部拡散層、及びシリコン基板において上部拡散層より下方に形成された下部拡散層、を有する縦型MOSトランジスタと、下部拡散層と電気的に接続されたパッドと、を備える。サージ電圧が印加された際に下部拡散層と基板との間においてブレイクダウンが発生する。

(もっと読む)

半導体装置

【課題】小さな面積で電源端子との間に保護素子が設けられていないオープンドレイン信号端子のESD保護を図る半導体装置を提供する。

【解決手段】第1導電型ウェルの表面にソースが第2の電源に接続され、ドレインがオープンドレイン信号端子に接続された第2導電型MISトランジスタを設ける。MISトランジスタの電流が流れる方向と並行にMISトランジスタの両側に第2導電型の第1領域を設け、オープンドレイン信号端子に接続する。その全体を第2の電源に接続された第1導電型ガードリングで囲い、さらにその外側を第1の電源に接続された第2導電型ガードリングで囲う。

(もっと読む)

集積回路装置、電気光学装置及び電子機器

【課題】 静電気を集積回路装置の特定の端子に誘導し、さらに静電気が誘導される端子を含む特定の出力セルのみで静電気耐圧を強化することで大多数の入出力セルのサイズを小さくすること。

【解決手段】 電気光学装置200は、電気光学パネル100と、それを駆動する集積回路装置1とを含む。電気光学パネルは、第1基体110に形成された複数のセグメント電極112と、第2基体120に形成された共通電極122とを含む。集積回路装置は、複数のセグメント電極専用端子SEG1〜SEGm−2と、共通電極専用端子TP0,TP1とを含む。電気光学装置200は、複数のセグメント電極と複数のセグメント電極専用端子とをそれぞれ接続する複数の第1配線220と、共通電極と少なくとも一つの共通電極専用端子とを接続する第2配線230とを含み、第2配線のインピーダンスが複数の第1配線の各々のインピーダンスよりも小さい。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタにおいてオフ耐圧及び破壊電流量の双方を高くする。

【解決手段】第2のベース領域116は、ディープウェル112の表層に形成されており、平面視において第1のベース領域114とシンカー110との間に位置している。そして第2のベース領域116は、第1のベース領域114に接続しており、第1のベース領域116よりも不純物濃度が高く、かつ第1のベース領域116よりも深さが浅い。埋込層108は、半導体層106に形成され、上面がディープウェル112及びシンカー110に接しており、ディープウェル112よりも不純物濃度が高い。

(もっと読む)

半導体集積回路装置

【課題】デジタル回路からアナログ回路へのノイズの混入を十分に抑圧する半導体集積回路装置を提供することを目的とする。

【解決手段】デジタル回路を形成するデジタル回路領域13と、アナログ回路を形成するアナログ回路領域12とに分離し、アナログ回路領域を、アナログ回路の能動素子を形成する能動素子領域12aと、アナログ回路の受動素子を形成する受動素子領域12b,12cとに分離し、受動素子領域12b,12cをデジタル回路領域13と隣り合う領域に配置し、能動素子領域12aをデジタル回路領域13から離れた領域に配置した半導体集積回路装置において、受動素子領域12b,12cの半導体基板20に半導体基板の導電型と異なる第1導電型の第1ウェル21を形成し、第1ウェル21内に第1ウェルの第1導電型と異なる第2導電型の第2ウェル22を形成し、第2ウェル22上に素子分離膜23を介在させて受動素子を配設した。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】小さいサイズでラッチアップの発生を防止できる半導体装置を提供する。

【解決手段】第1導電型の半導体基板1と、前記半導体基板内に形成された第1導電型の第1ウェル領域4と、前記半導体基板内に形成され、第1ウェル領域と隣り合う領域に配置された第2導電型のエピタキシャル領域2と、前記エピタキシャル領域内下方の領域に形成され、前記エピタキシャル領域よりも不純物濃度が高い第2導電型の埋め込み領域6と、第1ウェル領域と前記エピタキシャル領域及び前記埋め込み領域との境界に形成されたトレンチ8と、第1ウェル領域上に形成され、第2導電型のソース及びドレイン領域を有する第1半導体素子と、前記エピタキシャル領域上に形成され、第1導電型のソース及びドレイン領域を有する第2半導体素子と、を備える。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

内部回路と静電保護回路を具備する半導体集積回路

【課題】電源電圧の分離数や接地電圧の分離数の増大により静電保護回路の回路数もしくは静電保護素子数の増大を軽減する。

【解決手段】半導体集積回路1は、第1と第2と第3の動作電圧供給端子21、22、23と、第1と第2と第3の内部回路11、12、13と、第1と第2と第3の静電保護回路41、42、43と、接続中Cdとを具備する。第1と第2と第3の内部回路11、12、13は、第1と第2と第3の動作電圧供給端子21、22、23の第1と第2と第3の動作電圧でそれぞれ動作する。第1と第2と第3の静電保護回路41、42、43は、第1と第2と第3の動作電圧供給端子21、22、23と接続中点Cdの間にそれぞれ接続される。すなわち、第1と第2と第3の静電保護回路41、42、43は、従来のΔ(デルタ)接続ではなく、接続中点Cdに関してY(スター)接続される。

(もっと読む)

半導体装置及びその製造方法

【課題】低容量保護ダイオードを採用した静電破壊防止用保護ダイオードからなる半導体装置において、半導体基板の表面に電圧制限素子としてのツェナーダイオード形成のための占有面積を不要とする。

【解決手段】P+型半導体基板1にP+型埋め込み拡散層1bを形成する。次に、その上をノンドープの第1エピタキシャル層4aで被覆する。次に、該第1エピタキシャル層4a上にN型の高比抵抗の第2エピタキシャル層4bを形成する。該第2エピタキシャル層4bをP+分離層6で第1保護ダイオード形成領域50と第2保護ダイオード形成領域51に分離する。第1保護ダイオード形成領域50の第1エピタキシャル層4aの表面から第1エピタキシャル層4a及び第2エピタキシャル層4bに延在するN+型埋め込み層2等を形成する。P+型埋め込み拡散層1bから延在するP+型這い上がり層1cとN+型埋め込み層2でツェナーダイオードTD等を形成する。

(もっと読む)

半導体集積回路装置

【課題】ESD保護回路を備え外部端子数を効率よく配置できる半導体集積回路装置を提供する。

【解決手段】第1、第2電源電圧を供給する第1、第2電源パッドに対応した第1、第2電源セル、第1信号パッドに対応した入出力セル、第1電源電圧を供給する第1電源線、第2電源電圧を供給する第2電源線を有する。入出力セルは、信号入出力を行う回路、静電保護回路及び第1電源線と第2電源線との間に設けられた第1MOSを有する。第1電源セルは、第1電源パッドの正静電気に応答して第1MOSを一時的にオンにさせる時定数回路、第1電源パッドに向かう電流を流す一方向性素子を有する。第2電源セルは、第2電源パッドの正静電気に応答して第1MOSを一時的にオンにさせる時定数回路、第2電源パッドに向かう電流を流す一方向性素子を有する。第1MOSのゲートとウェルは時定数回路と接続される。

(もっと読む)

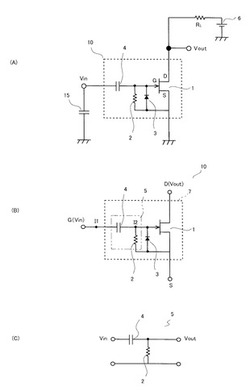

疑似ダイオードを有するIII族窒化物スイッチングデバイス

【課題】ダイオード機能を有するGaN−HEMTのようなIII族窒化物トランジスタを提供する。

【解決手段】GaNスイッチングデバイスは、低しきい値のGaNトランジスタ346の両端間に結合された高しきい値のGaNトランジスタ340を有しており、この低しきい値のGaNトランジスタ346が逆方向モードで並列ダイオードとして機能するようになっている。高しきい値のGaNトランジスタ340は、順方向モードの際にGaNスイッチングデバイスに対し雑音排除性を提供するように構成されている。互いに著しく異なるしきい値を有するようにする。その結果、従来のシリコンFETにおける固有のボディダイオードの機能及びモノリシック構造を維持したまま、III族窒化物スイッチングデバイスの優れたスイッチング特性を利用することができるようになる。

(もっと読む)

半導体装置

【課題】ダイオードセルを有する半導体装置において、ダイオードセルに隣り合う標準セルについて、光近接効果によるゲート長のばらつきを確実に抑制できるレイアウトを提供する。

【解決手段】標準セルC1は、Y方向に延び、X方向に同一ピッチで配置されたゲートパターンG1,G2,G3を有する。ダイオードセルC2は標準セルC1にY方向において隣り合っている。ゲートパターンG1,G2,G3は、各終端部e1,e2,e3がY方向において同じ位置にあり、X方向における幅が同一である。ダイオードセルC2は、ダイオードとして機能する拡散層D1〜D10に加えて、標準セルC1のゲートパターンG1,G2,G3の終端部e1,e2,e3に対向するように配置された、ゲートパターンG4,G5,G6からなる複数の対向終端部eo1,eo2,eo3を備えている。

(もっと読む)

半導体装置の製造方法

【課題】FEOLにおいても半導体装置のチャージングを効果的に抑制できるようにする。

【解決手段】半導体装置の製造方法は、半導体基板101の上に、被保護素子のゲート絶縁膜となる第1の絶縁膜122を形成する工程(a)と、保護素子部302において第1の絶縁膜122の少なくとも一部を除去する工程(b)と、工程(b)よりも後に、被保護素子部301において第1の絶縁膜122の表面を窒化する工程(c)と、工程(c)よりも後に、被保護素子部301及び保護素子部302の上に跨るように導電膜を選択的に形成することにより、互いに接続された被保護素子のゲート電極141及び保護素子の電極142を形成する工程(d)とを備えている。

(もっと読む)

DC/DCコンバータ用半導体装置

【課題】半導体装置の電源電圧の変換効率を向上させる。

【解決手段】ハイサイドスイッチ用のパワーMOS・FETとローサイドスイッチ用のパワーMOS・FETとが直列に接続された回路を有する非絶縁型DC−DCコンバータにおいて、ローサイドスイッチ用のパワーMOS・FETと、そのローサイドスイッチ用のパワーMOS・FETに並列に接続されるショットキーバリアダイオードD1とを同一の半導体チップ5b内に形成した。ショットキーバリアダイオードD1の形成領域SDRを半導体チップ5bの短方向の中央に配置し、その両側にローサイドのパワーMOS・FETの形成領域を配置した。また、半導体チップ5bの主面の両長辺近傍のゲートフィンガ6aから中央のショットキーバリアダイオードD1の形成領域SDRに向かって、その形成領域SDRを挟み込むように複数本のゲートフィンガ6bを延在配置した。

(もっと読む)

半導体装置

【課題】片面2電極ダイオードにおいて、トレンチ型絶縁層を設けることで、素子分離領域を形成するより、電流が流れるpn接合部の面積を大きくし、かつ横方向に電流が流れないようにすることで、pn接合部の湾曲部(突端部)に集中することを防ぐことができる。また、他電極(直下にpn接合が存在しない方の電極)を高濃度の埋め込み層と接続することで、電流経路に低抵抗層を作り、電流集中が発生しても、破壊が起きにくくなり、それにより、ESD耐量を改善することが可能となる。

【解決手段】本発明にかかる半導体装置は、アノード領域と、カソード領域と、チップ表面のp層とn層間に形成したトレンチ型絶縁層を有する。

(もっと読む)

静電気保護回路及び集積回路

【課題】静電気保護用の抵抗を使用せずに静電気放電から保護することのできる静電気保護回路及び集積回路を提供する。

【解決手段】端子P1が複数のトランジスター21に接続され、端子P2が入出力パッドに接続されており、所定範囲のレベルの電気信号に対して端子P1と端子P2との間を通すトランスミッションゲート10Aを備え、トランスミッションゲート10Aは、前記所定範囲外のレベルの電気信号を前記所定範囲のレベルの電気信号に変更可能なクランプダイオード14Aを有する。

(もっと読む)

半導体装置

【課題】 工程の増加や占有面積の増加もなくオフリーク電流を小さく抑えた、十分なESD保護機能を持たせたシャロートレンチ分離構造を有するESD保護用のN型のMOSトランジスタを有する半導体装置を提供する。

【解決手段】 素子分離にシャロートレンチ分離領域501を有するESD保護用のN型MOSトランジスタにおいて、ESD保護用のN型MOSトランジスタのゲート電極301下面のゲート絶縁膜を介してP型シリコン基板表面に形成されたチャネル領域の表面に、ESD保護用のN型MOSトランジスタのドレイン領域202から一定の距離を隔てたオフセット領域601を介して、濃いP型の不純物濃度領域からなるP型ブレークダウン領域401を形成した半導体装置とした。

(もっと読む)

半導体集積回路

【課題】隣接する端子間にサージ電圧が印加された場合に、隣接する端子の間に接続された回路素子をサージ電圧による静電破壊から保護する。

【解決手段】半導体集積回路100は、端子P0〜P14、ダイオード接続されたMOSトランジスタMN0〜MN15、保護ダイオード回路HD0〜HD14、電池放電用MOSトランジスタT1〜T14、電池電圧検出制御回路10及び過電圧保護用のクランプ回路20を含んで構成される。そして、電池放電用MOSトランジスタT1〜T14は、端子P0〜P14の隣接する各端子間にそれぞれ接続されている。ダイオード接続されたMOSトランジスタMN1〜MN14は、端子P0〜P14の隣接する各端子間にそれぞれ接続される。

(もっと読む)

81 - 100 / 639

[ Back to top ]