Fターム[5F038BH05]の内容

Fターム[5F038BH05]に分類される特許

101 - 120 / 639

半導体集積回路

【課題】隣接する端子間にサージ電圧が印加された場合に、隣接する端子の間に接続された回路素子をサージ電圧による静電破壊から保護すると共に過電圧保護回路の回路規模を削減する。

【解決手段】半導体集積回路200は、端子P0〜P14、ダイオード接続されたMOSトランジスタMN0〜MN15、保護ダイオード回路HD1、HD3、HD5、HD7、HD9、HD11、HD13、電池放電用MOSトランジスタT1〜T14、電池電圧検出制御回路10、ダイオード接続されたMOSトランジスタMP11〜MP17を含んで構成される。ダイオード接続されたMOSトランジスタMN1〜MN14は、端子P0〜P14の隣接する各端子間にそれぞれ接続される。ダイオード接続されたMOSトランジスタMP11〜MP17は、2つのセルに1個ずつ設けられている。

(もっと読む)

半導体集積回路のテスト方法、および、テストシステム

【課題】テスト用のプローブとパッドとの接触を容易にテストすることが可能な半導体集積回路のテスト方法およびテストシステムを提供する。

【解決手段】半導体集積回路のテスト方法は、RF回路のテスト前に、テスト信号を印加するための第1のプローブと第1の信号端子とを接続させ、且つ、テスト信号を印加するための第2のプローブと第2の信号端子とを接続させた状態で、制御端子に印加される制御電圧に応じてMOSトランジスタをオンし、第1のプローブと第2のプローブから交流信号を出力したときの半導体集積回路からの反射波に基づいて、第1のプローブと第1の信号端子との間および第2のプローブと第2の信号端子との間が導通しているか否かを判断する。

(もっと読む)

静電サージ保護回路、DC−DCコンバータ制御回路及びDC−DCコンバータ

【課題】CMOSの微細プロセスに混載可能な高耐圧の静電サージ保護回路、DC−DCコンバータ制御回路及びDC−DCコンバータを提供する。

【解決手段】CMOSと、前記CMOSを構成するトランジスタよりも高耐圧の第1のトランジスタと、が形成された半導体基板をコレクタとして有する第2のトランジスタと、前記第2のトランジスタのベースと前記コレクタとの間に接続され、過電圧によりブレークダウンし前記第2のトランジスタのエミッタ・コレクタ間電圧をクランプするツェナーダイオードと、を備えたことを特徴とする静電サージ保護回路が提供される。

(もっと読む)

半導体装置

【課題】 占有面積の増加がなく、十分なESD保護機能を持たせたESD保護用のN型のMOSトランジスタを有する半導体装置を提供する。

【解決手段】 内部素子のN型MOSトランジスタやその他の内部素子をESDによる破壊から保護するためのESD保護用のN型MOSトランジスタのチャネル領域の下部に、濃いN型の不純物を有するシリコン領域からなる埋め込みN型領域を配置した半導体装置とした。

(もっと読む)

過電圧保護回路

【課題】外部電源が停電(例えば、瞬時停電)した場合であっても、スイッチング素子に印加される過電圧から当該スイッチング素子を保護することの可能な過電圧保護回路の提供。

【解決手段】過電圧保護回路1は、ゲートへ入力される第1指示信号がスイッチング素子S1をオフ状態とする指示信号である場合であっても、スイッチング素子S1のドレインとソースとの間に印加される電圧が予め設定された閾値電圧(ここでは、ツェナーダイオードZ1、Z2のツェナー電圧Vz1,Vz2の和)以上となった場合には、スイッチング素子S1を強制的にオン状態とする切換回路(ここでは、ツェナーダイオードZ1、Z2)を備える。

(もっと読む)

ESD保護回路及びこれを備えた半導体装置

【課題】 低耐圧回路から高耐圧回路までの各回路に対するESD保護機能を有し、しかも小さいレイアウト面積で実現できるESD保護回路を提供する。

【解決手段】 低電圧を出力する電源端子VCC_lに接続するノードNLと接地線の間にESD保護素子13を備え、中間電圧を出力する電源端子VCC_mに接続するノードNMとノードNLの間にESD保護素子12を備え、高電圧を出力する電源端子VCC_hに接続するノードNHとノードNMの間にESD保護素子11を備える。接地線VSSと、ノードNL,NM,NHの各間には、それぞれ低耐圧の被保護素子18,中間耐圧の被保護素子17,高耐圧の被保護素子16が接続される。ESD保護素子11,12,13によって被保護素子16のESD保護を行い、ESD保護素子12,13によって被保護素子17のESD保護を行い、ESD保護素子13によって被保護素子18のESD保護を行う。

(もっと読む)

半導体装置

【課題】異なる電源系統から電源電圧を供給される出力回路と入力回路とを含む半導体装置において、ESDサージ電圧が出力回路を介して入力回路にそのまま印加されることによって入力回路が破壊されることを有効に抑制する。

【解決手段】半導体装置が、第1電源パッド11と、第1接地パッド12と、第1電源線13と、第1接地線14と、出力回路15と、第2電源パッド21と、第2接地パッド22と、第2電源線23と、第2接地線24と、入力回路25と、信号線20と、メインESD保護素子16と、保護ダイオード対D1と、PMOSトランジスタP2とを備えている。出力回路15がPMOSトランジスタP3を含み、入力回路25がNMOSトランジスタN1を含む。PMOSトランジスタP2は、ソースが信号線20に接続され、ドレインが第2接地線24に接続され、ゲートとバックゲートが第2電源線23に接続されている。

(もっと読む)

半導体素子の保護回路

【課題】横方向二重拡散MOSトランジスタ(LDMOS)の特性を悪化させることがなく、回路素子サイズの増大や各素子の製造時のばらつきの影響を抑えることができる、半導体素子の保護回路を提供する。

【解決手段】LDMOS110のバックゲートの出力をトリガーとして用い、LDMOSのドレインに接続される出力端子120に印加されるESDサージを、直列に接続された高耐圧MOS140及び低耐圧MOS142を経て接地端子122に流す。

(もっと読む)

保護素子及び半導体装置

【課題】半導体素子を保護する保護素子を備え、静電破壊が抑制され、信頼性の高い半導体装置を提供する。

【解決手段】半導体装置1は、チャネル層105とキャップ層112とを含む半導体積層体113と、半導体積層体113上に形成された下部電極213と上部電極216とを有する少なくとも1つの半導体素子1Xと、半導体素子1Xと共通の半導体積層体113を有し、半導体素子1Xを保護する少なくとも1つの保護素子1Yとを備えたものである。保護素子1Yは、キャップ層112を厚み方向に貫通するリセス部221と、リセス部221の底面221Bから半導体積層体113内に厚み方向に形成された絶縁領域218Yと、リセス部221を挟んで両側に形成されたキャップ層112に接続された一対のオーミック電極219、220とを備えたものである。

(もっと読む)

ガードリング構造を有する半導体デバイス、ディスプレイドライバ回路、及びディスプレイ装置

【課題】ガードリング構造を有する半導体デバイス、ディスプレイドライバ回路、及びディスプレイ装置を提供する。

【解決手段】本発明による半導体デバイスは、第1導電型の半導体基板と、半導体基板に既定の深さを有して形成された2以上の第2導電型の第1ウェル領域と、第2導電型の第1ウェル領域の内に既定の深さを有して形成された少なくとも一つの第1導電型の第2ウェル領域と、第1ウェル領域の間に位置し、第1ウェル領域と既定の間隔だけ離隔して既定の深さを有して形成された第2導電型のガードリング領域と、を含み、ガードリング領域は、システムグラウンド電圧に連結される。

(もっと読む)

半導体装置

【課題】放電効率の向上と、通常動作時の電位変動の伝達の抑制とを両立させることができる静電気保護素子を有する半導体装置を提供すること。

【解決手段】第1電源電位配線と第1接地電位配線との間にて、電気的に接続された第1回路、及びダイオード接続されたMOSトランジスタを有する第1保護素子と、第2電源電位配線と第2接地電位配線との間にて、電気的に接続された第2回路、及びダイオード接続されたMOSトランジスタを有する第2保護素子と、前記第1接地電位配線と前記第2接地電位配線との間に2つのMOSトランジスタが互いに逆バイアス状態になるように並列にダイオード接続された第3保護素子と、を備え、前記第3保護素子における2つのMOSトランジスタの閾値電圧は、前記第1保護素子及び前記第2保護素子における各MOSトランジスタの閾値電圧よりも大きく設定されている。

(もっと読む)

トレンチ型絶縁ゲート半導体装置及びその製造方法

【課題】トレンチ型絶縁ゲート半導体素子と多結晶シリコンダイオードを同一チップ上に形成して性能を高める。

【解決手段】本発明では、半導体基板上の半導体層の主面に形成されたトレンチ型絶縁ゲート半導体素子のトレンチ溝の外側には、トレンチ溝に連なる多結晶シリコン層を形成する。また、トレンチ溝の外側には、前記トレンチ溝に連なる多結晶シリコン層とは別の多結晶シリコン層が形成され、この多結晶シリコン層には多結晶シリコンダイオードが形成され、そして、この多結晶シリコンダイオードが形成された多結晶シリコン層の膜厚が、前記トレンチ溝に連なる多結晶シリコン層の膜厚よりも薄くなるように形成することを特徴とする。

(もっと読む)

BiCMOSプロセス技術における高電圧SCRMOS

集積回路が、ドレイン領域(1010)及びSCR端子(1012)の周りに、低減された表面フィールド(RESURF)領域(1024)と共に形成されるSCRMOSトランジスタを含む。RESURF領域は、ドリフト領域(1014)と同じ導電型であり、ドリフト領域(1014)より一層重くドープされる。  (もっと読む)

(もっと読む)

BiCMOSプロセス技術における高電圧SCRMOS

集積回路(1000)が、中央配置のドレイン拡散領域(1008)及び分散型SCR端子(1010)を備える1つのドレイン構造(1006)と、分散型ドレイン拡散領域(1016)及びSCR端子(1018)を備える別のドレイン構造(1012)とを含むSCRMOSトランジスタを有する。中央配置のドレイン拡散領域とソース拡散領域との間のMOSゲート(1022)がソース拡散領域へ短絡される。SCRMOSトランジスタを有する集積回路を形成するためのプロセスも開示される。  (もっと読む)

(もっと読む)

静電気保護素子及びその製造方法

【課題】リーク電流の少ない静電気保護素子を提供する。

【解決手段】半導体基板100nと、半導体基板内に形成され、第1の導電型の不純物が拡散された第1のウェル101と、第1のウェル内に、第1のウェルの一部の領域を挟んで形成され、第2の導電型の不純物が拡散されたコレクタ領域110及びエミッタ領域112と、第1のウェル内に、前記エミッタ領域と分離する第1の分離領域102を挟んで形成され、第1のウェル内に拡散された不純物の濃度よりも高い濃度の、第1の導電型の不純物が拡散されたベース拡散領域114と、前記エミッタ領域下方から前記エミッタ領域と前記ベース拡散領域との間までの第1のウェル内の領域に形成され、第2の導電型の不純物が拡散された拡散領域103aとを備えた静電気保護素子。

(もっと読む)

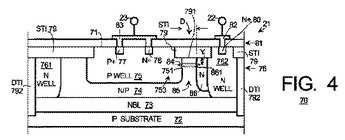

ESD保護デバイスおよび方法

関連するデバイスまたは回路24を保護する静電気放電(ESD)保護クランプ21、21’、70、700は、バイポーラ21、21’、70、700を備える。アバランシェ降伏が、上にある誘電体・半導体界面791から離れ、デバイス70、700のベース領域74、75の部分84,84以内に望ましく起こるように向かうベース75およびコレクタ86領域のドーパントを構成される。例えば、半導体ダイまたはウェハのトランジスタ21、21’、70、700の異なる方位配向のおかげで、ESDトリガ電圧の最大変化(△Vt1)MAXはベース・コレクタ間隔寸法Dの関数である。トリガ電圧一貫性および製造歩留まりが改良される。  (もっと読む)

(もっと読む)

ESD保護素子、半導体装置およびプラズマディスプレイ装置

【課題】 製造コストを上昇させることなくSOI構造の高耐圧半導体集積回路装置に組み込むことができるとともに、チップ面積の増大を抑制できるESD保護素子を提供する。

【解決手段】

ESD保護素子は、埋め込み絶縁膜2上に形成され、素子分離領域17で囲まれた第1導電型半導体層3、半導体層3に形成された第1導電型第1半導体領域8、第1導電型第1半導体領域8から離間して半導体層3に形成された第2導電型第1半導体領域16、第2導電型第1半導体領域16に形成され、それより高不純物濃度の第2導電型第2半導体領域10、第2導電型第2半導体領域10に形成された高不純物濃度の第1導電型第2半導体領域9からなる構造を有している。また、第1電極12および第2電極13は高耐圧半導体回路に電気的に接続され、第2導電型第1および第2半導体領域16、10は電気的にフローティング状態となっている。

(もっと読む)

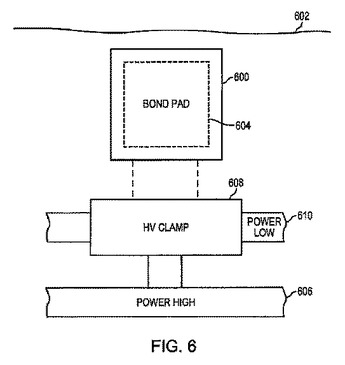

一体化された過渡過電圧保護を有するボンドパッド

過電圧クランプ構造および過電圧クランプ構造を形成する方法が提供される。いくつかの実施形態において、過電圧クランプ構造は、基板(708)と、基板の上に配置されるボンドパッド(700)と、ボンドパッドの下の基板に形成されるプレーナー高電圧MOSデバイス(100c)とを含む。高電圧MOSデバイス(100c)は、基板に形成される井戸(100、115)と、井戸に形成されるドープされた浅い領域(130、135、140、145)と、井戸の上に配置されるゲート(160)とを含み得る。いくつかの実施形態において、クランプ構造は、第1のスナップバック後にソフトな故障の漏れを示さず、デバイスエリアを有意に減少させながら、ESDロバストネスを大幅に延ばす。  (もっと読む)

(もっと読む)

半導体装置

【課題】 占有面積の大きな増加なく、十分なESD保護機能を持たせたシャロートレンチ分離構造を有するESD保護素子を得ることを目的とする。

【解決手段】 素子分離にシャロートレンチ構造を有するESD保護素子を有する半導体装置において、ESD保護素子は、中央に外部接続端子からの信号を受けるN型の領域が配置され、外部接続端子からの信号を受けるN型の領域の側面ならびに底面を囲むようにP型の領域が配置され、P型の領域の側面および底面を囲むように埋め込みN型の領域が配置され、埋め込みN型の領域の周囲にP型の基板端子領域が配置され、P型の基板端子領域の周囲にトレンチ分離領域が配置された半導体装置とした。

(もっと読む)

横型半導体装置

【課題】SOI基板のシリコン半導体層を薄膜化することによって横型の半導体装置の耐圧を高め、しかも大電流の通電時にシリコン半導体層が熱破壊されるまでの時間が短くなることを防止する。

【解決手段】IGBT1では、支持基板11と埋め込み酸化シリコン層12とシリコン半導体層13と絶縁層23とが順に形成されている。シリコン半導体層13は、エミッタ電極20に接しているエミッタ領域14と、コレクタ電極21に接しているコレクタ領域15と、ボディ領域17及びバッファ領域19の一部とドリフト領域16とからなる中央半導体領域とを備えている。絶縁層23の一部は、酸化シリコンよりも熱伝導性が高い材料で形成されているとともにドリフト領域16の真上に広がっている高熱伝導層27である。

(もっと読む)

101 - 120 / 639

[ Back to top ]