Fターム[5F038CA10]の内容

半導体集積回路 (75,215) | レイアウト (7,547) | チップ平面上でのレイアウト (5,921) | 電極パッド配置 (1,058)

Fターム[5F038CA10]に分類される特許

161 - 180 / 1,058

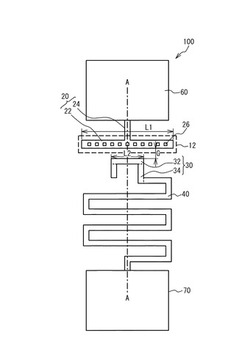

TSVベースの3次元積層ICのためのテストアーキテクチャ

評価素子

【課題】チャージアップした電荷を検出する感度を向上させること。

【解決手段】半導体基板10上に形成された絶縁膜14と、前記絶縁膜内に形成され、延伸方向に延伸した延伸部22を含む第1配線20と、前記絶縁膜内に設けられ、前記半導体基板と前記延伸部とを電気的に接続するコンタクト26と、前記絶縁膜内に形成され、前記延伸部と前記半導体基板の面方向に対向し前記延伸部より長さの短い対向部32と、前記対向部から前記第1配線の反対方向に引き出される引き出し部34と、を含む第2配線30と、前記引き出し部に電気的に接続されたアンテナ電極40と、含む評価素子。

(もっと読む)

半導体装置

【課題】 本発明の目的は、半導体装置単体で負電源を必要とせずにスイッチングが可能な素子を提供することである。

【解決手段】 この発明の半導体装置は、ノーマリオンFETと、一方の電極を前記FETのゲートに、他方の電極を入力端子に電気的に接続されたキャパシタと、アノード電極が前記FETのゲートに、カソード電極が前記FETのソースに電気的に接続されたダイオードと、を前記FETと同一チップ上に形成したことを特徴としており、さらに、前記キャパシタが、前記FETのゲート引き出し電極上に誘電体などの絶縁膜を形成し、形成した前記絶縁膜に金属膜を形成することにより形成されたことが好ましい。

(もっと読む)

半導体装置

【課題】半導体装置の性能と信頼性を向上させる。

【解決手段】半導体チップCP1には、スイッチ用のパワーMOSFETQ1,Q2と、パワーMOSFETQ1の発熱を検知するためのダイオードDD1と、パワーMOSFETQ2の発熱を検知するためのダイオードDD2と、複数のパッド電極PDとが形成されている。パワーMOSFETQ1およびダイオードDD1は、辺SD1側の第1MOSFET領域RG1に配置され、パワーMOSFETQ2およびダイオードDD2は、辺SD2側の第2MOSFET領域RG2に配置されている。ダイオードDD1は辺SD1に沿って配置され、ダイオードDD2は辺SD2に沿って配置され、ダイオードDD1,DD2間にソース用のパッド電極PDS1,PDS2以外の全てのパッド電極PDを辺SD3に沿って配置している。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】パッケージの端子数の増加と、ベースチップのI/O領域の増加を抑制する構造体を提供する。

【解決手段】複数の外部導出配線と、マスクROM領域、内部バス、複数のバス接続端子、および複数の外部接続端子を有する半導体集積回路基板と、この半導体集積回路基板上に積層され、複数のROM接続端子を持つプログラマブルROM15と、を備えた半導体集積回路装置において、複数の外部導出配線の一部、半導体集積回路基板、プログラマブルROM15、複数の外部接続端子と複数の外部導出配線との電気的接続、および複数のバス接続端子と複数のROM接続端子との電気的接続のそれぞれが同一半導体パッケージ内に封止されている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、ヒューズ層を覆う絶縁膜の膜厚を精度良く調整する。

【解決手段】半導体基板10上にザッピング素子1のヒューズ層12を形成し、ヒューズ層12を覆う第1の絶縁膜13を形成する。第1の絶縁膜13上にはヒューズ層12を覆うエッチングストッパー膜14を形成し、エッチングストッパー膜14を覆う第2の絶縁膜16を形成する。他の工程を経た後、第1のエッチング工程として、ヒューズ層12上で、第2の絶縁膜16をエッチングストッパー膜14に対して選択的にエッチングすることにより、エッチングストッパー膜14の表面を露出させる。次に、第2のエッチング工程として、ヒューズ層12上で、エッチングストッパー膜14を第1の絶縁膜13に対して選択的にエッチングすることにより、第1の絶縁膜13の表面を露出させる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の配線における電気的干渉を低減する。

【解決手段】半導体装置1Aにおける接続パッド12と半田端子23を繋ぐ電流経路となる配線を、半導体基板11を覆う下地絶縁膜14上に形成された下層配線17と、下地絶縁膜14を覆うフィルム材19上に形成された上層配線21とを組み合わせて構成するとともに、半導体基板11から比較的離間した位置に配されて、下層配線17よりも半導体基板11と電気的に干渉しにくくなっている上層配線21の割合を高くするように、上層配線21を下層配線17よりも長く形成することとした。

(もっと読む)

マルチチップパッケージ

【課題】 積層されたパッケージ間の信号伝達の速度を向上させることにある。

【解決手段】 マルチチップパッケージに関し、多数のチップが積層されたマルチチップパッケージにおいて、多数のチップの各々は互いに電源または信号を伝達するように構成される多数のインダクターパッドを備え、前記多数のインダクターパッドのうちのいずれか一つである基準インダクターパッドの両側には互いに異なる磁束方向を有する第1及び第2インダクターパッドが形成される。

(もっと読む)

昇圧回路及び半導体装置

【課題】半導体チップのチップ面積を小さくできる昇圧回路を提供する。

【解決手段】昇圧回路100は、N個(Nは2以上の自然数)の容量素子(容量素子C0〜C3)を備える。N個の容量素子のうち第K番目(1<K<N、Kは自然数)の容量素子(容量素子C2)は第(K−1)番目の容量素子(容量素子C1)によって昇圧された第(K−1)番目の昇圧電圧を受けて、第(K−1)番目の昇圧電圧を更に昇圧した第K番目の昇圧電圧を発生して第(K+1)番目の容量素子(容量素子C3)に供給し、第N番目の容量素子の一端(出力端子OUT)から第N番目の昇圧電圧を発生する。N個の容量素子の内、少なくとも1つの容量素子(容量素子C0及びC1)は他の容量素子(容量素子C2及びC3)が形成された第1のチップ(半導体チップCHIP2)とは異なる第2のチップ(半導体チップCHIP1)に形成され、第1及び第2のチップは互いに積層されている。

(もっと読む)

半導体装置

【課題】同一チップ上での異なる信号の相互干渉が原因で生じる信号歪みを抑制した半導体装置を提供する。

【解決手段】半導体装置50は、絶縁基板1上に形成された第1の絶縁膜7と、第1の絶縁膜7上に島状に形成され、トランジスタを有するシリコン層であるシリコン島領域16a、16bと、シリコン島領域16a、16b外に形成され、インダクターL、容量C1、C2及び抵抗Rの少なくとも1つを有する受動回路が形成された受動回路領域と、トランジスタTr1、Tr2及び受動回路を電気的に接続する配線10とを備える。

(もっと読む)

半導体集積回路装置

【課題】電極パッドからESD保護回路に十分なサージ電流が流れず、入出力回路が破壊されやすくなる。

【解決手段】半導体集積回路装置201の回路ブロック21の上層に、電極パッド22が設けられている。電極パッド202,213と、内部回路208およびESD保護回路206との間の接続配線に、分岐点A204,分岐点B212が設けられている。分岐点A204,分岐点B212は、電極パッド202,213よりもESD保護回路206に近い位置に、配置されている。

(もっと読む)

半導体装置

【課題】 同時に入出力されるデータビット数が異なる半導体装置では、プリント基板の半田ボールと半導体チップのパッド位置が、左右の領域に分かれ、ボールとパッド間の配線ができなくなり、ビット数が異なる製品を、1つのチップで共用することができないという問題がある。

【解決手段】 同時に入出力されるデータビット数が8、16、32ビットのいずれかに変更可能で、複数のパッド電極がチップの中央部に少なくとも2列に配列された半導体チップを有した半導体装置は、前記複数のパッド電極の中の所定のパッド電極が、データ入出力数が16ビットのときのみに使用される16ビット専用のパッド電極と、データ入出力数が32ビットのときのみに使用される32ビット専用のパッド電極と、を備えることを特徴とする。

(もっと読む)

半導体素子及び半導体装置の製造方法

【課題】隣接した半導体素子領域(IC領域)を同時に検査しても、検査用のプローブが外部電極から食み出し難くい、半導体素子、半導体ウエハ、及び半導体装置の製造方法を提供する。

【解決手段】外周に沿って配置された複数の外部電極28を有する、矩形の半導体素子38であって、前記外部電極の対向する二辺が、前記半導体素子の一の対角線34に垂直な方向36を向いている半導体素子。

(もっと読む)

半導体メモリ装置及びそれを含む半導体パッケージ

【課題】高性能及び低電力が要求される多様な装置及びシステムを支援できる、マルチチャネルインタフェース方式のワイド入出力を有する半導体メモリ装置及びそれを含む半導体パッケージを提供する。

【解決手段】本発明の一実施形態に係る半導体メモリ装置は、複数のメモリセルアレイを含む半導体ダイからなり、半導体ダイの中央部に形成される入出力バンプパッド部を含む。入出力バンプパッド部は、前記それぞれのメモリセルアレイを外部装置と独立的に接続するための複数のチャネルを提供する。マルチチャネル方式のワイド入出力インタフェースを通じて動作周波数の減少及びバンド幅の拡張を図ることによって、高性能の装置及びシステムを支援すると同時に電力消耗を減少させる。

(もっと読む)

半導体装置

【課題】一つの半導体装置をボンディングオプションにより機能の異なる製品に切り替える場合に、その半導体装置で使用される内部電源の安定化容量を、それぞれの製品において最適化することができる半導体装置を提供する。

【解決手段】半導体装置10は、異なる電源電位の電圧が供給される2つのインナーリード12A、12Bに選択的にワイヤーボンディングされるボンディングオプション用パッド14と、ボンディングオプション用パッド14に接続されるインバータ16と、短絡されたソース及びドレインがインバータ16に接続され、ゲートが内部電源IVから電源電圧が出力される電源出力ライン18に接続された、内部電源IVの出力レベルを安定化させるためのNMOSトランジスタ20と、を備える。

(もっと読む)

配線構造

【課題】電源・信号間の干渉および結合の抑制と、電源ノイズの抑制と、信号間の干渉・クロストークの抑制と、インピーダンス不連続による信号反射の抑制とを、全てバランスよく満たす低コストな高速デバイスを提供する。

【解決手段】信号用ボンディングワイヤ31d、31eと、グランド用ボンディングワイヤ31b、31gと、電源用ボンディングワイヤ32a、32c、32f]とを、次のように配置する。すなわち、グランド用ボンディングワイヤまたは電源用ボンディングワイヤの一方が、信号用ボンディングワイヤと同じ第1の包絡面に含まれ、他方は別の第2の包絡面に含まれる。ここで、第2の包絡面に含まれるボンディングワイヤおよび信号用ボンディングワイヤの間の電磁結合が、第1の包絡面に含まれる2本のボンディングワイヤの間の電磁結合よりも小さくなるようにする配線構造。

(もっと読む)

半導体集積回路

【課題】チップ面積が増大することなく設計において大きな後戻りをしなくてすむ半導体集積回路を提供すること。

【解決手段】一列に配列された各IOバッファ1〜5と、各IOバッファ1〜5に対応して配列されたパッド接続用配線21〜25と、各IOバッファ1〜5に対応して一列に配列されるとともに、IOバッファ1〜5及びパッド接続用配線21〜25と異なる層にて対応するパッド接続用配線の一部と重なるように配置され、かつ、対応するパッド接続用配線の隣の他のパッド接続用配線まで延長して配線されたIOバッファ切替用配線31〜35と、を備え、各IOバッファ切替用配線31〜35は、隣の他のIOバッファ切替用配線と短絡しないように同じ形状に形成され、各IOバッファ1〜5は、同じ位置にて対応するIOバッファ切替用配線31〜35と電気的に接続される。

(もっと読む)

半導体集積回路

【課題】電源プレーンと内部回路とを接続パッドを介して接続する、接続経路のインピーダンスに応じた適切な放電能力の保護回路を有する半導体集積回路を提供する。

【解決手段】本発明に係る半導体集積回路1aは、半導体チップ10aと、半導体チップ10aに電位を供給するパッケージ2とを有し、半導体チップ10aは、内部回路と、接続パッドと、内部回路と接続パッドの間に接続され、内部回路を保護する保護回路とを有し、パッケージ2は、外部端子と、パッケージ2と半導体チップ10aを接続するための内部端子と、電源プレーンと、電源プレーンと内部端子とを接続する第1の配線と、内部端子と接続パッドとをそれぞれ接続する複数の第2の配線とを有する。保護回路の放電能力の大きさは、電源プレーンと接続パッドとの接続経路である、第1の配線、内部端子および第2の配線のインピーダンスに応じて設定される。

(もっと読む)

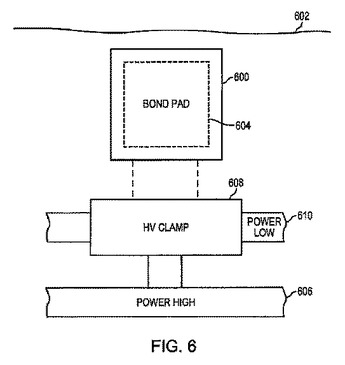

一体化された過渡過電圧保護を有するボンドパッド

過電圧クランプ構造および過電圧クランプ構造を形成する方法が提供される。いくつかの実施形態において、過電圧クランプ構造は、基板(708)と、基板の上に配置されるボンドパッド(700)と、ボンドパッドの下の基板に形成されるプレーナー高電圧MOSデバイス(100c)とを含む。高電圧MOSデバイス(100c)は、基板に形成される井戸(100、115)と、井戸に形成されるドープされた浅い領域(130、135、140、145)と、井戸の上に配置されるゲート(160)とを含み得る。いくつかの実施形態において、クランプ構造は、第1のスナップバック後にソフトな故障の漏れを示さず、デバイスエリアを有意に減少させながら、ESDロバストネスを大幅に延ばす。  (もっと読む)

(もっと読む)

半導体装置

【課題】 パッケージに封止される半導体素子は、使用環境によって湿度の影響を受けて、半導体素子の劣化が起こることがある。パッケージに実装することが容易で、半導体素子周囲の湿度・水分量を測定・記録できる湿度センサを得る。

【解決手段】 半導体基板2上に形成した絶縁膜7の上に、水溶性金属の薄膜8を用いた湿度センサ6を形成し、水溶性金属の薄膜8の抵抗を測定する。水溶性金属とは、電位−pH図において、電位がゼロ、pHが7付近で腐食域にある金属を意味する。

(もっと読む)

161 - 180 / 1,058

[ Back to top ]