Fターム[5F038CA10]の内容

半導体集積回路 (75,215) | レイアウト (7,547) | チップ平面上でのレイアウト (5,921) | 電極パッド配置 (1,058)

Fターム[5F038CA10]に分類される特許

121 - 140 / 1,058

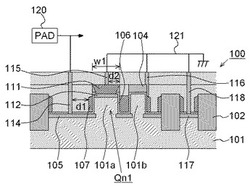

半導体装置

【課題】安定した静電気保護機能を有する半導体装置を提供すること。

【解決手段】半導体装置は、シリコン柱を有するシリコン基板、シリコン柱の側壁に沿って形成されたゲート電極、ゲート電極とシリコン柱との間に形成されたゲート絶縁膜シリコン柱の上部に形成された上部拡散層、及びシリコン基板において上部拡散層より下方に形成された下部拡散層、を有する縦型MOSトランジスタと、下部拡散層と電気的に接続されたパッドと、を備える。サージ電圧が印加された際に下部拡散層と基板との間においてブレイクダウンが発生する。

(もっと読む)

半導体集積回路および半導体集積回路装置

【課題】 電源電圧の安定した供給が可能な半導体集積回路および半導体集積回路装置を提供する。

【解決手段】 半導体集積回路40において、半導体基板の表面の、コア領域に、第1の電源が供給されて動作するコア回路が形成されるとともに、前記半導体基板の表面の前記コア領域の外側のI/O領域に、第2の電源が供給されて動作するI/O回路が形成された半導体集積回路40であって、前記半導体基板内に、該半導体基板を貫通して、前記第1の電源を供給する貫通ビア51が設けられ、前記半導体基板の表面のI/O領域に、前記第2の電源を供給するパッド46が設けられたことを特徴とする。

(もっと読む)

半導体集積回路および半導体集積回路に対するゲートスクリーニング試験の方法

【課題】複数のMOS型半導体素子が集積された半導体集積回路であって、ゲートスクリーニング試験を効率的に実施することのできる半導体集積回路を提供すること。

【解決手段】IC400は、MOS型半導体素子であるMOSFETとその制御回路とを1チップ内に4チャンネル設けたICであり、パワーMOSFET401〜404のゲート電極に電圧レベルシフト回路405〜408が接続され、各電圧レベルシフト回路に制御回路409〜412が接続される。各MOSFETからのゲート電極がすべて逆流防止回路413に接続され、その先にゲートスクリーニング試験端子Gが1つ接続される。制御回路409〜412の入力には入力端子IN1〜IN4、電源にはドレイン端子D1〜D4、グランドにはソース端子S1〜S4が接続される。パワーMOSFET401〜404のソース電極はソース端子S1〜S4に、ドレイン電極はドレイン端子D1〜D4に接続される。

(もっと読む)

半導体装置

【課題】ボンディングパッドの直下の酸化膜を壊すことなくウエハテストを行う。

【解決手段】半導体基板9と、半導体基板9上に形成された5層の配線層と、前記5層の配線層のうち、最上層の第5配線層5に形成され、それぞれ一部が露出した複数のボンディングパッド5eと、半導体基板9上に形成され、かつボンディングパッド5eの下において平面視でボンディングパッド5eと重なる位置に配置され、さらにボンディングパッド5eと電気的に接続されたトランジスタ素子等の能動素子と、を有しており、ボンディングパッド5eの直下には、5層の配線層のうちのいずれの配線層も設けられていない緩衝膜7が形成されている。

(もっと読む)

高周波スイッチ

【課題】出力特性が優れた高周波スイッチを提供する。

【解決手段】本発明の実施形態の高周波スイッチは、入力端子ANT1と複数のスイッチング素子と複数の高周波信号線と複数の出力端子RF1〜RF8とからなる高周波スイッチ回路部を有する高周波スイッチICチップ10を備える。前記入力端子ANT1と前記複数の出力端子の各出力端子RF1〜RF8は、それぞれ等しい長さの高周波信号線H1〜H8で接続される。前記複数の出力端子RF1〜RF8は、前記高周波スイッチICチップの外周の表面上に配置される。前記入力端子ANT1は、前記高周波スイッチ回路部の中心に配置される。

(もっと読む)

多層回路基板、基板装置、および多層回路基板の異常判定方法

【課題】スイッチング素子の駆動により生じる熱について精度よく検出することのできる多層回路基板を提供する。

【解決手段】パワー基板4の基板本体10は、積層された複数の絶縁層11,12,13の間に導電層21,22が配置された構成を有している。基板本体10の上面10aにベアチップ実装された半導体チップ15は、スイッチング素子28と、上温度センサ29と、を含んでいる。CPU7は、上温度センサ29の検出温度T1、およびスイッチング素子28の発熱量Q1を用いて疑似熱抵抗TR1を演算する。CPU7は、疑似熱抵抗TR1が大きいとき、パワー基板4に異常が生じていると判定する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 半導体基板上に形成された半導体集積回路の、特にプローブ検査時間を短縮することができる検査工程を提供する。

【解決手段】 検査対象となる半導体基板には、半導体集積回路本体を含む回路領域2aと、それに隣接するスクライブエリアにTEG3aが形成され、回路領域2aには第1パッド電極5a、5bの列が、またTEG3aには第2パッド電極6の列が設けられる。ここでTEG3aに隣接している方の第1パッド電極5aが第2のパッド電極6に対向しないように配置される。このような状態の第1パッド電極5a、5bおよび第2パッド電極6にプローブ針8a、8b、9を接触させて半導体集積回路の検査とTEGの測定とを同時に行う。

(もっと読む)

半導体装置

【課題】電源配線と接地配線とを有する半導体装置において、配線の一部における電圧ドロップや、電圧ドロップに伴うマイグレーションの発生を抑制することが可能な半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、主表面に沿うように層状に広がる電源シート状配線PPWRと、主表面に沿うように、主表面に交差する方向に関して電源シート状配線と一定の距離を隔てて層状に広がる接地シート状配線PGNDと、上記主表面上に形成され、主表面内の一の方向に延在する電源配線PWRと、主表面上に形成され、一の方向に沿う方向に延在し、電源配線PPWRと一定の距離を隔てて形成された接地配線GNDとを備える。上記電源シート状配線PPWRは、電源配線PWRと電気的に接続されており、接地シート状配線PGNDは、接地配線GNDと電気的に接続されている。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

半導体チップ及びそれを搭載した半導体モジュール

【課題】半導体チップに安定した電源電流を供給したり、電源から信号系へ混入する雑音を低くするための、半導体デバイスの電源流入及び電源流出端子の端子数の低減と、前記半導体チップを搭載した実装面積の低減を可能とする半導体モジュールを提供する。

【解決手段】半導体チップ20の両面に電源系と信号系の電気的接続端子を振り分けて配置する。大電流が流れる流路の許容電流値を大きくする構成により、少ない端子数でも安定な電源供給が可能、信号系への雑音混入を低減、ピン数の低減による実装面積の低減、放熱効果の増大などが可能となる。また、この半導体チップ20を搭載した半導体モジュールにより、大電流が流れる高速動作でも安定した特性を実現できる。

(もっと読む)

ハイパワーGaNベースFET用のレイアウトデザイン

【課題】FETを提供する。

【解決手段】FETは、基板と、基板上に配置されたバッファ層と、バッファ層上に配置されたチャネル層と、チャネル層上に配置された障壁層とを含む。ソース、ゲート及びドレイン電極は障壁層上に配置されて長手方向に延伸する。チャネル及び障壁層の一部分は長手方向に延伸するメサ部を形成し、ソース及びドレイン電極がメサ部の縁を超えて延伸する。ゲート電極はメサ部の縁側壁に沿って延伸する。導電性ソース相互接続部は障壁層上に配置されソース電極に電気的に接続された第一の端部を有する。第一の誘電体層はバッファ層及びソース相互接続部上に配置される。ゲートビアは第一の誘電体層に形成される。導電性ゲートノードがバッファ層に沿って延伸して前記メサ部の側壁に沿って延伸するゲート電極の一部分に電気的に接続する。ゲートパッドはメサ部に隣接する第一の誘電体層上に配置される。

(もっと読む)

半導体集積回路装置の検査方法及び半導体集積回路装置

【課題】複数の集積回路層が厚さ方向に積層されて成る半導体集積回路装置の層間接続不良の有無を、一層積層する毎に短時間で検査することが可能な検査方法及び半導体集積回路装置を提供する。

【解決手段】互いに積層される集積回路層10及び20に、複数の検査用整流素子部15及び25をそれぞれ形成する。複数の検査用整流素子部15(25)は、複数の接続用端子14(24)のそれぞれと正電源配線13a(23a)及び接地配線13b(23b)との間に接続され、整流素子15a,15b(25a,25b)を含み電流により発光する。複数の接続用端子14及び24を互いに電気的に接続したのち、正電源配線13a(又は接地配線13b)と接地配線23b(又は正電源配線23a)との間にバイアス電圧を印加し、検査用整流素子部25の発光に基づいて、接続用端子14及び24の接続状態を検査する。

(もっと読む)

半導体装置

【課題】ダイシング処理に起因する、チップ用パッド同士のショートを抑制することが可能な半導体装置を提供する。

【解決手段】半導体基板と複数の第1のパッドと、複数の第2のパッドとを備える半導体装置であり、第1のパッドは素子形成領域IMC内に、第2のパッドは素子形成領域IMCを取り囲むダイシングライン領域DLR内に形成される。ダイシングライン領域DLRには、第2のパッド同士が電気的短絡を生じさせやすい第1の領域SLRと、第2のパッド同士が電気的短絡を生じさせにくい第2の領域SURとを有している。第1の領域SLRに対向する位置に配置された一部の第1のパッドは、第2の領域SURに対向する位置に配置された残りの第1のパッドよりも、素子形成領域IMCの外縁の1辺BDLから離れて配置されている。

(もっと読む)

半導体チップ及び半導体装置

【課題】ボンディングに用いるパッド全体のレイアウトで必要な面積の増大を抑制できる半導体チップ及び半導体装置を提供する。

【解決手段】半導体チップに、ボンディング用のパッドであるボンディングパッドとテスト用のパッドであるプローブパッドとを含む複数のパッド形成部を備える。パッド形成部はボンディングパッドとプローブパッドの配列方向と直交する方向に2列で配置される。ボンディングパッドとプローブパッドとは、パッド形成部の列方向において、互いの位置が順次入れ替わるように配置される。

(もっと読む)

半導体装置およびその製造方法

【課題】積層される半導体基板同士が、貫通孔の内部に埋め込まれる導電体により、電気的に良好に接続される半導体装置を提供する。

【解決手段】第1半導体基板SCPは、主表面を有する基板SUBと、基板SUB内および基板SUB上に形成された半導体素子TRと、半導体素子TRに電気的に接続された配線MTLと、基板SUBの主表面であり、互いに対向する第1主面と第2主面とを貫通し、配線MTLに達する貫通孔の内部に形成された導電層TSVとを有する。第1半導体基板SCPと第2半導体基板SCPとが積層され、導電層TSVは第2半導体基板SCPの配線MTLと電気的に接続される。導電層TSVの第2主面では、貫通孔の端部の周囲には凹部DUMが形成され、凹部DUMの底壁面は基板SUBの内部に存在する。導電層TSVを構成する導電材料CUが凹部DUMの内部に充填される。

(もっと読む)

半導体集積回路装置

【課題】ESD保護回路を備え外部端子数を効率よく配置できる半導体集積回路装置を提供する。

【解決手段】第1、第2電源電圧を供給する第1、第2電源パッドに対応した第1、第2電源セル、第1信号パッドに対応した入出力セル、第1電源電圧を供給する第1電源線、第2電源電圧を供給する第2電源線を有する。入出力セルは、信号入出力を行う回路、静電保護回路及び第1電源線と第2電源線との間に設けられた第1MOSを有する。第1電源セルは、第1電源パッドの正静電気に応答して第1MOSを一時的にオンにさせる時定数回路、第1電源パッドに向かう電流を流す一方向性素子を有する。第2電源セルは、第2電源パッドの正静電気に応答して第1MOSを一時的にオンにさせる時定数回路、第2電源パッドに向かう電流を流す一方向性素子を有する。第1MOSのゲートとウェルは時定数回路と接続される。

(もっと読む)

半導体装置及びその製造方法

【課題】チップ面積の増加を抑制しつつ、ウェハ状態でのスクリーニング時に電源電圧低下(IRドロップ)を抑えることができる半導体装置を提供する。

【解決手段】本発明の一形態に係る半導体装置50は、半導体チップ100と、半導体チップ100上面の中央部のチップ中央領域120に形成された複数の外部接続用パッド102及び複数の検査用パッド104と、複数の外部接続用パッド102上に形成されたバンプ105とを備える。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】複数の電源を使用する半導体集積回路装置において、接続対象の接続する電源配線を容易に選択ないし変更できる半導体集積回路装置及びその製造方法を提供すること。

【解決手段】半導体集積回路装置は、静電気保護素子及び入出力回路素子のうちの少なくとも1つを含む接続対象と、1以上の電源配線及びパッドから選択される2以上の要素と、同一層に形成された複数の配線と、複数の配線のうちのいずれか1つの配線と、接続対象とを電気的に接続する第1コンタクトと、を備える。複数の配線は、電源配線、パッド、又は電源配線及びパッドのうちのいずれかと電気的に接続された配線である。

(もっと読む)

半導体装置

【課題】VCOに含まれるスパイラルインダクタとMOSバラクタを接続する配線に付加される寄生インダクタ、および/または寄生容量を低減することができる半導体装置を提供する。

【解決手段】LCタンクVCOは、第1および第2のスパイラルインダクタL1,L2と、第1および第2のMOSバラクタC1,C2とを備える。第1および第2のMOSバラクタC1,C2は、半導体基板に垂直な方向から見たときに、第1のスパイラルインダクタL1と第2のスパイラルインダクタL2の間の領域に配置される。

(もっと読む)

121 - 140 / 1,058

[ Back to top ]