Fターム[5F038CA10]の内容

半導体集積回路 (75,215) | レイアウト (7,547) | チップ平面上でのレイアウト (5,921) | 電極パッド配置 (1,058)

Fターム[5F038CA10]に分類される特許

41 - 60 / 1,058

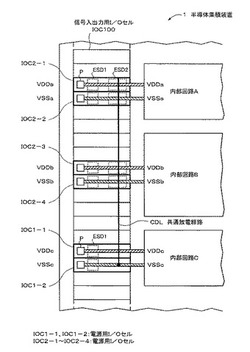

半導体集積装置

【課題】共通放電経路との間の異種電源間ESD保護回路をそれぞれの電源のパッドの近くに配置することのできる半導体集積装置を提供する。

【解決手段】実施形態の半導体集積装置1は、パッドPと、自己電源用ESD保護回路ESD1とを有し、VDDc系統の電源供給に使用の電源用I/OセルIOC1と、パッドPと、自己電源用ESD保護回路ESD1と、異種電源間ESD保護回路ESD2とを有し、VDDa、VDDb系統の電源供給に使用の電源用I/OセルIOC2とを備える。信号入出力用I/OセルIOC100と同一外形寸法の電源用I/OセルIOC1およびIOC2が、列状に配置されたIOC100と同列に配置され、電源用I/OセルIOC2の異種電源間ESD保護回路ESD2へ接続される共通放電経路CDLが、電源用I/OセルIOC1から、列状に配置されたIOC100を貫通して、電源用I/OセルIOC2へ配線される。

(もっと読む)

半導体装置、DC−DCコンバータ及び受像器

【課題】配線抵抗を低減し導通損失による効率低下を改善した半導体装置、DC−DCコンバータ及び受像器を提供する。

【解決手段】第1の導電体と、半導体素子搭載部と、半導体素子と、第1の接続部と、第2の接続部とを備えた半導体装置が提供される。前記第1の導電体は、前記半導体素子搭載部の周囲に設けられている。前記半導体素子は、前記半導体素子搭載部に設けられ、第1のスイッチ素子と、前記第1のスイッチ素子と並列的に設けられた第2のスイッチ素子とを有する。前記第1の接続部と前記第2の接続部とは、前記第1のスイッチ素子と前記第2のスイッチ素子との境界を延長した仮想的な境界線よりも前記第1のスイッチ素子の側に設けられ、前記第1のスイッチ素子と前記第2のスイッチ素子とに電気的に接続され、前記第1の導電体と電気的に接続される。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上させる。

【解決手段】スイッチング用のパワーMOSFETと、そのパワーMOSFETよりも小面積でかつそのパワーMOSFETに流れる電流を検知するためのセンスMOSFETとが1つの半導体チップCPH内に形成され、この半導体チップCPHはチップ搭載部上に導電性の接合材を介して搭載され、樹脂封止されている。半導体チップCPHの主面において、センスMOSFETが形成されたセンスMOS領域RG2は、センスMOSのソース用のパッドPDHS4よりも内側にある。また、半導体チップCPHの主面において、センスMOS領域RG2は、パワーMOSFETが形成された領域に囲まれている。

(もっと読む)

受光デバイス、これを用いた光受信機、及び受光デバイスの製造方法

【課題】 従来のPD製造プロセスと同じ工程で大受光径PDの帯域を拡大して、光受信部の高速化を図る。

【解決手段】 受光デバイスは、半導体基板の上方に形成された第1導電型の第1半導体層、前記第1半導体層上の光吸収層、および前記光吸収層上の第2導電型の第2半導体層の積層構造を有する光検出素子と、前記半導体基板の上方で、前記光検出素子に接続されるインダクタと、前記光検出素子で生成された電流を前記インダクタを介して取り出す出力電極と、前記光検出素子にバイアス電極を印加するバイアス印加用電極と、前記インタダクタの金属配線と交差して、前記光検出素子と、前記出力電極又は前記バイアス印加用電極との間を電気的に接続する交差配線と、を含む。

(もっと読む)

半導体装置、システム装置、及び信号制御方法

【課題】処理装置の入出力パッドの端子数を低減することができる半導体装置を提供する。

【解決手段】処理装置21のバス制御回路34に含まれる入出力回路は、外部I/F22と接続されるパッドに接続される。入力部は、パッドから入力される信号に応じた入力信号を出力する。この入力信号は、処理回路31に供給される。パッドは、入力部の入力端子に接続され、出力端子は電源電圧VDDを伝達する電源配線に接続されている。入力部は、外部I/F22のバス制御回路44から入力されるHレベルの信号の電圧を出力端子から出力する。従って、電源配線には、外部I/F22から入力されるHレベルの信号による電圧が供給される。

(もっと読む)

半導体集積回路及びBGAパッケージ

【課題】実使用時におけるクロストークの発生の抑制と、実使用時以外における信号用端子の確保とを半田ボールを増加させずに実現することが可能な半導体集積回路及びBGAパッケージが提供される。

【解決手段】半導体集積回路10が提供される。バッファ15は、マクロ11に接続される信号入力端子15aと、パッド21に接続される信号出力端子15bとを備える。バッファ15は、マクロ11が出力するバッファ制御信号41に基づいて、信号入力端子15aに入力される信号を信号出力端子15bから出力する動作状態と信号入力端子15aに入力される信号を信号出力端子15bから出力しない非動作状態とが切り替わる。バッファ16は、バッファ制御信号41に基づいて、パッド22とマクロ12とを接続するマクロ接続状態とパッド22とグラウンド電位14とを接続するグラウンド電位接続状態とが切り替わる。

(もっと読む)

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

半導体チップ、半導体ウェハおよび半導体チップの検査方法

【課題】配線抵抗に起因した電圧降下を抑制し、検査工程での誤判定を受けにくい半導体チップおよび半導体ウェハを提供する。更に、配線抵抗に起因した電圧降下を抑制し、検査工程で誤判定を受けにくい半導体チップの検査方法を提供する。

【解決手段】電極パッド領域は、絶縁膜(7)上で一列に配列されたn個(n≧3)の電極パッド(4m−4から4m+4)を備える。内部セル領域は、電極パッド領域側に配列されている半導体回路(3l−3から3l+3)にそれぞれ接続された配線(VDDL)をn個の電極パッドの配列方向に備える。n個の電極パッドの内、第1の電極パッド(4m−1)と、第1の電極パッドから1個の電極パッドを隔てた第2の電極パッド(4m+1)とが、絶縁膜中で互いに接続され、かつ、配線Lm−1およびLm+1によって、配線(VDDL)にそれぞれ接続されている。

(もっと読む)

半導体集積回路装置

【課題】内部コアエリアのトランジスタを犠牲にすることなく、周辺エリアのトランジスタを用いてリップルフィルタによる電源供給回路を構成する。

【解決手段】入出力回路を構成するためのトランジスタが配列されてなる周辺エリア(図2の12に相当)をチップ上に有する半導体集積回路装置であって、ドレインを電源に接続し、ソースを負荷側に接続し、ゲートを容量素子(図2のC1)を介して交流的に接地する第1のトランジスタ(図2のMN1)と、容量素子をゲート・基板間によって形成する第2のトランジスタと、を周辺エリアに備える。

(もっと読む)

半導体素子の構造、半導体抵抗素子の製造方法およびFETスイッチ回路

【課題】薄膜抵抗又は基板抵抗によって数kΩから数十kΩの抵抗値を持つゲート抵抗のサイズが基板長さ、基板幅に比べて大きい。

【解決手段】能動層10を有する半導体基板11と、半導体基板の能動層10にオーミック接触するソース電極13及びドレイン電極14と、能動層10の上方に設けられたゲート電極15と、半導体基板11に設けられた非活性領域16と、非活性領域16上にゲート電極15の一部が引出されて接触する導体17と、非活性領域16上で直流電圧が印加されるパッド電極18と、パッド電極18及び導体17にオーミック接触し、非活性領域16に設けられたゲート抵抗領域19とを備え、ゲート抵抗領域19は半導体基板11へボロンイオンを注入することによって形成され、ボロンイオンの注入量によりゲート抵抗領域19上のシート抵抗値を高めたことを備えたことを特徴とする半導体素子の構造が提供される。

(もっと読む)

半導体装置における電流による配線破壊箇所の予測方法

【課題】半導体装置の電流による配線破壊箇所の予測方法において、解析時間を短縮する。

【解決手段】下層配線14A,14Bをそれぞれ一つの直列抵抗で、第1の下層ビア15A,第2の下層ビア15Bを1個の抵抗で、第1の上層ビア17A、第2の上層ビア18Bを1個の抵抗で、第1及び第2の上層配線16A,16Bを抵抗ブリッジ回路で、パワートランジスタTRを直列抵抗で、それぞれモデリングしてなる解析モデルをモデリング用計算機により生成する。回路シミュレータ3により、解析モデルにおけるパワートランジスタTRに電流を供給し、解析モデルにおける各抵抗に流れる電流に基づいて、第1及び第2の下層配線14A,14B、第1及び第2の上層配線16A,16Bにおける各抵抗の電流密度を計算し、各抵抗の電流密度と、配線破壊を起こす電流密度閾値とを比較器4により比較することにより、配線破壊箇所を予測する。

(もっと読む)

半導体装置

【課題】パッドの下方に半導体素子を設けることができ、信頼性の高い半導体装置を提供する。

【解決手段】素子形成領域10Aと該素子形成領域10Aの周囲に設けられた素子分離領域20とを有する半導体層10と、前記素子形成領域10A内に形成された素子30と、前記半導体層10の上方に設けられた層間絶縁層60と、前記層間絶縁層60の上方に設けられ、平面形状が短辺と長辺とを有する長方形である電極パッド62であって、前記素子30と平面視で少なくとも一部が重複する前記電極パッド62と、を含み、前記半導体層10において、前記電極パッド62の前記短辺の鉛直下方から外側に位置する所定の範囲は、素子禁止領域12である。

(もっと読む)

半導体装置、半導体装置の設計方法、半導体装置設計装置、及びプログラム

【課題】より多くのI/Oセルを配置することができるようにする。

【解決手段】多層配線層には、電位供給用接続配線230が設けられている。電位供給用接続配線230は、平面視で外周セル列20を構成するI/Oセル200のいずれか、および内周セル列30を構成するI/Oセル200のいずれかと重なっている。そして電位供給用接続配線230は、外周セル列20の下方に位置する電源電位供給配線222を、内周セル列30の下方に位置する電源電位供給配線222に接続するとともに、外周セル列20の下方に位置する接地電位供給配線224を、内周セル列30の下方に位置する接地電位供給配線224に接続している。

(もっと読む)

半導体装置およびその製造方法

【課題】放熱性と耐久性に優れた半導体装置およびその製造方法を提供する。

【解決手段】導電ベースプレートと、導電ベースプレート上に接合される半導体チップと、半導体チップと導電ベースプレートとの接合面の中央部に配置された第1接着剤と、半導体チップと導電ベースプレートとの接合面の周辺部に配置された第2接着剤とを備え、第1接着剤は第2接着剤よりも相対的に熱伝導率が高く、第2接着剤は第1接着剤より相対的に接合力が高い半導体装置。

(もっと読む)

半導体装置

【課題】従来の入出力セルよりも回路面積の大きな入出力セルを面積効率良く配置する。

【解決手段】半導体装置において、複数の第1バッファセル31〜34は、基板の一辺に沿って1列に設けられる。複数の第2バッファセル21,22は、複数の第1バッファセルよりも基板の中央寄りの位置に、複数の第1バッファセルの配列方向に沿って1列に設けられる。複数の第1パッド81〜88は、複数の第1バッファセルの上部に上記配列方向に沿って1列に設けられる。複数の第2パッド61〜66は、複数の第1パッドよりも基板の中央寄りの位置に、上記配列方向に沿って1列に設けられる。複数の第2パッド61〜66は、各々が、複数の第1バッファセルのいずれか1つと個別に接続される複数の第3のパッド61,63,65,66と、各々が、複数の第2バッファセルのいずれか1つと個別に接続される複数の第4パッド62,64とを含む。

(もっと読む)

半導体素子の破壊を検知する検知回路

【課題】監視対象の素子の破壊を直接的に検知することを可能にする。

【解決手段】監視対象の半導体素子近傍にモニタ用配線を敷設する一方、所定のクロックを出力するクロック出力手段を当該モニタ用配線の一端に接続し、同モニタ用配線の他端に監視手段を接続する。そして、クロック出力手段からモニタ用配線へ出力されるクロックを伝播を監視手段に監視させ、クロックの伝播が途絶えたことを検出した場合に、監視対象の半導体素子の破壊が生じた旨を通知する破壊通知信号を出力させる。

(もっと読む)

温度測定装置、温度校正装置及び温度校正方法

【課題】熱処理機構を用いて基板を所定の温度に熱処理する熱処理装置において、前記熱処理機構の温度を簡易な方法で適切に校正する。

【解決手段】温度校正装置の温度検査治具10は、熱処理板上に載置される被処理ウェハ70と、被処理ウェハ70上に設けられた複数のホイートストンブリッジ回路71とを有している。ホイートストンブリッジ回路71は、温度変化に応じて抵抗値が変化する4つの測温抵抗体72と、接触子41が接触する4つのコンタクトパッド73と有している。温度校正装置の制御部では、ホイートストンブリッジ回路71が平衡状態となるように、すなわちホイートストンブリッジ回路71のオフセット電圧がゼロになるように、熱処理板の温度を調節する。

(もっと読む)

電力増幅器

【課題】MMICとMMIC外部回路とを接続するボンディングワイヤの影響を比較的簡単な構成で低減し、かつ省スペース化された電力増幅器を提供する。

【解決手段】MMIC基板と、MMIC基板上に配置された高周波プローブパッドと、MMIC基板上に高周波プローブパッドに隣接して配置され、MMIC外部回路とのボンディングワイヤ接続用のメタルプレートとを備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】TEGによる検査結果を容易に確認できるようにしつつ、TEGの占有面積を小さくする。

【解決手段】TEG群300は、第1テスト用パッド310、第2テスト用パッド312、及び複数のTEG(例えば第1TEG320、第2TEG340、及び第3TEG360)を有している。複数のTEGは、電気回路上、第1テスト用パッド310と第2テスト用パッド312の間に位置し、互いに直列又は並列に配置されており、かつ平面視で互いに重なっていない。本実施形態において、TEG群300を構成するTEGは、OBRICH(Optical Beam Induced Resistance Change)用のTEGである。

(もっと読む)

半導体集積回路装置

【課題】配線層間膜の平坦化を行いながら、クラックの伝搬と配線層間膜の剥がれを抑制することを目的とする。

【解決手段】電極パッド113形成領域の、低誘電率膜より誘電率の高い配線層間膜からなる多層配線層領域において、ダミービアを形成しないことにより、配線層間膜の平坦化を行いながら、クラックの伝搬と配線層間膜の剥がれを抑制することができる。

(もっと読む)

41 - 60 / 1,058

[ Back to top ]