Fターム[5F038EZ17]の内容

Fターム[5F038EZ17]に分類される特許

161 - 180 / 527

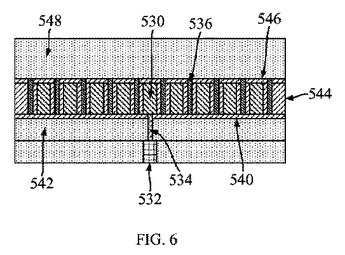

磁気膜強化インダクタ

集積磁気膜強化インダクタ及び集積磁気膜強化インダクタの形成方法が開示される。集積磁気膜強化インダクタが、第一部分及び第二部分を有するインダクタ金属部(530)、インダクタ金属部に結合された上端金属部または底金属部(532)、及びインダクタ金属部の第一部分及び第二部分の少なくとも一方の中か、該一方の上か、該一方に隣接するかのいずれかで配置される分離膜(544)を備える。分離膜が、磁気膜のような磁気材料部(536)を備える。  (もっと読む)

(もっと読む)

抵抗素子の製造方法

【課題】本発明は、プラズマ原子層堆積法(プラズマALD法)の下地の絶縁膜の絶縁性能を低下させず、プラズマALD法での膜形成により高精度の抵抗素子の形成を可能にする。

【解決手段】表面が絶縁性(例えば絶縁層12)を有する基板10に、熱的原子層堆積法によって第1抵抗層21を形成する第1工程と、プラズマ原子層堆積法によって前記第1抵抗層21上に前記第1抵抗層21と同種の第2抵抗層22を形成する第2工程を有する。

(もっと読む)

スイッチング素子、スイッチング素子の製造方法、電子デバイス、論理集積回路及びメモリ素子

【課題】半導体プロセス親和性に優れる酸化物イオン伝導体を適用し、且つ低電圧で駆動できるスイッチング素子、スイッチング素子の製造方法、電子デバイス、論理集積回路及びメモリ素子を提供する。

【解決手段】スイッチング素子は、第1電極11と、第2電極12と、第3電極13と、酸化物を含有するイオン伝導層と、を有し、第1電極11は、イオン伝導層に電子を供給し、第1及び第3電極の少なくとも1以上の電極は、イオン伝導層に金属イオンを供給し、金属イオンは、電子を受け取ってイオン伝導層中で金属を形成し、金属は、第1及び第2電極間を接続し、第3電極13は、第1及び第2電極間を接続する金属の形成及び消去を制御し、イオン伝導層は、第1電極11と第2電極12と第3電極13とに接して設けられ、酸化物の結晶化温度で結晶化した酸化物の結晶よりも小さい結晶である微結晶を含有し、微結晶は、結晶粒界を形成することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を製造できるようにする。

【解決手段】半導体膜11に不純物を注入する工程と、半導体膜11上にレジストパターン16を形成し、不純物を注入した半導体膜11をエッチングによりパターニングして抵抗素子23を形成する工程と、レジストパターン16をアッシングにより除去すると共に抵抗素子23の側面に保護膜24を形成する工程と、抵抗素子23をレジスト膜30で覆う工程と、抵抗素子23内から不純物が外方に拡散することを抑制し、抵抗素子23の不純物濃度を所定値以上に保持する膜厚に保護膜24の厚さを維持しながらレジスト膜30を除去するウェットプロセスを行う工程を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】線形性に優れた半導体抵抗素子を提供する。

【解決手段】本発明の半導体装置は、GaAs基板101上に形成され、3−5族化合物半導体から構成されるHBT130と、GaAs基板101上に形成され、HBT130を構成する半導体エピタキシャル層の少なくとも1層から構成される半導体抵抗素子120とを備え、半導体抵抗素子120は、ヘリウム不純物を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、寄生Trのオン電流が半導体層表面を流れることで、素子が熱破壊するという問題があった。

【解決手段】本発明の半導体装置では、ドレイン領域としてのN型の拡散層9にP型の拡散層14及びドレイン導出領域としてのN型の拡散層10が形成される。そして、P型の拡散層14は、MOSトランジスタ1のソース−ドレイン領域間に配置される。この構造により、ドレイン電極28に正のESDサージが印加され、寄生Tr1のオン電流I1が流れた場合にも、寄生Tr1のオン電流I1の電流経路がエピタキシャル層深部側となることで、MOSトランジスタ1の熱破壊が防止される。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の高集積化と供に、メモリ装置のキパシタで容量値の確保のために、酸素欠損のない高誘電率膜を形成する装置の製造方法を提供する。

【解決手段】誘電体膜を形成する工程と、酸化性ガスを供給して誘電体膜に対して酸化処理を行う工程を複数回、断続的に繰り返す熱処理工程と、を有する誘電体膜を備えた半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率でありかつリーク電流を低減することが可能なゲート絶縁膜を備えた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板11上に設けられ、かつランタンアルミシリコン酸化物若しくは酸窒化物を含む第1の誘電体膜23と、第1の誘電体膜23上に設けられ、かつハフニウム(Hf)、ジルコニウム(Zr)、チタン(Ti)、及び希土類金属のうち少なくとも1つを含む酸化物若しくは酸窒化物を含む第2の誘電体膜24と、第2の誘電体膜24上に設けられた電極14とを含む。

(もっと読む)

半導体装置

【課題】高耐圧のノイズやサージから内部回路を守るESD保護素子であり、要求される条件により合わせ込みやすい構造のESD保護素子を提供する。

【解決手段】高耐圧を有する半導体装置をノイズやサージから守るLOCOSオフセット型Nチャネル型MOSを利用したESD保護素子100において、ドレイン側のLOCOS酸化膜-コンタクト間距離14の内側に抵抗領域15を設け、この抵抗領域15の距離を変えることにより、ESD保護素子の動作時における寄生バイポーラトランジスタのオン状態を保持する保持電圧を容易に調整することが可能となる。

(もっと読む)

基準電圧発生回路装置

【課題】デプレッション型MOSトランジスタとエンハンス型MOSトランジスタによって形成される基準電圧発生回路装置の面積を大きくすることなく基準電圧の温度特性を向上させる。

【解決手段】デプレッション型MOSトランジスタの濃度プロファイルを、第一導電型チャネル領域の基板表面側の不純物濃度が薄く、かつ前記第一導電型チャネル領域と第二導電型の基板領域もしくはウェル領域にて形成されるPN接合付近の前記第一導電型チャネル領域の不純物濃度が濃くなるように制御することで基準電圧の温度特性を向上させる。

(もっと読む)

論理回路及び半導体装置

【課題】電気特性の制御された酸化物半導体層を用いて作製された抵抗素子及び薄膜トランジスタを利用した論理回路、並びに該論理回路を利用した半導体装置を提供する。

【解決手段】抵抗素子354に適用される酸化物半導体層905上にシラン(SiH4)及びアンモニア(NH3)などの水素化合物を含むガスを用いたプラズマCVD法によって形成された窒化シリコン層910が直接接するように設けられ、且つ薄膜トランジスタ355に適用される酸化物半導体層906には、バリア層として機能する酸化シリコン層909を介して、窒化シリコン層910が設けられる。そのため、酸化物半導体層905には、酸化物半導体層906よりも高濃度に水素が導入される。結果として、抵抗素子354に適用される酸化物半導体層905の抵抗値が、薄膜トランジスタ355に適用される酸化物半導体層906の抵抗値よりも低くなる。

(もっと読む)

キャパシタ用絶縁膜、キャパシタ及び半導体装置

【課題】高い誘電率を示すキャパシタ用絶縁膜は、キャパシタに用いられた際にリーク電流が増大する。

【解決手段】2つの電極の間に挟まれて用いられるキャパシタ用絶縁膜を、チタン酸ストロンチウム又はチタン酸バリウムストロンチウムのチタンサイトの一部がハフニウム元素で置換された結晶から形成する。

(もっと読む)

キャパシタレスメモリセルを論理素子と集積化するための方法および構造

基板(基材)上で論理デバイスを製造すること、論理デバイスの表面上に中間半導体基板を形成すること、およびその中間半導体基板上にキャパシタレスメモリセルを製造することを含む集積回路を製造するための方法である。論理デバイスの表面上に形成されるキャパシタレスメモリセルを備える集積回路もまた開示される。それらは、そのような集積回路を含むマルチコアマイクロプロセッサとして使用される。  (もっと読む)

(もっと読む)

半導体装置

【課題】PINダイオードとMIMキャパシタとを備え、その製造工程の短縮を可能とする構造を有する半導体装置を提供する。

【解決手段】GaAs基板10A上に、オーミック電極42a、44aを備えたPINダイオードと、下側電極45と上側電極48cとの間に誘電体層46が介在するMIMキャパシタとが設けられた半導体装置であって、PINダイオードは、GaAs基板10A上に設けられたn型半導体層32およびp型半導体層38と、n型半導体層32上に設けられた第1のオーミック電極42aと、p型半導体層38上に設けられた第2のオーミック電極44aとを具備し、下側電極45は第1のオーミック電極42aと同じ構造を有し、かつ、GaAs基板10Aと下側電極45との間には絶縁膜40が設けられている。

(もっと読む)

垂直置換ゲートトランジスタと集積可能な容量の構造及び作製法

【課題】垂直MOSFETデバイス及び容量に関連したプロセス及び構成を提供する。

【解決手段】半導体デバイスは半導体材料の第1の層と、第1の層中に形成された第1のソース/ドレイン領域を有する電界効果トランジスタを含む。チャネル領域は、第1の層上に形成され、第2のソース/ドレイン領域235はチャネル領域上に形成される。集積回路構造は底部プレート266、誘電体層258及び最上部容量プレート259を有する容量を更に含む。作製方法において、電界効果トランジスタのソース領域及びドレイン領域から成るグループから選択された第1のデバイス領域が、半導体層上に形成される。第1の電界効果トランジスタゲート領域265が、第1のデバイス領域上に形成される。間にはさまれた誘電体層を有する最上部及び底部層も、半導体層上に形成される。別の実施例において、容量層は半導体層中に形成された溝又は窓内に形成される。

(もっと読む)

金属膜およびその製造方法、誘電体キャパシタおよびその製造方法ならびに半導体装置

【課題】 誘電体キャパシタを構成する電極として好適に用いることができる新規な金属薄膜およびその製造方法を提供する。

【解決手段】 本発明の金属薄膜は、

所与の基体の上方に設けられた面心立方型結晶構造を有する金属の薄膜であって、

前記薄膜は、(111)面が優先配向し、かつ、その表面には、前記基体の表面と平行ではない(100)面が表出している。また。本発明の金属薄膜において、前記面心立方型結晶構造を有する金属は、Pt、IrおよびRuの群から選ばれる少なくとも1つを含むことができる。

(もっと読む)

半導体装置およびその製造方法

【課題】

厚い配線を形成すると、絶縁膜との間に剥離が生じやすい。

【解決手段】

半導体装置は、複数の半導体素子を形成した半導体基板と、半導体基板上方において、半導体基板表面とほぼ平行な第1レベルに延在する第1の配線パターンであって、異なるレベルの配線またはパッドとの接続領域を含む平面形状を有し、第1の厚さを有する主配線領域と主配線領域の側壁から1つ以上の段差を形成して外側に張り出し、第1の厚さより薄い第2の厚さを有し、主配線領域から連続する張り出し配線領域とを有する第1の配線パターンと、第1の配線パターンを囲む第1の絶縁領域と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】高い信頼性を有し、微細化に好適な構造の保護ダイオードを備えた半導体装置およびその製造方法を提供する。

【解決手段】半導体基板32の第1領域11に形成された絶縁ゲート電界効果トランジスタ12と、第1領域11に隣接する第2領域13に形成され、絶縁ゲート電界効果トランジスタ12のゲート絶縁膜34より厚く、且つ高濃度に不純物を含有するシリコン酸化膜40と、シリコン酸化膜40上に形成されたポリシリコン層内に複数のPN接合を有するとともに、絶縁ゲート電界効果トランジスタ12のゲートとソースとの間に接続され、絶縁ゲート電界効果トランジスタ12のゲート破壊を防止する保護ダイオード14と、を具備する。

(もっと読む)

半導体装置、半導体装置の製造方法およびスイッチ回路

【課題】トランジスタのリーク電流の低減。

【解決手段】半導体材料の表面に沿って互いに隣接する、シリサイド化される金属を含有する複数の電気素子要素と、複数の電気素子要素を覆い、電気素子要素に含まれる金属が実質的にシリサイド化しない温度で薄膜形成したシリコンを含む保護絶縁膜と、を備える半導体装置が提供される。上記半導体装置において、保護絶縁膜は、シリコンおよび窒素を含有できる。保護絶縁膜は、260℃以下の温度で薄膜形成した窒化シリコン膜であってよく、好ましくは100℃以下の温度で薄膜形成した窒化シリコン膜である。

(もっと読む)

半導体装置、半導体装置の製造方法およびスイッチ回路

【課題】トランジスタのリーク電流の低減。

【解決手段】半導体材料の表面に沿って互いに隣接する複数の電気素子要素と、複数の電気素子要素を覆う、シリコンを含まない下層保護絶縁膜と、下層保護絶縁膜の上に配置され、シリコンを含む上層保護絶縁膜と、を備える半導体装置が提供される。上記半導体装置において、複数の電気素子要素の少なくとも一つは、シリサイド化される金属を含有でき、下層保護絶縁膜は、電気素子要素に含有される金属と上層保護絶縁膜に含有されるシリコンとの接触を阻害できる。下層保護絶縁膜は、比誘電率が10以上の高誘電体層を有してよい。上層保護絶縁膜は、シリコンおよび窒素を含有することができる。

(もっと読む)

161 - 180 / 527

[ Back to top ]