Fターム[5F038EZ17]の内容

Fターム[5F038EZ17]に分類される特許

121 - 140 / 527

発光装置及び発光装置の作製方法

【課題】発光装置の信頼性を向上することを課題の一とする。

【解決手段】同一基板上に駆動回路用トランジスタを含む駆動回路部と、画素用トランジスタを含む画素部とを有する発光装置であり、駆動回路用トランジスタ及び画素用トランジスタは、酸化物絶縁層と一部接する酸化物半導体層を含む逆スタガ型のトランジスタである。画素部において酸化物絶縁層上にカラーフィルタ層と発光素子が設けられ、駆動回路用トランジスタにおいて、酸化物絶縁層上にゲート電極層及び酸化物半導体層と重なる導電層が設けられる。なお、ゲート電極層、ソース電極層及びドレイン電極層は金属導電膜を用いる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】バンドギャップが狭い高誘電率膜を用いたキャパシタにおいて、リーク電流を低減するとともに、製造コストを削減することができる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】ウエハ2上に形成された下部電極としてのTiN膜100と、TiN膜100上に形成された第1の高誘電率絶縁膜としてのHfO2膜110と、HfO2膜110上に形成され、HfO2膜110のバンドギャップよりも狭いバンドギャップを有する第2の高誘電率絶縁膜としてのTiO2膜120と、TiO2膜120上に形成され、非貴金属であって4.8eVよりも高い仕事関数を有する上部電極膜としてのCo膜130と、により構成されている。

(もっと読む)

半導体装置の製造方法及び基板処理システム

【課題】TiO2膜とHfO2膜との相互拡散を抑制でき、リーク電流の増加を抑制させる。

【解決手段】基板上に第1の高誘電率絶縁膜を形成する工程と、第1の高誘電率絶縁膜上に絶縁膜を形成する工程と、絶縁膜上に第2の高誘電率絶縁膜を形成する工程と、第1の高誘電率絶縁膜、絶縁膜および第2の高誘電率絶縁膜が形成された基板に対して熱処理を行う工程と、を有し、第1の高誘電率絶縁膜、絶縁膜および第2の高誘電率絶縁膜は、それぞれが異なる物質で構成されると共に、絶縁膜は、酸化アルミニウム膜、窒化アルミニウム膜、または、窒化シリコン膜で構成される。

(もっと読む)

電気磁気素子およびその製造方法

【課題】電気磁気素子を、平面コイル部を構成する導体ライン内部の渦電流損失を防止または抑制可能な構造とする。

【解決手段】少なくとも下面が平坦な一の導体ライン12が側面同士で近接するように湾曲または屈曲する平面形状をもつ平面コイル部17を備える。平面コイル部17の導体ライン12に磁性体層13が設けられている。より詳細に、磁性体層13は、導体ライン12の長手方向周囲の外周面のうち、少なくとも、導体ライン12の側面の一部であって互いに近接する2つの側面部それぞれに接して形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗素子と、金属を含むゲート電極を有するMISFETとを備えた半導体装置において、ゲート電極の加工不良及びMISFETの特性の劣化を招くことなく、十分な抵抗値が得られる抵抗素子を実現する。

【解決手段】半導体装置は、抵抗素子RとMISFETとを備えた半導体装置である。抵抗素子Rは、半導体基板10上に形成された金属を含む第1の導電膜12aと、第1の導電膜12a上に形成されたシリコンを含む第2の導電膜17aと、第1の導電膜12aと第2の導電膜17aとの間に形成された絶縁膜13aとを有している。

(もっと読む)

炭化珪素絶縁ゲート電界効果トランジスタを用いたインバータ回路および論理ゲート回路

【課題】動作速度を高速化できる SiC MISFETで構成された論理ゲート回路デバイスを得る。

【解決手段】nチャネルエンハンスメント型SiC MISFET(22)と、nチャネルデプリーション型SiC MISFET(22、22b)とでインバータ、NAND/NOR論理ゲート回路を構成する。

(もっと読む)

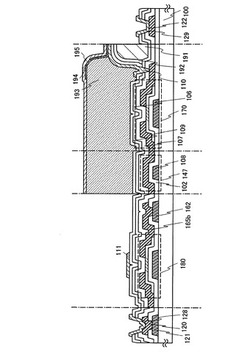

円筒型キャパシタを備えたウェーハレベルパッケージ及びその製造方法

【課題】円筒型キャパシタ構造を採用することにより、静電容量を増大させることが可能な構造を有する円筒型キャパシタを備えたウェーハレベルパッケージ及びその製造方法を提供する。

【解決手段】上面にボンディングパッド104を備え、ボンディングパッド104を露出させる絶縁層106が形成されたウェーハチップ102と、ボンディングパッド104に連結された状態で絶縁層106の一側に延長される再配線層108と、再配線層108に連結され、内部に中空部を有する円筒状の外部電極114bと、中空部内に外部電極114bと分離されるように形成された円筒状の内部電極114aと、外部電極114bと内部電極114aとの間に形成される誘電体層116と、再配線層108、内部電極114a、外部電極114b及び誘電体層116をカバーするように絶縁層106に形成され、内部電極114aの上面を露出させる第1オープン部120aを有する樹脂封止部118とを含んでなる。

(もっと読む)

半導体装置及びその製造方法

【課題】 被保護素子であるMOSFETと、静電保護用のMOSFETを同一基板上に搭載する半導体装置において、高い保護能力を備えながらも少ない工程数で製造することができる半導体装置を提供する。

【解決手段】 低濃度領域6,15,16、ゲート電極11,12,13を形成した後、全面に絶縁膜を成膜する。そして、レジストパターンをマスクにエッチングを行って、領域A1及びA3内においては、ゲート電極の一部上方から低濃度領域の一部上方にかけてオーバーラップするように残存させ(21a,21c)、領域A2内においてはゲート電極の側壁に残存させる(21b)。その後、ゲート電極11〜13及び絶縁膜21a〜21cをマスクとして高濃度イオン注入を行った後、シリサイド化の工程を行う。

(もっと読む)

半導体装置

【課題】 求められる特性が異なる複数のキャパシタを同一基板上に混載するには、さらなる工夫が必要とされる。

【解決手段】 下部電極、上部電極、及び両者の間に配置された誘電体膜を含む下層キャパシタが、半導体基板の上に配置されている。第1の層間絶縁膜が、第1のキャパシタを覆う。複数の上層キャパシタが、第1の層間絶縁膜の上に配置されている。上層キャパシタは、下部電極、上部電極、及び両者の間に配置された誘電体膜を含み、平面視において、下層キャパシタに重なる。半導体基板の上に、上層キャパシタに対応して複数のトランジスタ配置されている。トランジスタは、上層キャパシタとともにメモリセルを構成する。

(もっと読む)

半導体装置

【課題】半導体チップのチップサイズを縮小化することができる技術を提供する。特に、LCDドライバを構成する長方形形状の半導体チップにおいて、短辺方向のレイアウト配置を工夫することにより、半導体チップのチップサイズを縮小化することができる技術を提供する。

【解決手段】LCDドライバを構成する半導体チップCHP2は、複数の入力用バンプ電極IBMPのうち一部の入力用バンプ電極IBMPの下層には入力保護回路3a〜3cが配置されている一方、複数の入力用バンプ電極IBMPのうち他の一部の入力用バンプ電極IBMPの下層には入力保護回路3a〜3cが配置されずにSRAM2a〜2c(内部回路)が配置されている。

(もっと読む)

誘電体膜、誘電体膜を用いた半導体装置の製造方法及び半導体製造装置

【課題】高誘電率を有する誘電体膜の製造方法を提供する。

【解決手段】薄いシリコン酸化膜を形成したSi基板上に、HfN/Hf積層膜を形成し、アニール処理によりHf、Si、O、Nの混合物からなる金属酸窒化物とする誘電体膜の製造する。(1)EOTの低減が可能であり、(2)リーク電流がJg=1.0E−1A/cm2以下に低減され、(3)固定電荷の発生によるヒステリシスが抑制され、(4)700℃以上の熱処理を行ってもEOTの増加が無く耐熱性に優れる。

(もっと読む)

半導体装置

【課題】半導体装置に用いられる保護回路を効果的に機能させ、サージによる半導体装置の破壊を防ぐ。

【解決手段】端子電極と、保護回路と、集積回路と、それぞれを電気的に接続する配線を有し、保護回路は端子電極と集積回路の間に設けられ、端子電極と、保護回路と、集積回路を、配線を分岐することなく接続する半導体装置である。静電気放電による半導体装置の破壊を低減することができる。また、半導体装置の不良発生を低減することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗値のバラツキが小さく良好な特性を示す抵抗素子を有し、高速に動作可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板11内に形成された素子分離領域12と、第1の活性領域13Aと、第2の活性領域13Bと、第1の活性領域13A上に形成され、第1導電型不純物が導入されたシリコンからなる第1導電型ゲート電極16Aを有する第1導電型MISトランジスタと、第2の活性領域13B上に形成され、第2導電型不純物が導入されたシリコンからなる第2導電型ゲート電極16Bを有する第2導電型MISトランジスタと、素子分離領域12上に形成され、p型不純物が導入されたシリコンからなり、n型ゲート電極16A及びp型ゲート電極16Bよりも抵抗値の大きいp型抵抗体16Dとを備えている。

(もっと読む)

半導体装置の製造方法

【課題】金属薄膜抵抗体を備えた半導体装置において、金属薄膜抵抗体の抵抗値及び配線パターンとの接触抵抗の安定化を実現する。

【解決手段】下地絶縁膜5上に、金属薄膜抵抗体23の両端部の形成予定領域に対応して配線パターン11を形成する。配線パターン11上を含む下地絶縁膜5上に平坦化された絶縁膜19を形成する。平坦化された絶縁膜19に、金属薄膜抵抗体23の両端部の形成予定領域及び配線パターン11に対応して接続孔21を形成する。接続孔21内を含み絶縁膜19に対してArスパッタエッチング技術によりエッチング処理を施して、接続孔21の内壁にサイドウォール22を形成するとともに、接続孔21の上端部21aをテーパー形状にする。接続孔21内及び絶縁膜19上に金属薄膜抵抗体23を形成するための金属薄膜を形成する。接続孔21にも金属薄膜を残存させるように金属薄膜をパターニングして金属薄膜抵抗体23を形成する。

(もっと読む)

半導体装置

【課題】ESD耐量が大きく、かつ無効面積の少ないESD保護ダイオードを備えた半導体装置を提供する。

【解決手段】半導体基板の上に絶縁膜を介して設けられ、過電圧によりブレークダウンする保護ダイオードが形成された半導体領域と、前記半導体領域に接続され前記保護ダイオードに電流を流す第1及び第2の電極と、を備え、前記保護ダイオードのPN接合は、前記半導体領域の端面に露出し、前記第1及び第2の電極は、前記PN接合が露出した前記端面から離間して設けられたことを特徴とする半導体装置が提供される。

(もっと読む)

半導体装置

【課題】半導体素子の温度を迅速に、且つ感度よく検出できる温度検出用ダイオードを備えた半導体装置を提供することである。

【解決手段】本発明にかかる半導体装置は、半導体層1aに形成された半導体素子と、半導体層1aが有する凹部11に絶縁膜5aを介して形成された温度検出用のダイオード7と、を備える。半導体素子は、半導体素子の表面に設けられ、且つ半導体素子の出力を取り出す出力パッドSPを有し、ダイオード7は、半導体素子の平面視において、出力パッドSPの周囲に配置されている。

(もっと読む)

半導体素子及びその製造装置

【課題】汎用性が高く、低コストで省資源である方法を採用し、実用性に富み、任意の場所、任意の形状に金属又は半導体を二次元的又は三次元的に形成できる半導体素子及びその製造装置を提供する。

【解決手段】炭素材料と金属酸化物材料又は半導体酸化物材料とを有する還元反応構造1Aを持つ層構造30Aを準備し、還元反応構造1Aに対して局所的にエネルギーを集中することが可能で、かつ還元反応構造1Aに対して2次元的又は3次元的に走査することが可能な熱源を用い、この熱源によって酸化還元反応が起こる温度以上に還元反応構造1Aの一部を走査しつつ選択的に加熱して、炭素材料により金属酸化物材料又は半導体酸化物材料をそれぞれ金属又は半導体に還元し、所望の形状の金属領域又は半導体領域(金属層又は半導体層3A)を形成することによって製造されることを特徴とする半導体素子40Aとすることにより上記課題を解決する。

(もっと読む)

半導体装置およびその製造方法

【課題】チップサイズの縮小化と抵抗値のばらつきの低減化とが両立された抵抗体を有する半導体装置及びその製造方法を提供する。

【解決手段】アナログ回路を構成する半導体装置21であって、シリコン基板1と、シリコン基板1上に形成されたシリコンを主成分とする線状の抵抗体3と、抵抗体3の両端部のうちいずれかの端部に接して形成された金属シリサイドからなる複数のコンタクト形成領域7と、抵抗体3及び複数のコンタクト形成領域7の上に形成された層間絶縁膜4と、層間絶縁膜4を貫通し、複数のコンタクト形成領域7のそれぞれと層間絶縁膜4上に形成された金属配線6とを電気接続する複数のコンタクトプラグ5とを有し、複数のコンタクト形成領域7のそれぞれの面内パターンは、抵抗体3から、少なくとも2箇所で面内屈曲していることにより、コンタクト形成領域7の一部が抵抗体3に並行して形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】 抵抗素子の抵抗値の選択範囲を拡大し、且つ抵抗層形成後にシリサイドブロックを形成せずに該抵抗層のシリサイド化を防止することを可能にする。

【解決手段】 半導体領域11上に絶縁膜15を形成し、絶縁膜15を介して半導体領域11に不純物のイオン注入12を行う。これにより、絶縁膜15の下に抵抗層13が形成されるとともに、抵抗層13に隣接して電極領域14が形成される。その後、電極領域14の表面にシリサイド膜17を形成する。このとき、絶縁膜15は、抵抗層13がシリサイド化されることを防止するシリサイドブロックとして機能する。イオン注入12として、同一半導体基板上に形成されるMOSトランジスタのソース/ドレイン領域への不純物注入工程を利用し得る。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁破壊に至らない微量の電荷の蓄積を抑制した半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11の上に形成された半導体素子1及び保護ダイオード2を備えている。半導体基板11の上には、半導体素子1及び保護ダイオード2を覆うように第1の層間絶縁膜22が形成されている。第1の層間絶縁膜22には、半導体素子1と電気的に接続された第1のプラグ25と、保護ダイオード2と電気的に接続された第2のプラグ23、24とが形成されている。第2のプラグ23、24の上面の面積は、第1のプラグ25の上面の面積よりも大きい。

(もっと読む)

121 - 140 / 527

[ Back to top ]