Fターム[5F038EZ17]の内容

Fターム[5F038EZ17]に分類される特許

41 - 60 / 527

プログラマブルLSI

【課題】低消費電力で、動的コンフィギュレーションにも対応可能なプログラマブルLSIを提供する。

【解決手段】複数のロジックエレメントを有し、複数のロジックエレメントそれぞれは、コンフィギュレーションメモリを有する。複数のロジックエレメントそれぞれは、コンフィギュレーションメモリに記憶されたコンフィギュレーションデータに応じて、異なる演算処理を行い、且つ、ロジックエレメント間の電気的接続を変更する。コンフィギュレーションメモリは、揮発性の記憶回路と、不揮発性の記憶回路との組を有し、不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、当該トランジスタがオフ状態となることによってフローティングとなるノードに一対の電極のうちの一方が電気的に接続された容量素子と、を有する。

(もっと読む)

半導体装置の製造方法、製造システムおよび調整装置

【課題】製品の歩留まりを向上させることができる半導体装置の製造方法、製造システムおよび調整装置を提供すること。

【解決手段】実施形態にかかる半導体装置の製造方法は、成膜工程と、加工工程と、イオン注入工程と、アニール工程と、調整工程とを含む。成膜工程では、基板上に半導体の薄膜を成膜する。加工工程では、薄膜を所定の形状に加工する。イオン注入工程では、所定の形状に加工された薄膜に対してイオン注入処理を行う。アニール工程では、イオン注入処理が行われた薄膜をアニール処理して抵抗素子を生成する。調整工程では、成膜工程における薄膜の成膜条件および成膜結果と加工工程における薄膜の加工結果とのうち、少なくともいずれか1つに基づき、イオン注入工程におけるイオン注入処理の処理条件およびアニール工程におけるアニール処理の処理条件の双方または一方を調整する。

(もっと読む)

半導体装置の製造方法、半導体装置、設計方法、設計装置、及び、プログラム

【課題】集積度及び歩留まりの低下を抑制しつつ、アニール処理に起因した素子の特性ばらつきを軽減する。

【解決手段】半導体基板1上に素子2、3、5を形成する素子形成工程と、素子形成工程の後、半導体基板1上に、選択的に、半導体基板1よりも高い光吸収率を有するか、又は、半導体基板1への光の吸収率を向上させる機能を有する加熱安定化膜7を形成する加熱安定化膜形成工程と、加熱安定化膜7を有する面側から半導体基板1に光を照射し、半導体基板1に注入された不純物を活性化するアニール工程と、を有する半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】温度係数の小さいポリシリコン抵抗体を含む半導体装置の製造方法を提供する。

【解決手段】シリコン基板1にノンドープポリシリコン膜4を形成する工程と、ノンドープポリシリコン膜4をパターニングしてノンドープポリシリコンパターン40を形成する工程と、ノンドープポリシリコンパターン40を窒素雰囲気中でアニールし、ノンドープポリシリコンパターン40のシリコン結晶粒径を拡大する第1アニール工程と、第1アニール工程においてシリコン結晶粒径が拡大されたノンドープポリシリコンパターン40に導電型がP型のBF2+イオンを注入する工程と、BF2+イオンが注入されたポリシリコン抵抗体8を酸素雰囲気中でアニールする第2アニール工程によって半導体装置を形成し、第1アニール工程は、不純物を注入する前で、ポリシリコン膜形成の後に行われ、処理時間が不純物の量に対応する。

(もっと読む)

半導体装置の製造方法

【課題】製造工程を簡略化することができる半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に薄膜抵抗体15を構成する金属薄膜およびバリアメタル16を構成するバリアメタル薄膜を形成する。そして、金属薄膜およびバリアメタル薄膜をパターニングし、薄膜抵抗体15と当該薄膜抵抗体15上にバリアメタル膜16aを形成する。その後、バリアメタル膜16a上に絶縁膜17を形成し、絶縁膜17にバリアメタルエッチング部16bを露出させる開口部17aと、コンタクト部を露出させるコンタクトホール17bを形成する。続いて、コンタクトホール17bを介してバリアメタル膜16aと電気的に接続される導電性薄膜18cを形成する。その後、導電性薄膜18cのうちバリアメタルエッチング部16b上に位置する部分をウェットエッチングによってパターニングし、バリアメタル膜16aのうちバリアメタルエッチング部16bをパターニングする。

(もっと読む)

半導体装置

【課題】小型化、薄型化、軽量化を実現した半導体装置の提供を課題とする。また、作製時間を短縮し、歩留まりを向上することができる半導体装置の作製方法の提供を課題とする。

【解決手段】トランジスタと、トランジスタ上に設けられた絶縁層と、絶縁層に設けられた開口部を介して、トランジスタのソース領域又はドレイン領域に電気的に接続された第1の導電層(ソース配線又はドレイン配線に相当)と、絶縁層及び第1の導電層上に設けられた第1の樹脂層と、第1の樹脂層に設けられた開口部を介して、第1の導電層に電気的に接続された導電性粒子を含む層と、第2の樹脂層及びアンテナとして機能する第2の導電層が設けられた基板とを有する。上記構成の半導体装置において、第2の導電層は、導電性粒子を含む層を介して、第1の導電層に電気的に接続されている。また、第2の樹脂層は、第1の樹脂層上に設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】同一半導体基板上に、トランジスタ素子、及び、容量素子、及び、抵抗素子を有する半導体装置において、十分な機能を有する容量素子を提供する。

【解決手段】容量素子をアクティブ領域上、抵抗素子を素子分離領域上に同一の多結晶シリコンで形成した後、CMPやエッチバック等で、所望の抵抗体の膜厚になるまで、基板表面を平坦化させながら削る。この時、アクティブ領域と、素子分離領域との高さの違いによって、膜厚の薄い抵抗素子と、膜厚の厚い容量素子の上部電極が形成される。容量素子の上部電極が十分な膜厚を持つので、コンタクトの突き抜けや、高抵抗化に伴う電圧依存性の増加などの特性劣化が防止され、アナログ回路に必要な高抵抗素子とプロセスを共通化することが可能であり、かつ、十分な機能を有する容量素子を製造することができる。

(もっと読む)

キャパシタおよび半導体装置

【課題】微細化した半導体集積回路において用いられるキャパシタを提供する。

【解決手段】誘電体の一つの面に接して設けられた、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有する仕事関数が5.0電子ボルト以上、好ましくは5.5電子ボルト以上のn型半導体による電極を有するキャパシタである。電極の仕事関数が高いため、誘電体のポテンシャル障壁が高くなり、誘電体が10nm以下と薄くても十分な絶縁性を保てる。特に、誘電体が、high−k材料である場合に顕著な効果が認められる。

(もっと読む)

半導体装置

【課題】消費電力を極力抑制することで電源の安定化を実現する半導体装置を提供する。

【解決手段】ロジック部11、メモリ部12、ロジック部とメモリ部の一方又は両方の動作頻度を検出する検出部13、検出部の検出結果に基づきロジック部及びメモリ部の一方又は両方にしきい値制御信号を供給するしきい値制御部14を有する半導体装置である。ロジック部とメモリ部の各々は複数のトランジスタを有しており、複数のトランジスタの各々は、論理信号が入力される第1のゲート電極と、しきい値制御信号が入力される第2のゲート電極と、半導体膜とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】LDMOSトランジスタとESD保護素子とを有する半導体装置において、製造工程が簡単であるとともに、所望の特性を確保しつつ従来に比べてより一層の高密度化が可能な半導体装置及びその製造方法を提供する。

【解決手段】LDMOSトランジスタ形成領域のゲート電極18aと素子分離膜11bの重なり幅をA1、ゲート電極18aとドレイン領域23bとの間隔をB1とし、ESD保護素子形成領域のゲート電極18と素子分離膜11cとの重なり幅をA2、ゲート電極18bとアノード領域22cとの間隔をB2としたときに、A1≧A2、且つB1<B2の関係を満足するように、ゲート電極18a、素子分離膜11b、ドレイン領域20a、ゲート電極18b、素子分離膜11c及び前記アノード領域22cを形成する

(もっと読む)

保護素子及び保護素子を備えた半導体装置

【課題】比較的小さい面積で形成することができ、かつ、素子サイズの微小化が進んでも保護素子として動作させることを可能にする、保護素子を提供する。

【解決手段】半導体基板1に形成された、第1導電型のウェル領域3と、この第1導電型のウェル領域3に隣接して形成された、第2導電型のウェル領域4と、第1導電型のウェル領域3に形成された、第2導電型チャネルのMOSトランジスタと、第1導電型のウェル領域3とMOSトランジスタのソース領域とMOSトランジスタのゲートとに電気的に接続された第1の配線と、MOSトランジスタのドレイン領域と第2導電型のウェル領域4とに電気的に接続された第2の配線とを含む保護素子を構成する。

(もっと読む)

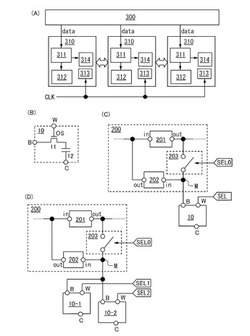

半導体回路及びその駆動方法、並びに記憶装置、レジスタ回路、表示装置、及び電子機器

【課題】トランジスタのしきい値電圧を最適な値に保持可能な半導体回路を提供すること。またトランジスタのしきい値電圧を制御可能な半導体回路、及びその駆動方法を提供すること。また上記半導体回路を適用した記憶装置、表示装置、及び電子機器を提供すること。

【解決手段】被制御トランジスタのバックゲートに接続されるノードに、ダイオードと第1の容量素子を設け、トランジスタのしきい値電圧が最適になるように所望の電圧を印加可能で且つその電圧を保持することができる構成とし、さらにダイオードに並列に接続された第2の容量素子を設け、当該ノードの電圧を一時的に変化させられる構成とすればよい。

(もっと読む)

半導体装置

【課題】大量生産が可能で、かつ従来の小型素子とは異なる構造を有する半導体装置を提供する。また、強度を向上させることが可能であり、作製段階における素子の破壊を抑制することができ、信頼性及び歩留まりの高い半導体装置の構造、及び半導体装置の作製方法を提供することを目的としている。

【解決手段】集積回路を有する層と、集積回路を有する層上に形成され、集積回路を有する層と電気的に接続された第1の端子と、第1の端子上に形成され、第1の端子と電気的に接続されたアンテナとして機能する導電層と、集積回路を有する層上に形成され、集積回路を有する層と、アンテナとして機能する導電層と、第1の端子と電気的に接続されていない第2の端子を有する。

(もっと読む)

DC−DCコンバータ及びその作製方法

【課題】単一な高電圧の入力電圧で駆動し、電圧変換回路及び制御回路を有するDC−DCコンバータを得ること、及び、DC−DCコンバータの占有面積の増大を抑制する。

【解決手段】入力電圧が印加される入力端子と、入力端子と接続され第1のトランジスタを有する電圧変換回路と、電圧変換回路を制御し珪素材料をチャネル形成領域に有する第2のトランジスタを有する制御回路と、入力端子と制御回路との間に設けられ入力電圧を入力電圧より低い電圧である電源電圧に変換する第3のトランジスタとを有し、第1のトランジスタ及び第3のトランジスタは酸化物半導体材料をチャネル形成領域に有するトランジスタであり、第2のトランジスタ、並びに、第1のトランジスタ及び第3のトランジスタは、絶縁膜を介して積層されているDC−DCコンバータ及びその作製に関する。

(もっと読む)

半導体装置の製造方法

【課題】シート抵抗のバラツキの少ない、さらに製造工程を短くすることができる製造方法を提供する。

【解決手段】半導体層が積層した半導体領域に不純物イオンを注入して、抵抗素子を形成する半導体装置の製造方法において、第1の半導体層4上に第2の半導体層5が積層され、第1の半導体層からなる抵抗素子を形成する際、第2の半導体層の厚さを変えることで、第1の半導体層に達する不純物イオンの量を制御し、予め設定されたシート抵抗の抵抗素子を形成する。

(もっと読む)

集積磁気薄膜増強回路素子を有する磁気抵抗ランダムアクセスメモリ(MRAM)

コア付きインダクタ素子およびその製造方法

【課題】半導体基板上に形成するインダクタのインダクタンスを大きくすること。

【解決手段】半導体基板上に形成された少なくとも1層からなるコイル配線のコイル中央孔に別基板に形成されたコアを挿入する。コアをコイル中央孔に固定した後、別基板は分離する。コアは別基板に接合材を介してコア材(磁性体)の薄板を付着させて、パターニングする。半導体基板上に形成されたコイル中央孔は流動性接着剤が入っていて、コアを挿入した後に流動性接着剤が硬化してコアが固定される。コアが固定された後に接合剤の接着力を低下させて別基板を分離する。コア材はバルクと同じ高透磁率を有するので、非常に大きなインダクタンスを持つインダクタを形成できる。

(もっと読む)

コア付きインダクタ素子およびその製造方法

【課題】半導体基板上に形成するインダクタのインダクタンスを大きくすること。

【解決手段】半導体基板上に形成された少なくとも1層からなるコイル配線のコイル中央孔に別基板に形成されたコアを挿入する。コアをコイル中央孔に固定した後、別基板は分離する。コアは別基板に接合材を介してコア材(磁性体)の薄板を付着させて、パターニングする。半導体基板上に形成されたコイル中央孔は流動性接着剤が入っていて、コアを挿入した後に流動性接着剤が硬化してコアが固定される。コアが固定された後に接合剤の接着力を低下させて別基板を分離する。コア材はバルクと同じ高透磁率を有するので、非常に大きなインダクタンスを持つインダクタを形成できる。

(もっと読む)

半導体装置およびその製造方法

【課題】工程が簡単で、よりラッチアップに強いCMOS構造を得る。

【解決手段】1×1018cm−3から1×1019cm−3の高不純物濃度の半導体基板2を用い、CMOS構造のP型ウェル4とN型ウェル5の境界に設けられた溝分離部13の先端部分がその高不純物濃度領域に達する(エピタキシャル層3を貫通して半導体基板2の領域に至る)ように深く形成することにより、従来のように溝分離部13よりも更に深い領域(溝分離部13の下側)を電子が通過することなく、従来のようにウェル領域内にN+埋め込み層やP+埋め込み層を基板深く埋め込む必要もなく、簡便な方法で、よりラッチアップに強いCMOS構造を得ることができ、コスト性能の両方に優れた半導体装置1を得ることができる。

(もっと読む)

半導体製造方法および半導体装置

【課題】ウェーハテスト後のウェーハ状態において所望の回路を印刷処理により容易に形成することが可能な半導体製造方法および半導体装置を提供することを課題する。

【解決手段】本発明に係る半導体製造方法は、ウェーハの被描画パターン形成領域に所定の深さを有する溝部を形成する工程、ウェーハに対してトリミング要否の検査を行う工程、前記ウェーハにおけるトリミング必要なウェーハの前記溝部に導電性溶剤を射出し描画パターンを描画する工程、描画パターンを描画した後、脱気および低温アニールする工程、脱気および低温アニールした成膜後、当該成膜表面を平坦化する工程、および平坦化した後、高温アニールする工程、を有する。

(もっと読む)

41 - 60 / 527

[ Back to top ]