Fターム[5F038EZ17]の内容

Fターム[5F038EZ17]に分類される特許

21 - 40 / 527

硬化性組成物および該組成物を用いた絶縁膜

【課題】本発明の目的は、特定の構造を有するポリシロキサン化合物を含有する高誘電率でありかつ絶縁性に優れた薄膜となる硬化性組成物に関するものである。本発明の硬化性組成物を硬化して得られる薄膜は、特に薄膜トランジスタのゲート絶縁膜やコンデンサ用材料として有用である。

【解決手段】アルケニル基を有する化合物(A)および特定の構造を有するポリシロキサン化合物(B)からなるヒドロシリル化反応性を有する硬化性組成物であり、得られる硬化物における1kHzでの比誘電率が3.5以上であることを特徴とする硬化性組成物により達成できる。

(もっと読む)

半導体装置

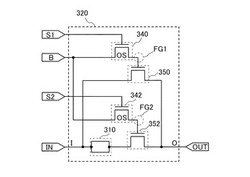

【課題】プログラマブルなアナログデバイスを提供する。また、電源電位の供給が遮断されたときでもデータの保持が可能で、且つ、低消費電力化が可能なアナログデバイスを提供する。

【解決手段】アナログ素子を含むユニットセルにおいて、ユニットセルのスイッチとして、第1乃至第4のトランジスタを用い、第1のトランジスタと第2のトランジスタとが接続された第1のノード、及び、第3のトランジスタと第4のトランジスタが接続された第2のノードの電位を制御することで、ユニットセルの出力を導通状態、非導通状態、又はアナログ素子を介した導通状態のいずれかに切り替える半導体装置を提供する。

(もっと読む)

半導体装置

【課題】半導体集積回路における消費電力を低減する。また、半導体集積回路における動作の遅延を低減する。

【解決手段】記憶回路が有する複数の順序回路のそれぞれにおいて、酸化物半導体によってチャネル形成領域が構成されるトランジスタと、該トランジスタがオフ状態となることによって一方の電極が電気的に接続されたノードが浮遊状態となる容量素子とを設ける。なお、酸化物半導体によってトランジスタのチャネル形成領域が構成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。そのため、記憶回路に対して電源電圧が供給されない期間において当該トランジスタをオフ状態とすることで、当該期間における容量素子の一方の電極が電気的に接続されたノードの電位を一定又はほぼ一定に保持することが可能である。その結果、上述した課題を解決することが可能である。

(もっと読む)

トリミング回路、トリミング回路の駆動方法

【課題】信頼性の高いトリミング回路を提供する。書き換え可能なトリミング回路を提供する。信頼性の高いトリミング回路の駆動方法を提供する。書き換え可能なトリミング回路の駆動方法を提供する。

【解決手段】オフリーク電流が極めて小さいトランジスタのソース電極またはドレイン電極に接続された記憶ノードと、該記憶ノードにゲート電極が接続されたトランジスタを用いてトリミング回路を構成する。また、該オフリーク電流が極めて小さいトランジスタを用いて、該記憶ノードにゲート電極が接続されたトランジスタのソース電極とドレイン電極に対して並列に接続された素子または回路のトリミング状態を制御する。

(もっと読む)

半導体装置

【課題】導体半導体接合を用いて、優れた特性を示す、あるいは、作製の簡単な、あるいは、より集積度の高い電界効果トランジスタを提供する。

【解決手段】半導体層の電子親和力よりも仕事関数の小さな導体との接合においては、導体より半導体層にキャリアが注入された領域が生じる。そのような領域を電界効果トランジスタ(FET)のオフセット領域、あるいは、インバータ等の半導体回路の抵抗として用いる。また、ひとつの半導体層中にこれらを設けることにより集積化した半導体装置を作製できる。

(もっと読む)

加算器

【課題】新たなロジックインメモリ構造を提供する。また、より消費電力の低い信号処理回路を提供する。また、より消費電力の低い電子機器を提供する。

【解決手段】オフ電流の低いトランジスタを用いて記憶素子を構成することで、記憶機能と演算機能を組み合わせた回路を提供する。オフ電流の低いトランジスタを用いることで、オフ電流の低いトランジスタのソースまたはドレインの一方と、他のトランジスタのゲートとの間などに電荷を保持することができる。そのため、オフ電流の低いトランジスタのソース又はドレインの一方と、他のトランジスタのゲートと、の間のノード等を記憶素子として用いることができる。また、加算器の動作に伴うリーク電流を著しく低減することができる。これにより、消費電力の低い信号処理回路を構築することが可能である。

(もっと読む)

半導体装置とその動作方法

【課題】半導体装置において、消費電力を低減する。また、スタンバイ回路を少ない素子で構成し、半導体装置の回路面積の増大を防ぐ。

【解決手段】半導体装置に備えるスタンバイ回路をトランジスタ一つのみで構成し、該トランジスタに供給する電圧を切り替えることで、半導体装置の出力電流を制御する。これにより、スタンバイ状態での半導体装置の出力電流をほぼゼロにすることができるため、消費電力の低減が可能になる。なお、トランジスタの半導体層に酸化物半導体を用いることで、リーク電流を極小に抑えることができる。

(もっと読む)

半導体装置

【課題】ラッチ型メモリが搭載されたCPUを動作させるに際して、処理内容に応じて常時記憶方式と終了時記憶方式のいずれかを選択し、ラッチ型メモリが搭載されたCPUの消費電力を低減する。

【解決手段】ラッチ型メモリが搭載されたCPUを動作させるに際して、電源のオンオフの繰り返し動作が多い場合には常時記憶方式とし、電源のオンオフの繰り返し動作が少ない場合には終了時記憶方式とする。常時記憶方式と終了時記憶方式のどちらを選択するかは、消費電力に応じて決定したしきい値をもとにして決定する。

(もっと読む)

信号処理装置

【課題】消費電力を抑えることができる信号処理装置を提供する。

【解決手段】信号処理装置が有する記憶回路に、酸化物半導体にチャネルが形成されるトランジスタを適用することで、電力の供給を停止している間もデータの保持(記憶)を可能とする。記憶回路に記憶されているデータは、信号処理装置への電力の供給を停止している間も、破壊すること無く読み出すことができる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】消費電力を抑えることができる、プログラムユニットを用いた半導体装置を提供する。また、信頼性の高い、プログラムユニットを用いた半導体装置を提供する。さらに集積度の高い、プログラムユニットを用いた半導体装置を提供する。

【解決手段】PLD等のロジックセル間の接続構造を変更する機能を有する半導体回路において、ロジックセル間を接続や切断、あるいはロジックセルへの電源の供給を、オフ電流またはリーク電流が小さい絶縁ゲート電界効果型トランジスタを用いたプログラムユニットによって制御する。プログラムユニットにはトランスファーゲート回路を設けてもよい。駆動電圧を下げるため、プログラムユニットには容量素子を設けて、その電位をコンフィギュレーション時と動作期間とで異なるものとしてもよい。

(もっと読む)

論理回路

【課題】電源電位の供給が遮断されたときでも論理回路の切り替え状態の保持が可能で、電源投入後の論理ブロックの起動時間が短く、低消費電力化が可能な、否定論理積(NAND)回路および否定論理和(NOR)回路を容易に切り替えることができる論理回路を提供する。

【解決手段】酸化物半導体を有するトランジスタを介して、ノードへの電荷保持状態を切り替えることによって、否定論理積(NAND)回路および否定論理和(NOR)回路を容易に切り替えることができる。当該トランジスタにはワイドバンドギャップ半導体である酸化物半導体材料を用いることによって、トランジスタのオフ電流を十分に小さくできるため、ノードに保持した電荷の状態を不揮発とすることができる。

(もっと読む)

半導体装置

【課題】消費電力が低減された半導体装置を提供することである。

【解決手段】入力電位および基準電位が入力される差動増幅器、利得段および出力電位が出力される出力段を有する半導体装置において、該出力段にオフ状態でのリーク電流が低いトランジスタを配置することで、該利得段から供給される電位が一定に保持される半導体装置である。また、オフ状態でのリーク電流が低いトランジスタとしては、酸化物半導体層を有し、且つ酸化物半導体層にチャネル形成領域を有するトランジスタを用いることである。

(もっと読む)

半導体装置

【課題】処理実行中に電源をオフしてもデータが保持され、且つ従来よりも占有面積が小さいDフリップフロップ回路を有する半導体装置を提供する。

【解決手段】入力端子が、第1のトランスミッションゲートの第1の端子に電気的に接続され、第1のトランスミッションゲートの第2の端子が、第1のインバータの第1の端子及び機能回路の第2の端子に電気的に接続され、第1のインバータの第2の端子及び機能回路の第1の端子が、第2のトランスミッションゲートの第1の端子に電気的に接続され、第2のトランスミッションゲートの第2の端子が第2のインバータの第1の端子及びクロックドインバータの第2の端子に電気的に接続され、第2のインバータの第2の端子及びクロックドインバータの第1の端子は出力端子に電気的に接続されており、機能回路にはオフ電流が小さいトランジスタと容量素子との間にデータ保持部を有する半導体装置とする。

(もっと読む)

半導体集積回路

【課題】半導体集積回路における消費電力を低減すること。また、半導体集積回路における動作の遅延を低減すること。

【解決手段】記憶回路が有する複数の順序回路のそれぞれにおいて、酸化物半導体によってチャネル形成領域が構成されるトランジスタと、該トランジスタがオフ状態となることによって一方の電極が電気的に接続されたノードが浮遊状態となる容量素子とを設ける。なお、酸化物半導体によってトランジスタのチャネル形成領域が構成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。そのため、記憶回路に対して電源電圧が供給されない期間において当該トランジスタをオフ状態とすることで、当該期間における容量素子の一方の電極が電気的に接続されたノードの電位を一定又はほぼ一定に保持することが可能である。その結果、上述した課題を解決することが可能である。

(もっと読む)

プログラマブルロジックデバイス

【課題】電源電位の供給が遮断されたときでもコンフィギュレーションデータの保持が可能で、電源投入後のプログラマブルスイッチの起動時間が短い、低消費電力化が可能なプログラマブルロジックデバイスを提供すること。

【解決手段】各論理ブロック間の配線接続を制御するプログラマブルスイッチのメモリ部のトランジスタに、トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドバンドギャップ半導体である酸化物半導体材料を用いて当該トランジスタを構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、電源電位の供給が遮断されたときでもコンフィギュレーションデータを保持することが可能となる。

(もっと読む)

半導体集積回路およびその製造方法

【課題】半導体集積回路に電源を投入後の通常の動作時にリーク電流の抑制と同時にクランプ電圧の増大防止または低下を図り、保護用MOSトランジスタのゲート電位が変動しにくい保護回路を有する半導体集積回路及び製造方法を提供する。

【解決手段】RCMOS型のESD保護回路1において、保護用MOSトランジスタ5は、内部回路6の内のチャネルの導電型が同じトランジスタに対して、仕事関数差を有する異なる電極材料からゲート電極が形成され、または、仕事関数差を設けるために異なる導電型の半導体電極材料からゲート電極が形成されることによって、単位チャネル幅あたりのリーク電流量が、より減る向きに閾値電圧が異なっている。

(もっと読む)

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

拡散抵抗素子およびその製造方法

【課題】ノイズおよび抵抗バラツキが小さな拡散抵抗の製造方法を提供することを目的とする。

【解決手段】半導体基板の表面付近にp型拡散層114を形成する工程と、拡散抵抗体となるp型拡散層114の第1領域の表面上に、層間絶縁膜とは異なる絶縁膜であって当該第1領域の表面を保護するカバー膜125を形成する工程と、カバー膜125を形成する工程の後、カバー膜125の前記第1領域に接する第2領域に前記第1領域よりも高い濃度で拡散抵抗体のコンタクト部となるp型拡散層116を形成する工程とを含む。

(もっと読む)

コンパレータ、及びそれを用いた半導体装置

【課題】新たな構成のチョッパ型のコンパレータを提供する。

【解決手段】コンパレータは、インバータと、容量素子と、第1のスイッチと、第2のスイッチと、第3のスイッチとを有し、インバータの入力端子と出力端子とは、第1のスイッチを介して電気的に接続され、インバータの入力端子は、容量素子の一対の電極のうちの一方と電気的に接続され、容量素子の一対の電極のうちの他方は、第2のスイッチを介して参照電位が与えられ、入力された信号電位は第3のスイッチを介して容量素子の一対の電極のうちの他方に与えられ、インバータの出力端子から出力される電位を出力信号とし、第1のスイッチは、チャネルが酸化物半導体層に形成されるトランジスタを用いて構成される。

(もっと読む)

半導体装置

【課題】半導体集積回路の微細化に伴い非常に短くなったゲート長を有するトランジスタにおいて、ゲート絶縁膜におけるリーク電流の発生を抑制し、トランジスタとしての機能を高めることが可能な半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面に形成された1対のソース/ドレイン領域と、1対のソース/ドレイン領域に挟まれる領域上であって、主表面に接するように形成されたゲート絶縁膜AFEと、ゲート絶縁膜AFEの上面に接するように形成されたゲート電極POとを備える。上記1対のソース/ドレイン領域の一方から他方へ向かう方向のゲート電極POの長さは45nm未満である。ゲート絶縁膜AFEは反強誘電体膜を有する。

(もっと読む)

21 - 40 / 527

[ Back to top ]