Fターム[5F044QQ07]の内容

ボンディング (23,044) | ワイヤレスボンディング用半導体チップ (2,288) | チップの両面に電極があるもの (28)

Fターム[5F044QQ07]に分類される特許

1 - 20 / 28

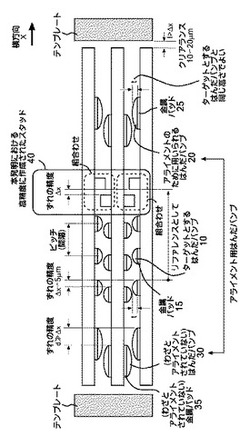

はんだバンプのセルフアライメントに利用するスタッドの作成

【課題】 3次元実装のプロセスに親和性のある、高精度のアライメントを提供すること。

【解決手段】 複数のシリコンチップ間においてはんだバンプが溶融した場合に、複数のシリコンチップ同士の横方向の相対的な動きを規制する複数のスタッド(40)の組合わせであって、複数のシリコンチップ間に配置される複数のはんだバンプ(10)のピッチに従い、これらの横方向の位置をリファレンスにして横方向位置が決定されていて、複数のシリコンチップが横方向に相対的に移動した場合に相対的に動きが規制されて、複数のシリコンチップのそれぞれに設定された複数のはんだバンプ同士の横方向位置が(高さ方向において)整列するように、一方のシリコンチップおよび他方のシリコンチップにおいて複数のスタッド(40)が設けられる。

(もっと読む)

半導体装置の製造方法及び半導体装置、電子機器

【課題】空洞部の破壊を防ぐと共に、基板間の接続の信頼性を向上できるようにした半導体装置の製造方法及び半導体装置、電子機器を提供する。

【解決手段】第1の基板は、第1の面と第2の面とを有する第1の基材と、第1の基材の第1の面側に設けられた犠牲層と、第1の基材の第1の面と第2の面との間を貫通する貫通電極と、貫通電極と第1の基材との間に設けられた絶縁膜と、を有する。第2の基板は、第3の面を有する第2の基材と、第2の基材の第3の面側に設けられたバンプと、第2の基材の第3の面側に設けられ、バンプを囲む環状導電部と、を有する。第2の面と第3の面とを対向させた状態で、貫通電極とバンプとを接続すると共に、第1の基板の周縁部を環状導電部に埋入させる実装工程と、実装工程の後で、犠牲層をエッチングして第1の基材の第1の面側に空洞部を形成するエッチング工程と、を含む。

(もっと読む)

配線シート付き配線体、半導体装置、およびその半導体装置の製造方法

【課題】製造工程を簡略化することのできる配線シート付き配線体、半導体装置、およびその半導体装置の製造方法を提供する。

【解決手段】第1主面11にソース電極14およびゲート電極15が形成されかつ第2主面12にドレイン電極13が形成されたスイッチング素子10と、ドレイン電極13に接続された導電層積層基板80とを備える半導体装置1に対して、配線シート付き配線体30は、上側配線構造体として適用される。配線シート付き配線体30は、ソース電極14に接続される第1配線体40と、ゲート電極15に接続されるゲート端子が設けられた配線シート60とを備える。第1配線体40においてソース電極14が接続される面に配線シート60が取り付けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストで高い耐熱性ワイヤレス接合を有する半導体装置およびその製造方法を提供する。

【解決手段】実装基板8と、実装基板8上に配置された信号配線電極12と、実装基板8上に若しくは実装基板8を貫通して配置されたパワー配線電極6と、信号配線電極12と電気的に接合可能なゲートパッド電極GPおよびパワー配線電極6と電気的に接合可能なソースパッド電極SPを有する半導体デバイス16と、信号配線電極12とゲートパッド電極GPとの間に配置された第1金属粒子接合層18Gと、パワー配線電極6とソースパッド電極SPとの間に配置された第2金属粒子接合層18Sとを備え、半導体デバイス16が実装基板8上にフリップチップ接続された半導体装置1およびその製造方法。

(もっと読む)

半導体装置の製造方法

【課題】生産性および信頼性を向上することができる半導体装置の製造方法を提供すること。

【解決手段】第一の接合工程では、半導体チップ10、第一樹脂層11、半導体チップ12、第二樹脂層13、半導体チップ14を積層することにより得られ、半導体チップ10,12同士、半導体チップ12,14同士が半田接合されていない状態の積層体2を加熱して、半導体チップ10,12間、半導体チップ12,14間の半田接合を行う。その後、半田接合した積層体2を基材18上に設置する。積層体2の基材18への接続用端子162と、基材18の積層体2への接続用端子181とが当接するように、積層体2を基材18上に設置する。

(もっと読む)

半導体装置及びその製造方法

【課題】電子部品の生じた熱を金属板及びモールド樹脂を介して効率よく放熱でき、且つ、電気絶縁性を確保することのできる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、両面に電極を有する電子部品20と、電子部品20が配置され、電極の一方と電気的に接続された基板30と、電子部品20上に配置され、電極の他方と電気的に接続された金属板40と、電子部品20、基板30の少なくとも一部、金属板40を一体的に封止するモールド樹脂50を備える。そして、対向配置された2つの部材としての、電子部品20と基板30との間、及び、電子部品20と金属板40との間の少なくとも一方に、樹脂シート60が配置される。樹脂シート60は、ビアホール内に導電材料を配置してなる接続ビア61を有し、樹脂シート60を挟む2つの部材は、接続ビア61に接しつつ接続ビア61を介して接合される。

(もっと読む)

半導体装置の製造方法、接着剤層付き半導体ウェハの製造方法、半導体素子付き半導体ウェハの製造方法、及び半導体ウェハ積層体の製造方法

【課題】ボイドが低減され、研削後の反りを小さくすることができる接着剤層付き半導体ウェハの製造方法、並びに、接着剤層付き半導体ウェハを用いる、半導体装置の製造方法を提供する。

【解決手段】金属バンプ12が形成された回路面を有する半導体ウェハ10の回路面上に、2種類以上の液状感光性接着剤6,7の塗布及び塗膜の光照射によって、2層以上の構造を有し最表面層がフラックス成分を含有するBステージ化された接着剤層を設けて接着剤層付き半導体ウェハ40を得る工程と、接着剤層付き半導体ウェハ40と、他の半導体ウエハ50とを、接着剤層付き半導体ウェハ40の接着剤層を挟んで圧着する工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体素子の配置位置による電気特性のばらつきを抑制可能な半導体装置及び製造歩留り向上が可能な半導体装置の製造方法を提供する。

【解決手段】複数の配線パターン200を有する基板20と、半導体素子10と、複数の配線パターン200と半導体素子10とを電気的に接続する接続部材50とを有する半導体装置において、基材の両面に粘着材層を有し、基板20と半導体素子10とを貼りあわせる粘着部材40を、複数の配線パターン200の間に配置する半導体装置及びその製造方法。

(もっと読む)

半導体装置の製造方法

【課題】半導体チップの組立工程におけるハンドリング性を向上し、しかも、半導体チップの損傷を回避する半導体装置の製造方法を提供すること。

【解決手段】ダイシングライン16によって区画された複数の半導体チップ4を含む半導体ウエハ2を準備する第1の工程と、半導体ウエハ2に支持板13を付着する第2の工程と、半導体ウエハ2および支持板13をダイシングライン16に沿って切断し、半導体チップ4および分割された支持板13からなる積層体3を形成する第3の工程と、積層体3を配線基板18に搭載し、積層体3の半導体チップ4および配線基板18を電気的に接続する第4の工程とを有する半導体装置1の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】種類の異なる半導体チップの間で接合不良が発生することを防止した半導体装置及びその製造方法を提供する。

【解決手段】配線基板2の一面に実装されたチップ積層体3は、配線基板2の一面とは反対側から順に、一面側に第1のバンプ電極12と他面側に第2のバンプ電極13とを有する複数のメモリーチップ10a〜10dを、それぞれの一面と他面とを対向させながら、それぞれの間にある第1のバンプ電極12と第2のバンプ電極13とを接合して積層し、その上に、一面側に第3のバンプ電極15と他面側に第4のバンプ電極16とを有するロジックチップ11を、その一面と、その下にあるメモリーチップ10dの他面とを対向させながら、その間にある第2のバンプ電極13と第3のバンプ電極15とを接合部材18を介して接合して積層した構造を有する。

(もっと読む)

3次元でパッケージされた集積回路に対するダイ間結合の間の静電放電ダメージへの感受性の低減

本発明は、電子集積回路パッケージの製作、より具体的には3次元でパッケージされた集積回路を製造する際の静電放電ダメージの軽減に関する。一実施形態では、第2層ダイが第1層ダイと接触して配置されるとき、第2層ダイおよび第1層ダイ上の他の信号導電バンプおよびパワー導電バンプが電気的に接触する前に、第2層の基板と電気的に結合された第2層の周辺部付近の導電バンプが、第1層の基板と電気的に結合された第1層の対応する導電バンプと接触する。  (もっと読む)

(もっと読む)

集積回路構造

【課題】導電ビア(TSV)に接続されるウェハ背部の相互接続構造を有する集積回路構造を提供する。

【解決手段】集積回路構造は、正面と背面を有する半導体基板と、半導体基板を貫通する導電ビアと、半導体基板の背面上の金属構造と、を備える。金属構造は、導電ビアを被覆して、接触する金属パッド、及び、導電ビア上の金属線を含む。金属線は、デュアルダマシン構造を含む。集積回路構造は、更に、金属線上のバンプを具備する。

(もっと読む)

光伝送モジュール

【課題】フリップチップ実装用でないワイヤボンディング用の光素子を用いてもフリップチップ実装を実現でき、かつ、放熱性に優れた光伝送モジュールを提供する。

【解決手段】基板2はケース筐体8に収納され、基板2に搭載する側の面に電極が1列に形成された光素子3を、基板2にフリップチップ実装する光伝送モジュールであって、光素子3の搭載面と反対側の面をベース部材4に接合してフリップチップ実装用モジュール5を形成し、そのフリップチップ実装用モジュール5を基板2にフリップチップ実装すると共に、フリップチップ実装用モジュール5をケース筐体8と当接させて放熱路を形成したものである。

(もっと読む)

半導体装置、積層半導体装置および積層半導体装置の製造方法

【課題】TSVを有するSOI基板を積層する場合に余分な圧力を加えることなく、少ない圧力で確実にバンプ間を接合する。

【解決手段】絶縁層および絶縁層に接して形成されたSOI層を有する基板と、基板の表面および裏面の間を貫通する貫通孔と、貫通孔に形成された、表面および裏面の間を電気的に結合する貫通結合部と、表面または裏面における貫通結合部の端部を露出する窪み部と、貫通結合部の端部に接して窪み部に形成された、他の基板と電気的に接触する部材となる接触部材と、を備えた半導体装置を提供する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板に設けられる貫通孔および貫通電極の形成状態および出来映えを容易に確認可能にし、貫通孔および貫通電極の品質向上と、接続不良の早期発見を可能にする技術を提供する。

【解決手段】半導体基板11と、半導体基板11の表面に設けられた内部電極12Aおよび内部電極12Bと、半導体基板11を厚み方向に貫通して内部電極12Aに到達し、内部電極12Aと電気的に接続された第一の貫通電極17Aと、半導体基板11および内部電極12Bを厚み方向に貫通する第二の貫通電極17Bと、半導体基板11の裏面に設けられ、第一の貫通電極17Aと電気的に接続された金属配線18とを備える。

(もっと読む)

粘着性保護層を有する半導体ウェハ

【課題】プロセスの簡略化及び全体コストの低下が可能な、粘着性保護層を有する半導体ウェハを提供する。

【解決手段】粘着性保護層を有する半導体ウェハは、第1の表面11とこれに対向する第2の表面13を有する本体15と、第2の表面13に形成した複数の電極パッド17と、本体15の第2の表面13及び複数の電極パッド17上に形成した保護層19とを含み、保護層19の材料は感光性粘着剤、熱硬化性粘着剤、及び誘電材料を含む。保護層19は、ウェハ表面における回路の大気中の水分や塵との接触を阻止できるだけではなく、パターニングや粘着が可能で、後工程において、保護層が有する粘着性を利用してウェハと回路基板を結合できるため、ウェハの所定の表面に粘着剤を塗布する必要がなく、パッケージングプロセスにおいてウェハと回路基板との結合工程を大幅に簡略化できる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】半導体基板の貫通電極の接続状態を、容易に検査し得る半導体装置を提供する。

【解決手段】半導体基板1に開口面積が大、中、小の少なくとも3種類の貫通孔3、4、5a、5b、5cを形成する工程と、開口面積が異なる少なくとも3種類の貫通孔に導電層を形成し貫通電極4、5a、5b、5cを作成する工程と、3種類の貫通電極のうち、開口面積が大の貫通孔を有する貫通電極及び小の貫通孔を有する貫通電極の接続抵抗をそれぞれ測定することにより貫通電極の接続状態を判定する工程と、を有する。

(もっと読む)

積層された複数個の半導体素子を備えた半導体装置

【課題】ワイヤーボンディング方式を採用する必要がなく、従ってワイヤーボンディング方式の作用に起因する問題がない、積層された複数個の半導体素子(6、1014)を供えた半導体装置を提供する。

【解決手段】各半導体素子自体と共に、基板(2)と最下層半導体素子(6)との間及び各半導体素子間に配設されている絶縁性接着フィルム(4、8、12)に、独特な電気的接続手段を配設することによって、ワイヤーボンディング方式の必要性を回避する。

(もっと読む)

圧電振動子及び圧電発振器

【課題】 圧電振動素子の大きさの影響を受けずに製造を容易とする。

【解決手段】 平面視四角形の容器体10の一方の主面に設けられた凹部13内に設けられている搭載パッド14と圧電振動素子20に設けられている励振電極22と接続する引回しパターン23とが導電性接着材Dで接合され、平面視四角形状の蓋体30で容器体10の凹部13を気密封止した圧電振動子100であって、圧電振動素子20に設けられている引回しパターン23が、圧電振動素子20の両主面にのみ形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】低抵抗であって小型化が可能な半導体装置及びその製造方法を提供すること。

【解決手段】半導体チップ10に斜面部14を形成し、半導体チップ10の下面に複数の電極11を設け、半導体チップ10の上面に金属膜15を蒸着させ、斜面部14上の金属膜15を第2電極12とし、第1電極11と対応するリードフレーム20を接続し、第2電極12と対応するリードフレーム20とをストラップ13で接続することで、第1電極11及び第2電極12とリードフレーム20との導通路を形成する。

(もっと読む)

1 - 20 / 28

[ Back to top ]