Fターム[5F044RR01]の内容

ボンディング (23,044) | ワイヤレスボンディング関連事項 (2,154) | 複数チップのボンディング (221)

Fターム[5F044RR01]の下位に属するFターム

チップ同士ボンディング (81)

チップを積層してボンディング (82)

同一のリードに複数のチップをボンディング (2)

Fターム[5F044RR01]に分類される特許

21 - 40 / 56

半導体チップ、実装基板及び半導体装置の製造方法

【課題】 実装基板上の小型の半導体チップの位置および姿勢を自律的に制御する方法を提供する。

【解決手段】 チップ化された半導体チップを基板の電極に所望の位置および姿勢に搬送する半導体チップ搬送アライメント方法において、半導体チップの表面の電極を除く領域に、親水性材料からなる層と撥水性材料からなる層を分割して設け、半導体チップを液滴に含ませて実装基板の電極に搬送し、半導体チップを実装基板の電極に接続する工程とから構成され、これら上記の工程中で半導体チップが実装基板との相対位置、姿勢を半導体チップの親水性材料・撥水性材料と液滴との作用により自律的にアライメントを制御する。

(もっと読む)

半導体チップモジュール

【課題】大きさの異なる2個の半導体チップを隣接させてもアンダーフィルの流入量が過不足することを防止する。

【解決手段】本発明の半導体チップモジュール1は、配線板2上に、平面視大小異なる半導体チップ3、4、アンダーフィル5、アンダーフィル5の流出をせき止める1個の囲い6Aを備える。囲い6Aはアンダーフィル5の注入口7および半導体チップ3にのみアンダーフィル5を供給する溜池部8を有する。注入口7は、半導体チップ3、4の対向辺3a、4aと囲い6Aの一部6Aaにより囲まれた領域からなる。溜池部は、半導体チップ3の対向辺3aの一部3bと囲い6Aの一部6Aaにより囲まれた領域からなる。

(もっと読む)

半導体装置、半導体装置モジュール及び半導体装置モジュールの製造方法

【課題】複数の半導体素子で構成された半導体装置の生産時及び基板実装状態における不良発生に対して個々の半導体素子の諸特性を容易に検査することができ、良好な品質管理及び確実な不良解析を実現することが可能な半導体装置を提供することにある。

【解決手段】半導体装置30の単体状態においては複数の半導体素子が夫々電気的に独立した結線構造を呈しており、各半導体素子に個別に通電することにより諸特性を検査、解析することが可能となり、半導体装置30が実装されてなる半導体装置モジュール55の状態においては複数の半導体素子による並列回路からなる結線構造を呈しており、半導体装置実装用基板に設けられた一対のはんだ接合用電極パッド間44a、44bに電圧を印加することにより全ての半導体素子を駆動させることが可能となる。

(もっと読む)

電子部品実装装置及び実装方法

【課題】本発明の目的は信頼性の高い電子部品実装装置を提供することである。本発明の他の目的は保護シートの劣化の少ない電子部品実装装置を提供することである。本発明の更に他の目的は保護シートの高寿命化を可能にする電子部品実装装置を提供することである。

【解決手段】加熱した加圧部材と保護シートが密着した状態で装置が停止したとき、停止した状態が一定時間経過したことをきっかけとして、加圧ヘッドと保護シートの距離を離す。加圧部材と保護シートが密着していることを検知し、それが一定時間継続されたことをきっかけとし、加圧部材と保護シートを離すシステム。

(もっと読む)

サーマルヘッドおよびサーマルプリンタ

【課題】サーマルヘッドにおいてドライバーICと基板との電気的接続の信頼性を確保する。

【解決手段】発熱素子145が配置される基板110とドライバーIC120とを有するサーマルヘッド1であって、前記ドライバーIC120は、樹脂突起131と前記樹脂突起131に形成される接続端子135aを備えた第1の接続端子列137aと、前記第1の接続端子列137aより少ない数の接続端子135bを備えた第2の接続端子列137bとを備え、前記基板110は、接続端子135に接続される複数の実装端子115,116を備え、前記ドライバーIC120は、前記接続端子135が絶縁接着層150を介して前記実装端子115,116に固定されており、前記実装端子115,116は、面積が前記第1の接続端子列137aの中央部に対応する前記実装端子115の面積を基本として、それより大きい複数の異なる面積に形成されている。

(もっと読む)

電子部品実装装置及び接合不良検出方法

【課題】同時に複数電極を接合する電子部品実装において、複数電極に対して温度均一性が保障されない対象であっても、接合不良を検出できる電子部品実装装置及び接合不良検出方法を提供することを目的とする。

【解決手段】複数電極を有する基板8と複数電極を有するIC7を加熱加圧接合する過程において、任意の複数位置の基板下面温度を測定する温度計を備えることにより、接合中の接合不良を精度良く検知することが可能である。また、複数ICを同時に圧着するような場合にも個別に接合状態を把握することが可能となり、接合中に接合不良を精度良く検知することが可能である。

(もっと読む)

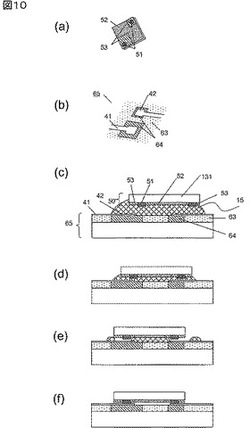

電子部品モジュールの製造方法

【課題】受動素子と能動素子とが同一のベース配線層に内蔵された構造の電子部品モジュールを簡略な製造プロセスで製造することができる電子部品モジュールの製造方法を提供することを目的とする。

【解決手段】受動素子としてのCR部品9と能動素子としてのICチップ8とを同一のベース配線層1に装着した構成の電子部品モジュール15の製造に際し、ベース配線層1の回路形成面2aに半田粒子7を含んだ接着剤層5Aを形成し、ICチップ8を先にベース配線層1に搭載して熱圧着した後にCR部品9を接着剤層5Aによってベース配線層1に接着し、その後に封止樹脂層を形成するための熱硬化シート12をCR部品9とICチップ8が接着されたベース配線層1の回路形成面2aに貼り合わせて熱圧着を行って、接着剤層5Aの硬化およびこの接着剤層5Aに含まれた半田粒子7の溶融を同時に行う。

(もっと読む)

電子部品モジュールの製造方法

【課題】受動素子と能動素子とが同一のベース配線層に内蔵された構造の電子部品モジュールを簡略な製造プロセスで製造することができる電子部品モジュールの製造方法を提供することを目的とする。

【解決手段】受動素子としてのCR部品9と能動素子としてのICチップ8とを同一のベース配線層1に装着した構成の電子部品モジュール15の製造に際し、ベース配線層1の回路形成面2aに半田粒子7を含んだ接着剤層5Aを形成し、CR部品9を先に搭載した後にICチップ8をベース配線層1に搭載して接着剤層5Aによってベース配線層1に接着し、その後に封止樹脂層を形成するための熱硬化シート12をCR部品9とICチップ8が接着されたベース配線層1の回路形成面2aに貼り合わせて熱圧着を行って、接着剤層5Aの硬化およびこの接着剤層5Aに含まれた半田粒子7の溶融を同時に行う。

(もっと読む)

取外し可能な相互接続構造体の製造方法

【課題】電子デバイス及びベース絶縁層の両方に損傷を与えることなく、電子デバイスをベース絶縁層から回収する方法を提供する。

【解決手段】電子デバイス18に第1の金属層24を適用する段階であって、電子デバイス18は1以上のI/Oコンタクト23を含み、第1の金属層24はI/Oコンタクト23の表面上に配置される段階と、電子デバイス18に取外し可能な層26を適用する段階とを含んでいる。取外し可能な層26は第1の金属層24に隣接して配置される。電子デバイス18又はベース絶縁層10に接着剤層16が適用される。接着剤層16を用いて電子デバイス18はベース絶縁層10に固定される。第1の金属層24及び取外し可能な層26は電子デバイス18とベース絶縁層10との間に配設される。

(もっと読む)

半導体デバイスの実装構造体及び実装構造体を用いた電子機器

【課題】良好なコプラナリティを有して歩留まりが高く、また低コストなパッケージスタック型に積層可能な実装構造体を提供し、さらには本実装構造体を適用することにより、高機能化や小型化を図った低コストの電子機器を提供する。

【解決手段】半導体パッケージ50の下面のはんだバンプ5が可撓性配線基板7の電極に溶融接続されており、半導体パッケージ50の側面および外部端子形成面とは表裏反対面を取り囲むように構成され、突出部9aを有する支持体9を備え、支持体9の側面の一部、及び上面の一部を可撓性配線基板7で包み込むように接着固定され、半導体パッケージ50の上面に電極が形成された実装構造体60とする。

(もっと読む)

半導体チップ及び半導体装置

【課題】電極数を極力低減すると共に、実装時に実装基板との平行度を保って接続不良の防止を図り、且つ半導体回路の破壊をも抑制した半導体チップを提供すること。

【解決手段】例えば、所定の間隙を持って対向させた各メモリバンク22A〜22D間により形成された十字状の接続バンプ配置領域23が設けられている。そして、十字状の接続バンプ配置領域23における領域23Aに、信号入出力用接続バンプ21A(第1の電極)が群をなして配設させている。一方で、当該信号入出力用接続バンプ21Aが群をなす領域23Aに直交する領域23B内に電力・接地用接続バンプ21Bの群を配設させることで、記憶装置チップ20を配線チップ10に実装した際、当該記憶装置チップ20が傾くのを当該電力・接地用接続バンプ21Bが支持し(半田を介して支持し)、最小限のバンプ数で平行度が保たれる。このように、例えば記憶装置チップ20を構成する。

(もっと読む)

電子装置及び電極接続方法

【課題】実装基板上に配置された、互いに厚みが異なる第1及び第2の半導体装置と、第1及び第2の半導体装置の頂部表面にそれぞれ形成された第1の端子電極及び第2の端子電極を相互に接続する導体パターンを有する配線用基板と、を有する電子装置において、製造プロセスを煩雑化することなく、高周波特性のばらつきを抑制できる電子装置を提供する。

【解決手段】電子装置10では、導体パターン21上に形成されたバンプ電極25の段数と、導体パターン22上に形成されたバンプ電極25の段数とが異なる。導体パターン21上に形成されたバンプ電極25の頂部と導体パターン22上に形成されたバンプ電極25の頂部とが同じ高さにある。

(もっと読む)

BGAメッシュ・キャップを有するパッケージ・オン・パッケージ・セキュア・モジュール

パッケージ・オン・パッケージ(POP)セキュア・モジュールは、BGAメッシュ・キャップと、第1のBGAパッケージと、第2のBGAパッケージとを備えている。第1のBGAパッケージは、第1の集積回路(例えば不正行為検出論理を備えたマイクロコントローラ)を備えている。第2のBGAパッケージは、第2の集積回路(例えばメモリ)を備えている。第2のBGAパッケージは、第1のBGAパッケージにピギー・バックで取り付けられており、また、BGAメッシュ・キャップは、第2のBGAパッケージにピギー・バックで取り付けられている。BGAメッシュ・キャップのプリント回路板基板部材は、埋設反不正行為メッシュを備えている。このメッシュは、モジュール内で、保護された方法で第1の集積回路に接続されている。モジュールが使用されると、下方に位置しているプリント回路板に埋め込まれたメッシュがBGAキャップ・メッシュに結合され、したがってこれらの反不正行為メッシュの両方が不正行為検出論理によって制御される。  (もっと読む)

(もっと読む)

電子回路実装構造体

【課題】複数個の半導体素子を高密度に実装可能な電子回路実装構造体を提供する。

【解決手段】半導体素子11の主面の周縁部を構成する4つの辺部のうち、半導体素子11の長手方向に直交する方向おいて対向する2つの辺部(所定の辺部)には、バンプ12を3列構成で、千鳥状に配列し、半導体素子11の長手方向において対向する2つの辺部(他の辺部)には、バンプ12を2列構成で、かつ千鳥状に配列して、バンプ12の列数が少ない辺部からの樹脂接着層16の樹脂のはみ出し量が、バンプ12の列数が多い辺部からのはみ出し量よりも大きくなるようにするとともに、各半導体素子11a〜11fを、樹脂接着層16の樹脂のはみ出し量が小さい所定の辺部同士が隣接する配置で実装した。

(もっと読む)

部品実装装置および部品実装方法

【課題】スタック実装における実装タクトを短縮する部品実装装置および部品実装方法を提供する。

【解決手段】基板1に第1の部品3と第2の部品5をスタック実装するため、まず第1収納部4からピックアップした第1の部品3を転写部7に移送し(矢印a)、第1の部品3に溶剤を転写させた後に第2の収納部6に移送し(矢印b)、トレイ6aに収納された状態の第2の部品5に実装する。第2の部品5に複数の第1の部品3を実装する必要があるときは、全ての第1の部品3の実装が完了した段階で既に実装された第1の部品3とともにピックアップした第2の部品5を基板保持部に移送し(矢印c)、基板1に実装する。

(もっと読む)

半導体部品の実装構造及び実装方法

【課題】半導体部品を回路基板上に容易に実装することができ、且つ回路基板からの半導体部品の取り外しも容易な半導体部品の実装構造及び実装方法を提供する。

【解決手段】BGA型半導体部品1の底面に複数のはんだバンプ12を突設させ、回路基板3に、はんだバンプ12を挿入可能な開口径を有するとともに、はんだバンプ12と同じ間隔で形成され、当該回路基板3の厚さ方向に貫通する複数のスルーホール31を備え、はんだバンプ12をスルーホール31に挿入させ、次いで、回路基板3の底面側から加熱することによりはんだバンプ12を溶解させて、BGA型半導体部品1を回路基板3に溶着する。

(もっと読む)

モジュール型センサアセンブリ及びその製作方法

【課題】モジュール型センサアセンブリ及びその製作方法を提供する。

【解決手段】モジュール型センサアセンブリ(10)並びにモジュール型センサアセンブリ(10)の製作方法(70)を提供する。モジュール型センサアセンブリ(10)は、電子素子アレイ(14)とスタック式構成で結合させたセンサアレイ(12)を含む。センサアレイ(12)は、その各々が複数のセンササブアレイ(18)を備えた複数のセンサモジュール(22)を備える。電子素子アレイ(14)は、その各々が複数の集積回路チップ(20)を備えた複数の集積回路モジュール(24)を備える。センサモジュール(22)は、フリップチップテクノロジーを介して電子素子モジュール(24)と結合させることがある。

(もっと読む)

半導体実装基板と、これに用いる製造方法

【課題】半導体実装基板において、落下時などにシリコン基板2aと樹脂膜2bとの界面2e部分で剥離が発生。

【解決手段】電子部品3を半導体素子2の角部6近傍に装着することによって、基板12と半導体素子2との間に充填した樹脂5を半導体素子2と電子部品3との間の隙間14へ這い上がらせ、界面2eを樹脂5で覆うようにするものである。これにより、界面2eが樹脂5で覆われるので、落下などに強くなり、剥離などが発生し難くできる。

(もっと読む)

電子部品の装着状況の検査方法

【課題】基板における所定の位置に各々装着されているべき複数の電子部品が実際にそれらの位置に各々装着されているか否かを、正確かつ短時間に検査することである。

【解決手段】複数のチップ2が装着されているべき基板1の画像情報を取得し、所定のしきい値TH1によって画像情報を2値化して2値化データを取得し、2値化データに基づいてチップ2に相当すると判断される候補領域を取得し、所定のしきい値TH1を変更して新たなしきい値TH2を設定する。そして、新たなしきい値TH2を使用して新たな2値化データを取得し、新たな候補領域を取得し、新たな候補領域を直前の候補領域に結合し、新たなしきい値TH3を設定するという各工程からなるループを行う。このループを、複数のチップ2のすべてについて所定の位置に各々装着されているか否かを検出するまで繰り返す。

(もっと読む)

電子部品の接続方法

【課題】高さの異なる複数の電子部品を一度に基材に接続できる電子部品の接続方法を提供する。

【解決手段】第1電極31aが形成された第1面30aと第1面の反対側に平行に設けられた第2面30bとを有し第1電極表面から第2面までの距離がaである第1部品30と、第2電極41aが形成された第3面40aと第3面の反対側に平行に設けられた第4面40bとを有し第2電極表面から第4面までの距離がb(a>b)である第2部品40とを、第1電極に接続する第1ランド11aと第2電極に接続する第2ランド12aとが形成された第5面を有する基材10に接続する際、一側に第2面に当接する第6面81と第4面に当接する第7面82とを有し他側に第6面及び第7面に平行な第8面80bを有し第6面と第8面との距離がc、第7面と第8面との距離がd(c<d)であり、(d−c)が(a−b)と略等しい押圧手段80を用いる。

(もっと読む)

21 - 40 / 56

[ Back to top ]