Fターム[5F044RR01]の内容

ボンディング (23,044) | ワイヤレスボンディング関連事項 (2,154) | 複数チップのボンディング (221)

Fターム[5F044RR01]の下位に属するFターム

チップ同士ボンディング (81)

チップを積層してボンディング (82)

同一のリードに複数のチップをボンディング (2)

Fターム[5F044RR01]に分類される特許

41 - 56 / 56

積層実装構造体

【課題】基板の平面方向の投影面積を減少させるように小型化しつつ、さらに、接続抵抗を小さくし、製造工程を少なくしたことで歩留まり向上及びコストの低減及び製造時間の短縮を実現した積層実装構造体を提供すること。

【解決手段】少なくとも一方の主面上に接合部が形成された複数の基盤101a、101bと、対向する基板101a、101b上に形成された電極107a、107bとの間隙に配置されている弾性導電ボール110とを有し、中間基板103には貫通孔120が設けられ、接合部105a等によって基板同士が接合されることによって、弾性導電ボール110が貫通孔120において変形、埋没し、基板同士が電気的に接続される。

(もっと読む)

半導体装置の製造装置及び半導体装置の作製方法

【課題】低コストの半導体装置の作製方法及び低コストで半導体装置を作製可能な製造装置を提供する。

【解決手段】列置された持着部104を有する治具103と、列置された持着部104の間隔を制御する制御手段100と、複数の半導体集積回路102が設けられる支持手段101と、複数の素子112を有する基板111が設けられる支持手段114とを有し、列置された持着部104を有する治具101により半導体集積回路102を素子112に実装して半導体装置を作製する半導体装置の製造装置である。一回の工程において、複数の半導体集積回路102をピックアップし、複数の素子112に複数の半導体集積回路102を貼りあわせ、複数の半導体装置を作製することができる。このため、タクトタイムを短くし、量産性を向上させて、低コストの半導体装置の作製方法を提供することができる。

(もっと読む)

フェイスダウン型半導体装置及びその製造方法

【課題】半導体素子の交換が容易に行えるフェイスダウン型半導体装置及びその製造方法を提供する。

【解決手段】基板電極21が設けられた配線基板2と、基板電極21上に搭載された半導体素子1と、半導体素子1と配線基板2との間を充填するアンダーフィル樹脂4と、配線基板2上にアンダーフィル樹脂4に埋め込まれて配置されたレベル表示パッド5と、を有するフェイスダウン型半導体装置6を製造する。レベル表示パッド5は、2層からなり、配線基板2の基板電極21と同時に形成された金属層5aの上にめっきによって形成された第1層である金属層5bと、第1層である金属層5bの上に形成され有機溶剤によって除去される材質からなる第2層5cからなる。

(もっと読む)

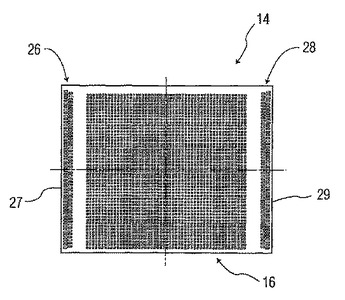

半導体モジュール

【課題】数種類の半導体集積回路チップをモジュール基板に搭載して組み立てる工程数を少なくすることによって歩留まりや信頼性の向上に寄与する。

【解決手段】モジュール基板(10)には、高さ寸法がほぼ等しい半導体集積回路チップ、例えば同種の半導体集積回路チップのグループ毎にそれら半導体集積回路チップを一列に並べて実装可能なように実装パッドをグループ化して配列する。そして、前記グループ化された実装パッド毎に異方導電性フィルム(66A,66B)を貼り付け、貼り付けられた異方導電性フィルムを介して実装パターンと半導体集積回路チップのバンプ電極とを導電接続する。これにより、グループ毎に複数個の半導体集積回路チップを一括して異方導電性フィルムに圧着加熱することができる。

(もっと読む)

半導体装置の製造方法

【課題】テープ基板に半導体チップを両面実装する半導体装置の信頼性の向上を図る。

【解決手段】テープ基板5上に第1の半導体チップ2を搭載し、さらに第1の半導体チップ2より大きな第2の半導体チップ3を搭載し、その後、テープ基板5と第1の半導体チップ2の間にアンダーフィル材4を充填し、さらにテープ基板5と第2の半導体チップ3の間にアンダーフィル材4を充填する。これにより、小さいチップに先にアンダーフィル材4を充填するため、テープ基板5の反りが少ない状態で大きいチップにアンダーフィル材4を充填することができる。その結果、大小両方のチップに対してアンダーフィル材4を確実に充填することができ、COF1(半導体装置)の信頼性の向上を図ることができる。

(もっと読む)

マルチチップ実装法及びそれに用いる硬化性フィルム状接着剤

【課題】 多種類のチップサイズに対応可能であり、接続時の熱の影響が少なく残余接着剤の除去処理が容易なマルチチップ実装法とそれに用いる硬化性フィルム状接着剤を提供する。

【解決手段】下記工程よりなるマルチチップ実装法

(1)基板の同一方向に接続すべき複数個のチップ群の中の最大サイズのテ−プ幅を有する硬化性フィルム状接着剤を複数列分、複数準備する工程、

(2)基板の同一方向に接続すべき複数個のチップ群の中の最大サイズのテ−プ幅を、離して複数列、前記フィルム状接着剤を基板のチップ群搭載列に活性温度以下で仮接続して形成する工程、

(3)接続すべきチップの電極と前記(2)の接着剤付き基板の電極を位置合わせする工程、

(4)電極の位置合わせを終了したチップの電極と基板の電極を、接続すべき電極間で、活性温度以上で加熱加圧し、同一基板に複数列、複数個のチップの電気的接続を得る工程。

(もっと読む)

ICチップ実装方法

【課題】本発明は、ベース上に複数のICチップを実装するICチップ実装方法に関し、生産性向上を図る。

【解決手段】ベースへの搭載面とは反対側の面がテープでマウントされダイシングによりそのテープを残してICチップごとに分離されたウェハを用意して、そのウェハを、ベースへの搭載面がベースに対面する向きに、ベースに対向させ、ベースをウェハに沿う所定の一次元方向に送りながら、かつウェハをベースに沿って二次元的に移動させながら、ウェハ上のICチップを順次にベース上に押し当ててベース上に仮固定させ、ベース上に仮固定された複数のICチップを一括して加熱及び加圧することによりそれら複数のICチップをベース上に固定させる。

(もっと読む)

ICチップ実装方法

【課題】本発明は、ベース上に複数のICチップを実装するICチップ実装方法に関し、生産性向上を図る。

【解決手段】ベース13への搭載面とは反対側の面がテープ30でマウントされダイシングによりテープ30を残してICチップ11ごとに分離されたウェハ10を用意し、ウェハ10上のICチップ11を順次に第1のローラ51に押し当てて吸着させ、第1のローラ51上に吸着されたICチップ11を順次に第2のローラ52に受け渡し、第2のローラ52上のICチップ11を、走行するベース13上に順次に搭載する。

(もっと読む)

半導体装置における実装構造の接続信頼性の予測方法およびその半導体装置

【課題】 初期検討段階においても、BGA/CSPをプリント配線基板へ実装した場合のはんだ接合部の熱ひずみを短時間で予測して、迅速な仕様決定に対応できるようにする。

【解決手段】 第1の基板の一方の面に一つ以上の半導体素子が搭載されるとともに、第1の基板の他方の面にはんだバンプが設けられた半導体装置において、前記はんだバンプを用いて第2の基板に接続した前記半導体装置の実装構造物を対象に接続信頼性を予測するための方法である。半導体装置の実装構造の寸法103と物性値102とに基づいてはんだ接合部のダメージを見積もるはんだダメージ計算式105を用いて、はんだ接合部の疲労寿命を予測する。

(もっと読む)

マルチチップ実装法

【課題】 サイズの異なるチップを基板の電極面に配置し、一度に実装することができる効率のよいMCM(マルチチップモジュール)の製造が可能なマルチチップ実装法を提供する。

【解決手段】 次の工程よりなるマルチチップ実装法、(1)硬化性材料からなるフィルム状接着剤層を用い、チップの電極形成面の大きさと略同一面積のフィルム状接着剤層を、前記チップの電極面に形成してなる複数の接着剤付チップを得る工程、(2)接続すべき複数の接着剤付チップの電極と基板の電極を対向させて、それぞれ位置合わせする工程、(3)電極の位置合わせを終了した複数のチップの電極と基板の電極を、接続すべき電極間で同時に加熱圧着し、同一基板に複数のチップの電気的接続を得る工程。

(もっと読む)

熱圧着装置

【課題】 熱圧着の温度や加圧力のばらつきをなくして、高精度に圧着でき、かつディスプレイサイズやそれに搭載される半導体装置のサイズや位置等が異なる場合にも、自動的に調整できる熱圧着装置を提供する。

【解決手段】 ディスプレイパネル1にドライバ回路2が複数仮圧着された状態で、熱圧着するために、熱圧着ブロック23の圧着ヘッド23bと受け台24とを備えた熱圧着ユニット20はドライバ回路2毎に分割されており、ユニット位置調整手段30を構成し、熱圧着ユニット20を固定する摩擦板31をエアシリンダ33に設けたプッシャ38により押し上げて、支持テーブル10から離間させて、ガイドレール11に沿って移動させることによって、個々の熱圧着ユニットの位置調整を行う。

(もっと読む)

電子部品実装装置

【課題】本発明は、可撓性の基材上に電子部品を実装する電子部品実装装置に関し、可撓性基材上の複数パターンのそれぞれに電子部品を同時多数実装させることで効率向上を図り、しわ発生を防止して歩留りの向上を図ることを目的とする。

【解決手段】実装ステージ13が可撓性の基材シート15に形成された複数のアンテナ23上に搭載されるそれぞれのICチップ16の位置に対応させた複数の突部22を備え、当該ICチップ16が搭載された基材シート15が搬送されてきたときに、当該突部22に形成される所定数の通気孔22Aより当該基材シート15を部分的に吸引して固定し、実装アタッチメント群12が当該突部22上で吸引固定されている基材シート15上のアンテナ23およびICチップ16に対して加熱、押圧することで当該ICチップ16を当該アンテナ23上に電気的接続させる構成とする。

(もっと読む)

フリップチップ実装法を利用した光変調器モジュールパッケージ

【課題】フリップチップ実装法を利用して、光変調器素子の最適の密封実装、容易な電気信号伝達および光学特性維持のための光変調器モジュールパッケージを提供する。

【解決手段】外部から入射する入射光を変調するマイクロミラー、前記マイクロミラーの少なくとも一方の側から離間され、外部から入力される電気信号を前記マイクロミラーに伝達する上部金属パッド、および前記マイクロミラーを取り囲むように前記マイクロミラーと前記上部金属パッド間に形成される上部密封パッドを下面に含む光変調器素子と、前記光変調器素子の上部金属パッドに対応する位置に形成される下部金属パッド、および前記光変調器素子の上部密封パッドに対応する位置に形成される下部密封パッドを上面に含む光透過性カバーとを含む。

(もっと読む)

超音波医療用トランスデューサアレイ

超音波トランスデューサ(40、70、100)は、個々のダイが結合された集積回路(42、72、102)と、この個々のダイが結合された集積回路にフリップチップバンプのアレイ(46、76、106)を介して結合された音響素子アレイ(44、74、104)とを有する。個々のダイが結合された集積回路は、第1の集積回路ダイ(48、78、108)と、前記第1の集積回路ダイに整列された少なくとも1つの更なる集積回路ダイ(50、80、(110、112))とを含んでいる。また、第1の集積回路ダイと、少なくとも1つの更なる集積回路ダイと、音響素子アレイとは一緒になって大口径のトランスデューサアレイを形成している。  (もっと読む)

(もっと読む)

複数の電子アセンブリの製造方法

【解決手段】複数の電子デバイスを製造する方法が提供される。デバイスウエハ上に形成された複数の集積回路上の複数の第1の導電性端子のそれぞれが、キャリアウエハ上の複数の第2の導電性端子のそれぞれと連結して、コンビネーションウエハアセンブリを形成する。コンビネーションウエハアセンブリは、分離した電子アセンブリを形成する複数の集積回路の間において、複数の集積回路の間でシンギュレートされる。電子アセンブリはそれぞれ、デバイスウエハの分離した部分からの個別のダイ、およびキャリアウエハの分離した部分からのキャリアウエハを有する。複数の電子アセンブリを製造するプロセスは、ウエハレベルで、すなわち、シンギュレーションの前に、複数のダイがキャリアウエハに連結され、単純化され、コストが低減される。また、コンビネーションウエハアセンブリは、アンダーフィル材料の導入、ウエハレベルでの硬化、および分離した支持ウエハを必要とせずにウエハレベルでのデバイスウエハの薄層化を可能とする。デバイスウエハとキャリアウエハとの間の位置合わせは、デバイスウエハとキャリアウエハのそれぞれの中の第1の導電体と第2の導電体を通る電流を伝導することにより試験される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の高速伝送、多層化対応を図り、半導体チップ設計の制約を減らす。

【解決手段】半導体装置は、少なくとも2つの積層された半導体チップ1,2と、半導体チップ1,2同士を電気的に接続する接続構造とを有している。接続構造は、第1の半導体チップ1に設けられた第1の電極11と、第2の半導体チップ2に設けられた第2の電極21と、第1、第2の半導体チップ1,2の間に挟まれた接合ボード5とを有している。接合ボード5は、第1の電極11と対向する第1の接続電極52と、第2の電極2と対向する第2の接続電極53と、接合ボード5を貫通するスルーホール54と、スルーホール54と第1、第2の接続電極52、53とを電気的に接続する配線55,56とを備えている。

(もっと読む)

41 - 56 / 56

[ Back to top ]