Fターム[5F044RR03]の内容

ボンディング (23,044) | ワイヤレスボンディング関連事項 (2,154) | 複数チップのボンディング (221) | チップを積層してボンディング (82)

Fターム[5F044RR03]に分類される特許

1 - 20 / 82

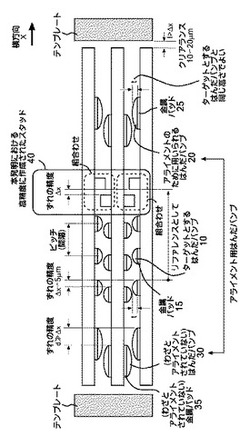

はんだバンプのセルフアライメントに利用するスタッドの作成

【課題】 3次元実装のプロセスに親和性のある、高精度のアライメントを提供すること。

【解決手段】 複数のシリコンチップ間においてはんだバンプが溶融した場合に、複数のシリコンチップ同士の横方向の相対的な動きを規制する複数のスタッド(40)の組合わせであって、複数のシリコンチップ間に配置される複数のはんだバンプ(10)のピッチに従い、これらの横方向の位置をリファレンスにして横方向位置が決定されていて、複数のシリコンチップが横方向に相対的に移動した場合に相対的に動きが規制されて、複数のシリコンチップのそれぞれに設定された複数のはんだバンプ同士の横方向位置が(高さ方向において)整列するように、一方のシリコンチップおよび他方のシリコンチップにおいて複数のスタッド(40)が設けられる。

(もっと読む)

半導体装置の製造方法、及び半導体製造装置

【課題】吸着ツールに対する半導体チップの位置ずれを補正して被搭載体に搭載可能となり、被搭載体に対する半導体チップの位置精度の向上が図れる半導体装置の製造方法、および、製造装置を提供する。

【解決手段】半導体チップ2を吸着ツール12で吸着する工程と、吸着ツールに吸着された半導体チップの裏面から赤外線カメラ13で赤外線画像を撮影することにより半導体チップの表面にあるアライメントマークの位置を検出する工程と、赤外線カメラによって検出されたアライメントマークの位置に基づいて吸着ツールに対する半導体チップの位置ズレを補正して半導体チップを被搭載体3に搭載する工程と、を含む。

(もっと読む)

半導体素子の実装方法

【課題】薄型化,狭ピッチ端子化された半導体素子であっても、生産性を維持しながら、はんだ接合の際の反りを抑制することを目的とする。

【解決手段】半導体素子を搭載する毎に加圧状態で加熱して仮接合を行い、全ての半導体素子を仮接合した後、一括して加圧状態で加熱して本接合を行うことにより、薄型化,狭ピッチ端子化された半導体素子であっても、生産性を維持しながら、はんだ接合の際の反りを抑制して積層することができる。

(もっと読む)

三次元実装装置

【課題】半導体デバイスの製造のスループットをさらに向上できるとともに、製造される半導体デバイスの品質の低下を防止できる三次元実装装置を提供する。

【解決手段】三次元実装装置11において、搬送トレイ16は配置面16aaをそれぞれ含む8つの内側トレイ16aを有し且つ各配置面16aaに配置された8つの積層チップ21を搬送し、チャンバ27は全ての内側トレイ16aを収容し、複数の下部ステージ28の各々はチャンバ27内において複数の内側トレイ16aの各々を載置し、複数のチャック29の各々は、チャンバ27内において、配置面16aaに配置された積層チップ21の各々と一対一で対応して配設され、各下部ステージ28及び各複数のチャック29が各下部ステージ28及び各複数のチャック29の間を詰めるように移動する。

(もっと読む)

積層フィルム及びその使用

【課題】3次元実装された半導体素子間の空間の充填を容易かつ確実に行うことができる積層フィルムを提供する。

【解決手段】積層フィルムは、接続用部材41bを介して電気的に接続された半導体素子間の空間を充填するための積層フィルムであって、基材1上に粘着剤層2が積層されたダイシングシートと、粘着剤層上に積層された硬化性フィルム3とを備え、硬化性フィルムの50〜200℃における最低溶融粘度は、1×102Pa・s以上1×104Pa・s以下である。

(もっと読む)

半導体装置の製造方法

【課題】チップ積層体の外部接続用電極として機能する第1のバンプ電極間がショートしないように、第1のバンプ電極に精度よくはんだを形成可能な半導体装置の製造方法を提供する。

【解決手段】ボンディングツール34によりはんだ搭載用基板50の他面を保持すると共に、第2のバンプ電極55に形成されたはんだ57を加熱により溶融させ、はんだ搭載用基板の第2のバンプ電極をチップ積層体40の第1のバンプ電極17と対向配置させる工程と、第2のバンプ電極に形成され、かつ溶融したはんだを、チップ積層体の第1のバンプ電極に接触させた後、チップ積層体からはんだ搭載用基板を離間させることで、第1のバンプ電極にはんだを転写させる工程と、を含む。

(もっと読む)

半導体封止用接着剤、半導体装置の製造方法及び半導体装置

【課題】半導体チップ及び基板間や2つの半導体チップ間の接続性を良好にでき、且つ、保存安定性を確保できる半導体封止用接着剤を提供すること。

【解決手段】半導体チップ10及び配線回路基板20のそれぞれの接続部15、32が互いに電気的に接続された半導体装置100、又は、複数の半導体チップのそれぞれの接続部が互いに電気的に接続された半導体装置において、接続部を封止する半導体封止用接着剤40であって、(a)第一級又は第二級窒素原子含有化合物と、(b)エステルと、(c)エポキシ樹脂と、を含有する、半導体封止用接着剤。

(もっと読む)

パッケージ支持面にクリップを利用する高電圧III族窒化物整流器パッケージ

【課題】パッケージ支持面にクリップを利用する高電圧III族窒化物整流器パッケージの典型的な実施形態を提供する。

【解決手段】パッケージ支持面260に取り付け、III族窒化物トランジスタ230のソースにスタックされたダイオード220のアノードを有するIII族窒化物トランジスタ230と、III族窒化物トランジスタ230のゲートおよびダイオード220のアノードに結合した第1の導電性クリップ212bと、III族窒化物トランジスタ230のドレインに結合した第2の導電性クリップ212aとを含む。導電性クリップ212a、212bはパッケージ支持面260に結合され、表面実装性の平担部を露出する。

(もっと読む)

フェイスダウン型実装構造

【課題】半導体チップを基板にフェイスダウン実装してなるフェイスダウン型実装構造において、半導体チップと基板電極との接続状態を適切に視認できるようにする。

【解決手段】一方の主面11に主面電極14を有する半導体チップ10と、一面21上に基板電極22を有する基板20とを備え、一方の主面11を基板20の一面21に対向させた状態で、半導体チップ10が基板20の一面21上に搭載されてなるフェイスダウン実装型の実装構造において、半導体チップ10の一方の主面11の外郭に位置する側面13には、主面電極14と導通し一方の主面11から側面13に亘って延設された導体部15が設けられており、半導体チップ10の側面13にて、導体部15と基板電極22とが導電性接合材30を介して接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】2枚のシリコン基板を重ね合わせて接着し、2枚のシリコン基板のそれぞれに形成されたバンプ電極同士を電気的に接続する半導体装置において、樹脂によるバンプ保護性能の低下を防ぎ、また、バンプ電極間の接続性の低下を防ぐ。

【解決手段】第1シリコン基板100上および第2シリコン基板101上のそれぞれに、上面の高さが揃ったバンプ電極230、ダミーバンプ240および耐熱性樹脂膜300を形成した後、第1シリコン基板100と第2シリコン基板101とをそれぞれの基板に形成されたバンプ電極同士が電気的に接続されるように接着させる。その際、ダミーバンプ240を対向するシリコン基板上の耐熱性樹脂膜300に接着するように配置することで、バンプ電極同士の良好な電気的接続と、耐熱性が高くボイドがない樹脂膜によるバンプ保護性能を併せ持った半導体装置を実現できる。

(もっと読む)

半導体デバイスウエーハの接合方法

【課題】異方性導電材料を用いた半導体デバイスウエーハ同士の接合方法を提供する。

【解決手段】複数の突起電極17を有する半導体デバイスが複数形成された第1半導体デバイスウエーハ11の該突起電極側を絶縁体10で被覆する絶縁体被覆ステップと、該絶縁体10が被覆された第1半導体デバイスウエーハ11の該突起電極側を平坦化するとともに該突起電極17の端面を露出させる突起電極端面露出ステップと、該突起電極17に対応した電極を有する第2半導体デバイスウエーハ24の該電極と第1半導体デバイスウエーハ11の該突起電極17とを異方性導電体28で接合し、該電極と該突起電極17とを接続する接合ステップと、を具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体素子間の接続不良の発生を低減可能な半導体装置を提供する。

【解決手段】 下部構造体110cと第1半導体素子110aとを連結する第1連結構造体140aは、複数の連結部141および複数の補助部142を有する。また、第1半導体素子110aと第2半導体素子110bとを連結する第2連結構造体140bは、複数の連結部141を有する。第1連結構造体140aの連結部141および補助部142の数に比べて、第2連結構造体140bの連結部141の数は小さい。これにより、第1半導体素子110aを下部構造体110cに連結するときのボンディング力に比べて、小さいボンディング力で第2半導体素子110bを第1半導体素子110aに連結することができる。したがって、第1連結構造体140aが変形または変性することなく、半導体素子間の接続不良の発生を低減することができる。

(もっと読む)

半導体装置の製造方法

【課題】半導体チップの組立工程におけるハンドリング性を向上し、しかも、半導体チップの損傷を回避する半導体装置の製造方法を提供すること。

【解決手段】ダイシングライン16によって区画された複数の半導体チップ4を含む半導体ウエハ2を準備する第1の工程と、半導体ウエハ2に支持板13を付着する第2の工程と、半導体ウエハ2および支持板13をダイシングライン16に沿って切断し、半導体チップ4および分割された支持板13からなる積層体3を形成する第3の工程と、積層体3を配線基板18に搭載し、積層体3の半導体チップ4および配線基板18を電気的に接続する第4の工程とを有する半導体装置1の製造方法。

(もっと読む)

オーバーレイミスアライメントを減少させた直接ボンディング法

【課題】第1のウェーハを第2のウェーハに直接ボンディングする新規な方法を提供する。

【解決手段】本発明の方法は、固有湾曲を有する第1のウェーハ(100)を固有湾曲を有する第2のウェーハ(200)に直接ボンディングする方法であり、2枚のウェーハのうちの少なくとも一方(100)が少なくとも一組のマイクロコンポーネント(110)を備える。本方法は、2枚のウェーハ間でのボンディング波の伝搬を開始させるように、2枚のウェーハ(100、200)を互いに接触させる少なくとも1つのステップを含む。接触させるステップ中に、回転放物面の形態の所定のボンディング湾曲(KB)が、ウェーハ(100)のボンディング前の固有湾曲に依存して2枚のウェーハのうちの一方に与えられ、他方のウェーハが所定のボンディング湾曲(KB)と一致するように自由である。

(もっと読む)

樹脂組成物、接着フィルム、半導体装置、多層回路基板および電子部品

【課題】第1の被着体と第2の被着体とを接合する際、容易に、第1の被着体と第2の被着体との位置合わせを行うことができる樹脂組成物を提供すること、および、このような樹脂組成物を用いた接着フィルム、半導体装置、多層回路基板および電子部品を提供すること。

【解決手段】本発明の樹脂組成物は、第1の被着体と第2の被着体とを接合する際に用いられ、前記第1の被着体上に設けられる樹脂組成物層1を構成するものであり、前記樹脂組成物層1を平均厚さt[μm]で設け、前記樹脂組成物層1の波長800nmの光における吸収係数をα[1/μm]としたとき、下記(1)式および(2)式を満たすよう構成されている。

α×t≦−log10(0.05) ・・・(1)

1≦t≦200 ・・・(2)

(もっと読む)

接着剤注入装置および接着剤注入方法

【課題】注入された接着剤に、基板内部に残留するガスによるボイドが形成されることを防止する。

【解決手段】基板Wの周側面には、接着剤注入口101aと排気口101bを有するシール材101が形成されている。シール材101の接着剤注入口101aを接着剤102中に浸漬し、排気口101bを排気用ノズル110で覆う。真空ポンプP1に接続されたポンプ側継手122が嵌合されたノズル用継手121を、排気用ノズル110に接続する。真空ポンプP1により、排気口101bを介して基板W内部の空隙に残留するガスを吸気し、接着剤102を注入する。

(もっと読む)

半導体装置及びその製造方法

【課題】積層する基板の電極端子同士の間での接合不良を防止できる3次元集積化技術を提供する。

【解決手段】基板1上にトランジスタ6と多層配線2、絶縁膜3を形成する。絶縁膜3に配線が露出するように開口部4を形成する。開口部内を含む絶縁膜上に、銅などからなる複数の導電体微粒子5を含む有機溶剤を回転塗布する。第1の熱処理により溶剤と有機成分を除去した後、CMP法で外側部分の導電体微粒子を除去する。開口部内に導電体微粒子から構成された電極端子9が形成される。第2の基板51の貫通電極52を開口部に合わせ、加圧して押し合わせる。第1の熱処理より高温の第2の熱処理を行い、導電体微粒子を部分的に溶融させ、貫通電極と接合する。

(もっと読む)

半導体装置の製造方法

【課題】半導体素子の破損を抑制すること。

【解決手段】上面に凹部18を備える基板10の前記凹部18内に第1半導体素子30を実装する工程と、前記第1半導体素子30の上面上に弾性体40を配置する工程と、第2半導体素子50の下面が前記弾性体40の上面に接するように前記第2半導体素子50の上面に荷重をかけて前記第2半導体素子50を前記基板10に接合する工程と、を含む半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】複数の半導体素子を積層させる半導体装置を低コストで製造する手段を提供する。

【解決手段】半導体装置31は、回路基板1上に第1の半導体素子10が実装されており、第1の半導体素子10の第1の電極パッド14上のハンダバンプ17に第2の半導体素子20の接続端子26が接合されている。第1の半導体素子10の第2、第3の電極パッド15,16はワイヤ18で回路基板1に電気的に接続されている。第1の半導体素子10と第2の半導体素子20の間の距離H0は、背高の接続端子26によって、ワイヤ18のループ高さH1以上になっている。

(もっと読む)

半導体接合用接着剤、半導体接合用接着フィルム、半導体チップの実装方法及び半導体装置

【課題】透明性が高く、半導体チップボンディング時のパターン又は位置表示の認識を容易なものとする半導体接合用接着剤を提供する。

【解決手段】エポキシ樹脂、無機フィラー及び硬化剤を含有する半導体接合用接着剤であって、前記無機フィラーは、半導体接合用接着剤中の含有量が30〜70重量%であり、かつ、平均粒子径が0.1μm未満のフィラーAと、平均粒子径が0.1μm以上1μm未満のフィラーBとを含有し、前記フィラーAは、前記フィラーBに対する重量比が1/9〜6/4である半導体接合用接着剤である。

(もっと読む)

1 - 20 / 82

[ Back to top ]