Fターム[5F045AB17]の内容

気相成長(金属層を除く) (114,827) | 成長層の組成 (12,584) | 3−5族 (4,971) | 3元混晶 (1,276)

Fターム[5F045AB17]に分類される特許

81 - 100 / 1,276

窒化物半導体装置

【課題】リーク電流を低減でき、かつ、良好な電流コラプス特性が得られる窒化物半導体装置を提供する。

【解決手段】Si基板1上に順に積層されたチャネルGaN層5およびそのチャネルGaN層5とヘテロ界面を形成するバリアAlGaN層6を含む窒化物半導体層を備える。上記バリアAlGaN層6は、炭素濃度を5×1017/cm3以上とする。また、チャネルGaN層5は、炭素濃度を6×1016/cm3未満とし、かつ、膜厚を500nm以上とする。

(もっと読む)

III族窒化物半導体膜およびその製造方法、ならびにIII族窒化物半導体デバイスおよびその製造方法

【課題】均質なn型導電性のIII族窒化物半導体層を含むIII族窒化物半導体膜およびかかるIII族窒化物半導体膜を含むIII族窒化物半導体デバイスを提供する。

【解決手段】本III族窒化物半導体膜20は、主面20m,21m,22mが(0001)面20cに対して0°より大きく180°より小さいオフ角θを有し、n型導電性を実質的に決定するドーパントが酸素であるIII族窒化物半導体層21,22を少なくとも1層含む。また、本III族窒化物半導体デバイスは、上記のIII族窒化物半導体膜20を含む。

(もっと読む)

半導体発光素子の製造方法及び半導体発光素子用ウェーハ

【課題】成長用基板の剥離の際の半導体層の損傷を抑制した半導体発光素子の製造方法及び半導体発光素子用ウェーハを提供する。

【解決手段】実施形態によれば、凹凸が設けられた主面を有する第1基板の主面上に、発光層を含む窒化物半導体層を形成する工程と、窒化物半導体層と第2基板とを接合する工程と、第1基板を介して窒化物半導体層に光を照射して第1基板を窒化物半導体層から分離する工程と、を含む半導体発光素子の製造方法が提供される。窒化物半導体層を形成する工程は、凹凸の凹部の内壁面上に窒化物半導体層の少なくとも一部と同じ材料を含む薄膜を形成しつつ、凹部の内側の空間内に空洞を残すことを含む。分離する工程は、薄膜に光の少なくとも一部を吸収させて、窒化物半導体層のうちで凹部に対向する部分に照射される光の強度を、窒化物半導体層のうちで凹凸の凸部に対向する部分に照射される光の強度よりも低くすることを含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体装置の、ソース・ドレイン間のオン抵抗を低減する。

【解決手段】ソース・ドレイン間を走行する窒化物半導体層と下地となる窒化物半導体層の間に、両窒化物半導体層より電子親和力が大きく、下地となる窒化物半導体よりも格子定数の大きい材料を形成する。その結果、ゲート電圧の印加によりゲート絶縁膜の下方に形成されるチャネルと、ゲート部以外で形成される二次元電子ガスを、深さ方向において近づけることができ、オン抵抗の低減が可能となる。

(もっと読む)

半導体装置の製造方法

【課題】設計された形状およびサイズのゲート電極を形成することが可能な半導体装置の製造方法を提供すること。

【解決手段】本実施形態に係る半導体装置の製造方法は、半導体層12の表面上のうち、互いに離間した位置に、チタン層17a、18a、アルミニウム層17b、18b、ニッケル層17c、18c、金層17d、18dがこの順で積層した積層体17、18を形成し、これらを、アルミニウムの融点より高い温度で加熱して複数の金属体17´、18´を形成するするとともに、これらの複数の金属体17´、18´を半導体層12にオーミック接触させる。この後、複数の金属体17´、18´を薄膜化して複数の合金層13a、14aを形成し、合金層13a、14aを含むドレイン電極13およびソース電極14を形成する。次に、ドレイン電極13とソース電極14との間のレジスト層19に開口部20し、この開口部20内にゲート電極15を形成する。

(もっと読む)

半導体発光素子の製造方法

【課題】本発明は、半導体発光素子の製造方法に関する。

【解決手段】本発明の実施例による半導体発光素子の製造方法は、半導体成長用基板上に第1導電性半導体層、活性層及び第2導電性半導体層を順に成長させて発光部を形成する段階と、上記第2導電性半導体層上に上記発光部と結合されるように支持部を形成する段階と、上記発光部から上記半導体成長用基板を分離する段階と、上記分離された半導体成長用基板の表面に残存する半導体層が除去されるように上記半導体成長用基板にエッチングガスを適用する段階とを含む。

(もっと読む)

III族窒化物半導体発光素子の製造方法

【課題】III 族窒化物半導体発光素子において、光取り出し効率を向上させること。

【解決手段】発光層14上に、MOCVD法によってp−AlGaNからなるpクラッド層15を形成する。圧力30kPa、Mg濃度は1.5×1020/cm3 とする。これにより、III 族元素極性の結晶に窒素極性の領域が多数生じ、pクラッド層15の表面は六角柱状の凹凸形状となる。次に、pクラッド層15上に、MOCVD法によって凹凸形状に沿って膜状にGaNからなるpコンタクト層16を形成する。

(もっと読む)

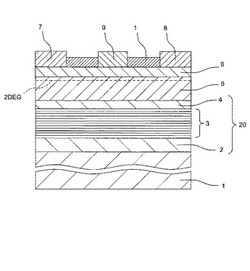

化合物半導体装置及びその製造方法

【課題】絶縁破壊耐性に優れた化合物半導体積層構造を備えて基板の絶縁破壊の十分な抑止を実現し、ピンチオフ状態とする際にもリーク電流が極めて少ない信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上に形成された化合物半導体積層構造2は、その厚みが10μm以下であって、AlNからなる厚い第1のバッファ層を有しており、III族元素(Ga,Al)の総原子数のうち、Al原子の比率が50%以上とされ、換言すれば、V族元素のNとの化学結合(Ga−N,Al−N)の総数のうち、Al−Nが50%以上とされる。

(もっと読む)

窒化物半導体装置の製造方法

【課題】高抵抗バッファ層の結晶品質の劣化を避けることができる窒化物半導体装置の製造方法を得る。

【解決手段】SiC基板1上に、III族原料として有機金属原料を用い、V族原料としてヒドラジン誘導体の有機化合物を用いたMOCVD法により、炭素濃度が1018cm−3以上に制御された窒化物半導体からなるAlN高抵抗バッファ層2を形成する。AlN高抵抗バッファ層2上に、AlN高抵抗バッファ層2よりも低い抵抗値を持つGaN電子走行層3とAl0.2Ga0.8N電子供給層4を形成する。

(もっと読む)

化合物半導体結晶の製造方法

【課題】複雑な作製工程を必要とせずに、均一に高品質な結晶が形成できるようにする。

【解決手段】まず、III−V族化合物半導体の単結晶からなる基板101の主表面におけるテラスの幅を、主表面の(100)面からの傾斜角度により制御する。この制御では、後述する第3工程で形成する第2半導体層103の第2原子間隔と、基板101の主表面における第1原子間隔と、自然数Nとを用いて表されるN×第1原子間隔≒(N−1)×第2原子間隔の関係が成立する条件で、テラスの幅がN×第1原子間隔となる状態に基板101の主表面を傾斜させる。なお、第2原子間隔は、第1原子間隔と同じ方向の、第2半導体層103を構成する原子の間隔である。

(もっと読む)

窒化物半導体素子、窒化物半導体ウェーハ及び窒化物半導体層の製造方法

【課題】任意の基板上に形成でき良好な結晶性を有する窒化物半導体素子、窒化物半導体ウェーハ及び窒化物半導体層の製造方法を提供する。

【解決手段】実施形態によれば、第1層と、機能層と、を備えた窒化物半導体素子が提供される。前記第1層は、非晶質層の上に形成され、窒化アルミニウムを含み、圧縮歪または引張歪を有する。前記機能層は、前記第1層の上に形成され、窒化物半導体を含む。

(もっと読む)

電界効果型トランジスタおよびその製造方法

【課題】ウルツ鉱型結晶構造の半導体を用いた電界効果トランジスタで、電極との接触抵抗を高くすることなく、バンドギャップエネルギーのより大きな半導体から障壁層が構成できるようにする。

【解決手段】ゲート電極104を挟んで各々離間して障壁層103の上に接して形成された2つの電流トンネル層105と、各々の電流トンネル層105の上に形成された2つのキャップ層106とを備える。電流トンネル層105の分極電荷は、障壁層103の分極電荷よりも大きい。

(もっと読む)

半導体装置の製造方法

【課題】InAlN電子供給層上にGaN層を形成する場合でも、InAlN電子供給層の品質の悪化を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、基板10上にGaN電子走行層14を形成する工程と、GaN電子走行層14上にInAlN電子供給層18を形成する工程と、InAlN電子供給層18を形成した後、In含有ガスを供給しつつ、基板10を昇温させる工程と、昇温が終了した後、InAlN電子供給層18上にGaN層20を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

窒化物半導体素子、窒化物半導体ウェーハ及び窒化物半導体層の製造方法

【課題】シリコン基板上に形成される、低転位密度で結晶品質が優れた窒化物半導体素子、窒化物半導体ウェーハ及び窒化物半導体層の製造方法を提供する。

【解決手段】実施形態によれば、下地層と、機能層と、を備えた窒化物半導体層が提供される。下地層は、シリコン基板の上に形成されたAl含有窒化物半導体層の上に形成され、不純物濃度が低く、GaNを含む。機能層は、下地層の上に設けられる。機能層は、下地層の不純物濃度よりも高い不純物濃度を有し第1導電形のGaNを含む第1半導体層を含む。Al含有窒化物半導体層は、多層構造体を含む。多層構造体は、Alを含む窒化物半導体を含む複数の第2層と、複数の第2層の間に設けられ第2層におけるAl組成比よりも低いAl組成比を有する窒化物半導体を含む第1層と、を含む。下地層の厚さは、第1層の厚さよりも厚く、第1半導体層の厚さよりも薄い。

(もっと読む)

半導体装置

【課題】高周波数動作が可能な半導体装置を提供すること。

【解決手段】本発明は、基板10上に設けられたGaN電子走行層14と、GaN電子走行層14上に設けられたAlNスペーサ層16と、AlNスペーサ層16上に設けられたInAlN電子供給層18と、InAlN電子供給層18上に設けられたゲート電極24とゲート電極24を挟むソース電極26およびドレイン電極28と、を備え、AlNスペーサ層16の膜厚が、0.5nm以上1.25nm以下の半導体装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】InAlN電子供給層上にGaN層を形成する場合でも、InAlN電子供給層の品質の悪化を抑制すること。

【解決手段】本発明は、基板10上にGaN電子走行層14を形成する工程と、GaN電子走行層14上にInAlN電子供給層18を形成する工程と、InAlN電子供給層18上に第1のGaN層20を形成する工程と、第1のGaN層20上に、InAlN電子供給層18および第1のGaN層20を形成した際の温度よりも高い温度で、第2のGaN層22を形成する工程と、InAlN電子供給層18上に、ゲート電極26と、ゲート電極26を挟むソース電極28およびドレイン電極30と、を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

窒化物半導体結晶層の製造方法及び窒化物半導体結晶層

【課題】より良質な窒化物半導体結晶層を製造する方法及び窒化物半導体結晶層を提供する。

【解決手段】実施形態によれば、表面にシリコン酸化膜が形成された基体の上に設けられた20μm以下の厚さのシリコン結晶層の上に、1μm以上の厚さの窒化物半導体結晶層を形成する。シリコン結晶層の上に、窒化物半導体結晶層のうちの第1の部分を形成した後、第1の部分よりも高い温度で第2の部分を形成する。シリコン結晶層は、シリコン結晶層の層面に対して平行な面内において、0.5mm以上、10mm以下の特性長さを持つ島状に区分されている。区分されたシリコン結晶層のそれぞれの上に選択的に互いに離間した複数の窒化物半導体結晶層を形成する。シリコン結晶層の少なくとも一部を窒化物半導体結晶層に取り込ませ、シリコン結晶層の厚さを減少させる。

(もっと読む)

III族窒化物結晶基板、エピ層付III族窒化物結晶基板、ならびに半導体デバイスおよびその製造方法

【課題】発光のブルーシフトが抑制された発光デバイスの製造に好適なIII族窒化物結晶基板、エピ層付III族窒化物結晶基板、ならびに半導体デバイスおよびその製造方法を提供する。

【解決手段】本III族窒化物結晶基板1は、結晶基板の表面層の均一歪みが1.9×10-3以下であり、結晶基板の表面層の不均一歪みが130arcsec以下であり、均一歪みと不均一歪みとは、それらの一方が小さくなるほど他方が小さくなる関係を有し、結晶基板の主表面1sの面方位が、結晶基板の(0001)面または(000−1)面1cから<10−10>方向に10°以上80°以下で傾斜している。

(もっと読む)

III族窒化物半導体発光素子の製造方法

【課題】III 族窒化物半導体発光素子の駆動電圧を低減すること。

【解決手段】pクラッド層15は、厚さ0.5〜10nmのp−AlGaN層と、InGaN層とを繰り返し成長させて積層させた超格子構造とする。p−AlGaN層の成長温度は800〜950℃とする。p−AlGaN層上にInGaN層を形成する際、p−AlGaN層の成長温度を保持したまま、TMAの供給を停止してTMIを供給し、Ga源ガスの供給量を増やし、厚さ1〜2分子層のInGaN層を形成する。pクラッド層15の結晶品質を良好に保ちつつ、厚さを薄くできるため、駆動電圧を低減することができる。

(もっと読む)

III族窒化物積層体の製造方法

【課題】Al含有率が高いIII族窒化物半導体上にP型GaN層が形成された積層体において、その表面が極めて平滑であり、電極特性が良好な積層体の製造方法を提供する。

【解決手段】AlXGaYInZN(X、YおよびZが、X+Y+Z=1.0,Y≧0,Z≧0,0.5≦X≦1.0である)層と、不純物原子がドープされたGaN層と有するIII族窒化物積層体を製造する方法であって、P型GaN層16が、層厚みをT[nm]とし、P型GaN層の層厚み方向における成長速度をGR[nm/分]とし、P型GaN層を形成するために用いられるGa原料の流量をFGa[μmol/分]とし、不純物原子原料の流量をFi[μmol/分]としたときに、GRが0.15以上2.0以下、(Fi/FGa)×ln(T)が0.1を超え0.4以下となるように成長させる。

(もっと読む)

81 - 100 / 1,276

[ Back to top ]