Fターム[5F048AC03]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 集積回路要素 (9,617) | MOS+MOS (7,604) | CMOS(Complementary MOS) (4,005)

Fターム[5F048AC03]の下位に属するFターム

TFT・CMOS (819)

Fターム[5F048AC03]に分類される特許

141 - 160 / 3,186

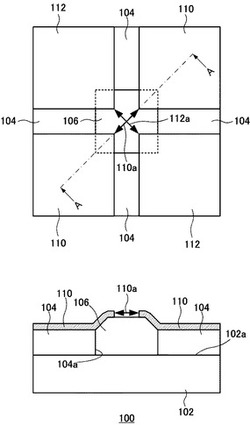

半導体基板、半導体装置および半導体基板の製造方法

【課題】十分な感度を有したp型キャリアのホール素子の製造に適した半導体基板を提供する。

【解決手段】表面の全部または一部がシリコン結晶面であるベース基板と、前記ベース基板の上に位置し、前記シリコン結晶面に達する開口を有し、結晶の成長を阻害する阻害体と、前記開口の底部の前記シリコン結晶面の上に位置する第1結晶層と、前記第1結晶層の上に位置し、互いに離して配置した一対の第1金属層と、前記第1結晶層の上に位置し、互いに離して配置した一対の第2金属層と、を有し、前記一対の第1金属層のそれぞれを結ぶ第1最短線と、前記一対の第2金属層のそれぞれを結ぶ第2最短線とが、交わる関係、または、ねじれの位置関係にある半導体基板を提供する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

CVDエッチングおよび堆積シーケンスにより形成されるCMOSトランジスタ接合領域

【課題】CMOSトランジスタのソース−ドレイン置換技術に関し、装置一式を利用して基板材料に窪みをエッチングして、その後、応力を有する異なる材料を堆積することに関し、大気に曝すことなく、エッチングとその後の堆積とを行う方法の提供。

【解決手段】エッチングおよびデポジションによりCMOSトランジスタの接合領域を形成する方法であって、

第1接合領域270を形成すべくゲート電極190の隣の基板120の第1箇所と、前記基板120に第2接合領域280を形成すべく前記ゲート電極190を介して前記第1箇所とは反対側に位置する前記基板120の第2箇所とを除去する工程と、前記第1接合領域270と前記第2接合領域280とに結晶質材料のエピタキシャル厚みを有する層を形成する工程とを含み、前記除去する工程と前記形成する工程は同一のチャンバ内で前記チャンバの封止を破ることなく行う。

(もっと読む)

電界効果トランジスタ及びその製造方法、並びに半導体装置

【課題】横型二重拡散構造を有する電界効果トランジスタの高集積化を可能とする半導体装置を提供する。

【解決手段】半導体装置1Nは、ゲート電極17の幅方向両側のうちの一方の側で延在するP型ボディ領域20Pと、他方の側で延在するN型ボディ領域20Nと、その一方の側に形成されてP型ボディ領域20Pと接合するP型不純物拡散領域32Pと、その他方の側でP型不純物拡散領域32Pと対向する位置に形成されてN型ボディ領域20Nと接合するN型不純物拡散領域32Nと、その一方の側に形成されてP型ボディ領域30Nと接合するN型不純物拡散領域31Nと、その他方の側でN型不純物拡散領域31Nと対向する位置に形成されてN型ボディ領域20Nと接合するP型不純物拡散領域31Pとを備える。

(もっと読む)

埋め込みガードリング及び耐放射線性分離構造並びにその製造方法

【課題】大量の商業マイクロエレクトロニクスメーカーがアクセスし易い最先端の基礎設備を使用して、高性能且つ費用対効果に優れた耐放射線性集積回路(RHICs)を提供する。

【解決手段】様々な形式の放射線エネルギーによって引き起こされる有害な影響を減少し、又は排除するために、従来の設計及びプロセスを使用する一方で特殊構造を含んで半導体デバイスを作成する。このような半導体デバイスは本願で開示された1台以上の寄生的な分離デバイス、及び/又は、埋め込みガードリング構造を含む。これら新規な構造に対応する設計、及び/又は、工程ステップの導入には、従来のCMOS製作工程との互換性がある。したがって、比較的低い費用で比較的簡単に実施することができる。

(もっと読む)

半導体集積回路

【課題】レイアウト面積が増大を抑制しつつ、高電位入力から低電位出力を生成するトランジスタのESD耐性を向上させる。

【解決手段】電源配線112、113間にはPチャンネル電界効果トランジスタ131が接続され、電源配線113とPチャンネル電界効果トランジスタ131のゲートとの間にはPチャンネル電界効果トランジスタ132が接続され、異常電圧検出回路142は、第1の電圧V1と第3の電圧V3との電位差に基づいてPチャンネル電界効果トランジスタ132をオン/オフ制御する。

(もっと読む)

半導体集積回路装置

【課題】回路動作速度を犠牲にすることなく、待機時の消費電力を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】同一Si基板上に少なくともソース・ゲート間又はドレイン・ゲート間に流れるトンネル電流の大きさが異なる複数種類のMOSトランジスタを設け、当該複数種類のMOSトランジスタの内、トンネル電流が大きい少なくとも1つのMOSトランジスタで構成された主回路と、トンネル電流が小さい少なくとも1つのMOSトランジスタで構成され、主回路と2つの電源の少なくとも一方の間に挿入した制御回路を有し、制御回路に供給する制御信号で主回路を構成するソース・ゲート間又はドレイン・ゲート間に電流が流れることの許容/不許容を制御し、待機時間中に主回路のINとOUTの論理レベルが異なる際のIN−OUT間リーク電流を防止するスイッチを主回路のIN又はOUTに設ける。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を形成する。

【解決手段】薄膜領域TA1中に第1の素子領域、第2の素子領域および第1の分離領域を有し、厚膜領域TA2中に第3の素子領域、第4の素子領域および第2の分離領域を有する半導体装置を次のように製造する。(a)絶縁層1bを介してシリコン層1cが形成された基板を準備する工程と、(b)基板の第1の分離領域および第2の分離領域のシリコン層中に素子分離絶縁膜3を形成する工程と、を有するよう製造する。さらに、(c)薄膜領域TA1にハードマスクを形成する工程と、(d)ハードマスクから露出した、第3の素子領域および第4の素子領域のシリコン層上に、それぞれシリコン膜7を形成する工程と、(e)第3の素子領域および第4の素子領域のシリコン膜7間に、素子分離絶縁膜11を形成する工程と、を有するよう製造する。

(もっと読む)

半導体回路および論理回路

【課題】論理回路をできるだけ小さな回路面積で形成可能な半導体回路を提供する。

【解決手段】半導体回路は、第1および第2のトランジスタで共有されるゲート領域と、ゲート領域に接するように配置されるゲート絶縁膜と、ゲート絶縁膜に接するように配置される半導体層と、を備える。半導体層は、ゲート領域に対向するように配置され、第1のトランジスタのチャネルとして用いられる反転層形成領域と、反転層形成領域に沿って、あるいは反転層形成領域と交差するように形成され、第2のトランジスタのチャネルとして用いられる導通路形成領域と、を有する。導通路形成領域は、ゲート領域が所定の電圧範囲のときには、反転層形成領域から伸びる空乏層により遮断される。

(もっと読む)

半導体装置およびその製造方法

【課題】エピタキシャル層を具備する半導体構造の改良を図ること。

【解決手段】 実施形態の半導体構造は、第1の格子定数を具備する第1の結晶を具備する半導体基板と、前記半導体基板上に形成され、第2の格子定数を具備する第2の結晶を具備する多層エピタキシャル層とを具備している。前記第1の格子定数は、前記第2の格子定数と異なる。前記多層エピタキシャル層は、第1のエピタキシャル層および第2のエピタキシャル層を具備している。前記第1のエピタキシャル層の第1の導電型不純物は、前記第2のエピタキシャル層の第2の導電型不純物よりも少ない。

(もっと読む)

半導体装置及びその製造方法

【課題】低廉なプロセスにて高性能・高信頼性を実現しうる半導体装置及びその製造方法を提供する。

【解決手段】第1の領域に形成された第1導電型の不純物層及び第1のエピタキシャル半導体層と、第1のエピタキシャル半導体層上に第1のゲート絶縁膜を介して形成された第1のゲート電極と、第1の領域に形成された第1のソース/ドレイン領域とを有する第1のトランジスタと、第2の領域に形成された第2導電型の不純物層及び第1のエピタキシャル半導体層とは膜厚の異なる第2のエピタキシャル半導体層と、第2のエピタキシャル半導体層上に第1のゲート絶縁膜と同じ膜厚の第2のゲート絶縁膜を介して形成された第2のゲート電極と、第2の領域に形成された第2のソース/ドレイン領域とを有する第2のトランジスタとを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】n型MOSトランジスタ及びp型MOSトランジスタのそれぞれに共通のゲート電極材料を用い、且つそれぞれの閾値電圧が適切な値に調整された半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1トランジスタ11及び第2トランジスタ12を備えている。第1トランジスタ11は、第1ゲート絶縁膜131と、第1ゲート電極133とを有し、第2トランジスタ12は、第2ゲート絶縁膜132と、第2ゲート電極134とを有している。第1ゲート絶縁膜131及び第2ゲート絶縁膜132は、第1絶縁層151及び第2絶縁層152を含む。第1ゲート電極133及び第2ゲート電極134は、断面凹形の第1導電層155及び該第1導電層155の上に形成された第2導電層156を含む。第1絶縁層151及び第2絶縁層152は平板状であり、第1ゲート絶縁膜131は、仕事関数調整用の第1元素を含んでいる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を形成する。

【解決手段】本発明は、pチャネル型MISFETをpMIS形成領域1Aに有し、nチャネル型MISFETをnMIS形成領域1Bに有する半導体装置の製造方法であって、HfON膜5上にAl膜8aを形成する工程と、Al膜上にTiリッチなTiN膜7aを形成する工程と、を有する。さらに、nMIS形成領域1BのTiN膜およびAl膜を除去する工程と、nMIS形成領域1BのHfON膜5上およびpMIS形成領域1AのTiN膜7a上にLa膜8bを形成する工程と、La膜8b上にNリッチなTiN膜7bを形成する工程と、熱処理を施す工程とを有する。かかる工程によれば、pMIS形成領域1Aにおいては、HfAlON膜のN含有量を少なくでき、nMIS形成領域1Bにおいては、HfLaON膜のN含有量を多くできる。よって、eWFを改善できる。

(もっと読む)

半導体装置及びその製造方法

【課題】ソース及びドレインのいずれか一方に高抵抗成分が付加されたときドレイン電流の低下を抑制する。

【解決手段】一つの実施形態によれば、半導体装置は基板、第一のソース及びドレイン、第二のソース及びドレイン、ゲート電極膜が設けられる。第一のソース及びドレインと第二のソース及びドレインは、基板表面に設けられる。第二のソース及びドレインの一方は、第一のソース及びドレインの一方に隣接配置される。第二のソース及びドレインの他方は、第一のソース及びドレインの他方に隣接配置される。ゲート電極膜は、第一及び第二のソース及びドレインの一方と第一及び第二のソース及びドレインの他方の間の基板表面上に設けられ、ゲート絶縁膜を介して設けられる。第一のソース及びドレインとゲート電極膜は第一のFETを構成し、第二のソース及びドレインとゲート電極膜は第二のFETを構成する。

(もっと読む)

半導体装置

【課題】隣接する2つのトランジスタ同士が接続された構成を有し、省スペースと電流集中による信頼性の低下の抑制とを両立させた半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1のトランジスタ101と接続された第1のバス111、第2のトランジスタ102と接続された第2のバス112と、第1のバス111と第2のバス112との間に形成され、第1のバス111と第2のバス112とを接続するバス間配線121とを備えている。バス間配線121は、第1のバス111における第2のバス112と対向する辺の一部及び第2のバス112における第1のバス111と対向する辺の一部と接続されている。第1のコンタクトパッド131は、第1のバス111の一部と接続され、第2のコンタクトパッド132は、第2のバス112の一部と接続されている。

(もっと読む)

半導体装置

【課題】小型化を実現し得る半導体装置を提供することにある。

【解決手段】半導体基板に形成され、素子分離領域により画定された第1の素子領域12bと、第1の素子領域上に形成された第1のゲート電極21bと、第1のゲート電極の第1の側における第1の素子領域に形成された第1のソース領域32Sと、第1のゲート電極の第2の側における第1の素子領域に形成された第1のドレイン領域32Dとを有する第1のトランジスタ36と、第1のゲート電極の第1の側における素子分離領域上に、第1のゲート電極と並行するように形成された第1のパターン38aと、第1のソース領域に接続された第1の導体プラグ44cとを有し、第1の導体プラグは、接地線及び電源線のうちの一方に電気的に接続されており、第1のパターンは、接地線及び電源線のうちの他方に電気的に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】寄生バイポーラトランジスタのゲインを低下することにより、誤動作や動作特性の変動が少ない半導体装置及びその製造方法を得る。

【解決手段】シリコン層3の上面上には、シリコン酸化膜6が部分的に形成されている。シリコン酸化膜6上には、ポリシリコンから成るゲート電極7が部分的に形成されている。ゲート電極7の下方に存在する部分のシリコン酸化膜6は、ゲート絶縁膜として機能する。ゲート電極7の側面には、シリコン酸化膜8を挟んで、シリコン窒化膜9が形成されている。シリコン酸化膜8及びシリコン窒化膜9は、シリコン酸化膜6上に形成されている。ゲート長方向に関するシリコン酸化膜8の幅W1は、シリコン酸化膜6の膜厚T1よりも大きい。

(もっと読む)

半導体装置の製造方法

【課題】不純物濃度のピーク位置までの深さが互いに異なる複数の不純物領域を半導体基板内に従来よりも少ない工数で形成するための技術を提供する。

【解決手段】複数の不純物領域を半導体基板内に有し、半導体基板の表面から複数の不純物領域の不純物濃度のピーク位置までの深さが互いに異なる半導体装置の製造方法が提供される。本方法は、光透過率が互いに異なる複数の領域を含むフォトマスクを用いて、半導体基板に塗布されたフォトレジストを露光する露光工程と、フォトレジストを現像して、フォトレジストの露光量に依存した互いに異なる膜厚を有する複数の領域を含むレジストパターンを形成する現像工程と、レジストパターンの膜厚が互いに異なる複数の領域を通して半導体基板に不純物イオンを注入して、半導体基板の表面からピーク位置までの深さが互いに異なる複数の不純物領域を形成する注入工程とを有し、ピーク位置までの深さは、注入される不純物イオンが通るレジストパターンの膜厚に依存することを特徴とする。

(もっと読む)

多動作電圧垂直置換ゲート(VRG)トランジスタ

【課題】本発明は、多動作電圧のMOSFETを生じる形態を提供する。

【解決手段】一般に、集積回路構造は平面に沿って形成された主表面を有する半導体領域と、表面中に形成された第1及び第2の空間的に分離されたドープ領域を含む。第1の領域とは異なる伝導形のチャネルを形成する第3のドープ領域が、第1の領域上に配置される。異なる伝導形をもち、チャネルを形成する第4のドープ領域が、第2の領域上に配置される。2つのトランジスタのそれぞれにゲート構造を形成するプロセスにより、2つのトランジスタ間で異なる厚さの酸化物層が形成される。各トランジスタは更に、それぞれ第3及び第4の領域上に配置され、第3及び第4の領域に対して相対する伝導形をもつ第5及び第6層を含む。

(もっと読む)

半導体装置

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

141 - 160 / 3,186

[ Back to top ]