Fターム[5F048AC03]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 集積回路要素 (9,617) | MOS+MOS (7,604) | CMOS(Complementary MOS) (4,005)

Fターム[5F048AC03]の下位に属するFターム

TFT・CMOS (819)

Fターム[5F048AC03]に分類される特許

121 - 140 / 3,186

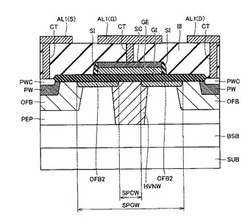

半導体装置およびその製造方法

【課題】オン抵抗を低減し、かつ高耐圧で駆動することが可能な半導体装置を提供する。

【解決手段】当該高耐圧トランジスタは、第1の不純物層PEPと、第1の不純物層PEPの内部に形成される第2の不純物層HVNWと、第2の不純物層HVNWを挟むように、第1の不純物層PEPの内部に形成される1対の第3の不純物層OFBおよび第4の不純物層PWと、第3の不純物層OFBから、第2の不純物層HVNWの配置される方向へ、主表面に沿って突出するように、第1の不純物層PEPの最上面から第1の不純物層PEPの内部に形成される第5の不純物層OFB2と、第2の不純物層HVNWの最上面の上方に形成される導電層GEとを備える。第4の不純物層PWにおける不純物濃度は、第3および第5の不純物層OFB,OFB2における不純物濃度よりも高く、第5の不純物層OFB2における不純物濃度は、第3の不純物層OFBにおける不純物濃度よりも高い。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタを覆うシリコン窒化膜を用いて、該トランジスタの駆動能力をより一層向上することができるようにする。

【解決手段】Pウェル102の上に、NMOSゲート絶縁膜104を介在させて形成されたNMOSゲート電極106と、Pウェル102におけるNMOSゲート電極106の両側方の領域に形成されたn型ソースドレイン領域112と、Pウェル102の上に形成され、NMOSゲート電極106及びn型ソースドレイン領域112を覆うように形成されたシリコン窒化膜118とを有している。シリコン窒化膜118を構成するシリコンは、その同位体29Si又は30Siの比率が50%以上である。

(もっと読む)

半導体集積回路のトランジスタ素子

【課題】簡易な構成であり且つトランジスタ毎にしきい値電圧が異なる半導体集積回路のトランジスタ素子の提供。

【解決手段】ソース領域16A,16D、ドレイン領域16B,16Cおよびチャネル領域を備えた支持基板(Si基板2)上に、ゲート電極10とゲート電極10を覆う中間膜18とを備える第1および第2のトランジスタ構造を、少なくとも有し、前記第1のトランジスタ構造におけるゲート電極10とチャネル領域とが重なる領域には、中間膜18上に、第1のトランジスタ構造のしきい値電圧に変動を及ぼす範囲でゲート電極10とチャネル領域とが重なる領域の大部分を覆うよう支持基板(Si基板2)に応力を印加する応力膜22を有し、前記第2のトランジスタ構造におけるゲート電極10とチャネル領域とが重なる領域には、中間膜18上に、支持基板(Si基板2)に応力を印加する応力膜22を有さない半導体集積回路のトランジスタ素子。

(もっと読む)

半導体装置

【課題】充電対象素子へ充電電流を効率的に供給することが可能な半導体装置を提供する。

【解決手段】充電対象素子Cに充電電流を供給する半導体装置1は、第1導電型の半導体層1と、充電対象素子Cの第1電極に結合される第1ノードN1を有し、半導体層1の主表面上に形成される第2導電型の第1の半導体領域2と、電源電圧が供給される電源電位ノードNL1に結合される第2ノードN3および第3ノードN4を有し、第1の半導体領域2の表面において半導体層1と間隔をあけて形成される第1導電型の第2の半導体領域3と、第2ノードN3および第3ノードN4から半導体層1への電荷キャリアの移動を制限する電荷キャリア移動制限部とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】 JFET等のような低ノイズ特性が要求される半導体装置において、発生するノイズを低減すると共に、半導体装置を小さい寸法で製造する。

【解決手段】 半導体装置は、半導体層(101)に形成された素子分離(102)、第1導電型の不純物層(104)、第1導電型のソース領域(106)、第1導電型のドレイン領域(107)、第2導電型のゲート領域(105)、絶縁膜(108)を介して形成された制御電極(109)を備える。制御電極(109)に電圧を印加すると、半導体装置の動作中に制御電極(109)の下の不純物層(104)に空乏層を発生させることができ、キャリアは絶縁膜(108)と不純物層(104)の界面から離れて流れる。

(もっと読む)

半導体装置

【課題】ブートストラップ方式のドライブ回路を有する半導体装置において、ブートストラップダイオードの順バイアス時にp-基板側に流れるホールによるリーク電流を抑制することができる半導体装置を提供することにある。

【解決手段】ブートストラップダイオードDb下にSON構造の空洞3を形成し、ブートストラップダイオードDbとグランド電位(GND)となるGNDp領域4との間のn-エピ層2にその空洞3に達するフローティングp領域5を形成することで、外部のブートストラップコンデンサC1充電時のp-基板1へのホールによるリーク電流を抑えることができる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】リーク電流および閾値を低減させるゲート絶縁膜を提供する。

【解決手段】図1に示すように、半導体基板1上に、ゲート絶縁膜3を形成するゲート絶縁膜形成工程と、ゲート絶縁膜3上に、ゲート電極4を形成するゲート電極形成工程と、を備え、ゲート絶縁膜形成工程は、第1金属の酸化膜あるいは酸窒化膜を、成膜する第1の成膜工程と、第1金属の酸化膜あるいは酸窒化膜上に第2金属または、その酸化物を成膜する第2の成膜工程と、第2金属を第1金属の酸化膜中に拡散させるために熱処理する熱処理工程の3工程を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコンエピタキシャル層の支えの喪失を防止した、局所SOI構造の形成方法の提供。

【解決手段】SiGe混晶層31SG1〜31SG4とシリコンエピタキシャル層31ES1,31ES2,31ES3および31ES4が積層された構造において、

それぞれ、Nウェル31NW及びPウェル31PWがSiGe混晶層31SG1〜31SG4側に突き出る構造を形成し、SiGe混晶層31SG1〜31SG4をエッチングにより除去する際に、支えとなるようにする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能向上を図る。

【解決手段】ゲート電極GE1,GE2,GE3,GE4の側壁上にオフセットスペーサを形成した状態で半導体基板1のnMIS領域1A,1BおよびpMIS領域1C,1Dのそれぞれにイオン注入を行うことで、ソース・ドレインのエクステンション領域を形成する。この際、nMIS領域1A,1BおよびpMIS領域1C,1Dのそれぞれに対して別々のフォトレジストパターンを用いて個別にイオン注入を行うが、フォトレジストパターンを形成し直す度に、オフセットスペーサを形成し直すようにする。

(もっと読む)

半導体装置及びその製造方法

【課題】製造プロセスが複雑になるといったことを防ぎつつ、n型及びp型MOSトランジスタについて両方の性能を向上させた半導体装置を提供する。

【解決手段】半導体基板1の面内に、n型MOSトランジスタと、p型MOSトランジスタとを備える半導体装置であって、n型MOS型トランジスタが形成される第1の拡散層2aの間を絶縁分離する第1の絶縁層3aと、p型MOS型トランジスタが形成される第2の拡散層2cの間を絶縁分離する第2の絶縁層3bとを備え、第1の絶縁層3aは、半導体基板1の表層に形成された第1の溝部4aに、シリコン窒化膜5と、このシリコン窒化膜5の上にシリコン酸化膜6とを埋め込むことによって形成され、第2の絶縁層3bは、半導体基板1の表層に第1の溝部4aよりも幅広となるように形成された第2の溝部4bに、シリコン酸化膜6を埋め込むことによって形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】 層間絶縁膜をCMP法で研磨、平坦化する際、MOS型トランジスタのチャネル領域に応力を与えるためにゲート電極を覆うように形成される応力ライナー膜が研磨されて、トランジスタ特性の変動やバラツキが発生しないようにする。

【解決手段】 第1活性領域(例えばPチャネルトランジスタ形成領域)上のゲート電極(シリコン膜14と金属シリサイド膜15との積層膜)上には第1応力膜(圧縮応力ライナー膜)16のみを形成し、第2活性領域(例えばNチャネルトランジスタ領域)上のゲート電極上には第2応力膜(引っ張り応力ライナー膜)18のみを形成する。一方、素子分離10上のゲート電極上には第1および第2応力膜16、18の積層膜を形成する。層間絶縁膜20のCMP法による研磨は、素子分離10上の第2応力膜18の露出後に停止する。

(もっと読む)

半導体基板または半導体装置の製造方法

【課題】平板状空洞を形成する際におけるホール半径Rと、ホールとホールの最短距離Sのプロセスマージンを広げ、信頼性の高い半導体装置の製造方法を提供すること。

【解決手段】半導体基板1の表面にホール4を複数形成し、非酸化性雰囲気のアニール処理により、該半導体基板1の表面を半導体の表面マイグレーションを利用して平坦化し、基板内部に平板状空洞6を形成する際に、前記ホール4の開口部が閉じる前に半導体のソースガスを供給する。

(もっと読む)

半導体装置、および、その製造方法

【課題】製造効率の向上、コストダウン、信頼性の向上を実現する。

【解決手段】第1導電型の第1電界効果トランジスタを第1基板に設ける。そして、第1導電型と異なる第2導電型の第2電界効果トランジスタを第2基板に設ける。そして、第1基板と第2基板とのそれぞれを対面させて貼り合わせる。そして、第1電界効果トランジスタと第2電界効果トランジスタとの間を電気的に接続させる。

(もっと読む)

半導体装置の製造方法

【課題】第1MISFETのゲート電極と第2MISFETのゲート電極とを別工程で形成する半導体装置の製造技術において、第1MISFETと第2MISFETの信頼性向上を図ることができる技術を提供する。

【解決手段】半導体基板20上にゲート絶縁膜26、電荷蓄積膜27、絶縁膜28、ポリシリコン膜29、酸化シリコン膜30、窒化シリコン膜31およびキャップ絶縁膜32からなる積層膜を形成する。そして、フォトリソグラフィ技術およびエッチング技術を使用して、低耐圧MISFET形成領域および高耐圧MISFET形成領域に形成されている積層膜を除去する。その後、半導体基板20上にゲート絶縁膜34、36、ポリシリコン膜37およびキャップ絶縁膜38を形成する。そして、低耐圧MISFET形成領域および高耐圧MISFET形成領域にゲート電極を形成した後、メモリセル形成領域にゲート電極を形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】多層配線を形成する際における配線の加工に要する工程を簡便にすることを課題

とする。また、開口径の比較的大きいコンタクトホールに液滴吐出技術やナノインプリン

ト技術を用いた場合、開口の形状に沿った配線となり、開口の部分は他の箇所より凹む形

状となりやすかった。

【解決手段】高強度、且つ、繰り返し周波数の高いパルスのレーザ光を透光性を有する絶

縁膜に照射して貫通した開口を形成する。大きな接触面積を有する1つの開口を形成する

のではなく、微小な接触面積を有する開口を複数設け、部分的な凹みを低減して配線の太

さを均一にし、且つ、接触抵抗も確保する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高誘電率ゲート絶縁膜を用いたCMIS型半導体集積回路において、短チャネル長、且つ狭チャネル幅のデバイス領域では、ソースドレイン領域の活性化アニールによって、高誘電率ゲート絶縁膜とシリコン系基板部との界面膜であるILの膜厚が増加することによって、閾値電圧の絶対値が増加するという問題がある。

【解決手段】本願の一つの発明は、MISFETを有する半導体集積回路装置の製造方法において、MISFETのゲートスタック及びその周辺構造を形成した後、半導体基板表面を酸素吸収膜で覆い、その状態でソースドレインの不純物を活性化するためのアニールを実行し、その後、当該酸素吸収膜を除去するものである。

(もっと読む)

半導体装置

【課題】たとえばDC−DCコンバータ等の電源または電力変換機器のスイッチング等に使用されるパワーMOSFET等の絶縁ゲートを有するパワー系能動素子は、スイッチングの高速化に伴い、ゲート容量を極力小さくする必要がある。このためには、チャネルとならない部分のゲート電極を取り去り、スプリットゲートとする手法が有効とされている。しかし、Nチャネル型パワーMOSFETを例に取り説明すると、その反作用として、チャネルを形成するP型ボディ領域の端部に電界が集中するため、パンチスルー耐圧が低下する等の問題が発生する。

【解決手段】本願の一つの発明は、プレーナ−バーティカル型パワーMOSFET等の絶縁ゲートを有するパワー系能動素子を有する半導体装置に於いて、各アクティブセル内のスプリットゲート間にトレンチ内に延在するフィールドプレート、すなわち、トレンチフィールドプレートを設けたものである。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高誘電率ゲート絶縁膜を用いたCMIS型半導体集積回路において、短チャネル長、且つ狭チャネル幅のデバイス領域では、ソースドレイン領域の活性化アニールによって、高誘電率ゲート絶縁膜とシリコン系基板部との界面膜であるILの膜厚が増加することによって、閾値電圧の絶対値が増加するという問題がある。

【解決手段】本願の一つの発明は、MISFETを有する半導体集積回路装置の製造方法において、MISFETのゲートスタック及びその周辺構造を形成した後、半導体基板表面を酸素吸収膜で覆い、その状態でソースドレインの不純物を活性化するためのアニールを実行し、その後、当該酸素吸収膜を除去するものである。

(もっと読む)

電界効果トランジスタ

【課題】急峻なS値特性を有するとともに、ソース/ドレイン領域が同じ導電型となる対称構造を有する電界効果トランジスタを提供する。

【解決手段】本実施形態による電界効果トランジスタは、半導体層と、前記半導体層に離間して設けられたソース領域およびドレイン領域と、前記ソース領域と前記ドレイン領域との間の前記半導体層上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ソース領域および前記ドレイン領域側の前記ゲート電極の少なくとも一方の側面に設けられた高誘電体のゲート側壁と、を備え、前記ソース領域および前記ドレイン領域は前記ゲート電極の対応する側面から離れている。

(もっと読む)

半導体素子及び半導体素子形成方法

【課題】ゲルマニウムをチャネル材料とする金属/ゲルマニウムからなるソース/ドレイン構造を有する半導体素子を提供する。

【解決手段】半導体と金属とが接合してソース/ドレイン構造を形成する半導体素子において、ゲルマニウム(Ge)を3価元素(又は5価元素)でドーピングしたp型ゲルマニウム(又はn型ゲルマニウム)をチャネル2の材料とし、当該p型ゲルマニウム(又はn型ゲルマニウム)の任意の結晶面における原子配置と同一の原子配置である結晶面を有する金属3を、前記同一の原子配置である結晶面で接合して界面を形成し、当該形成された界面を用いたソース/ドレイン構造を有する。

(もっと読む)

121 - 140 / 3,186

[ Back to top ]