Fターム[5F048AC10]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 集積回路要素 (9,617) | L、C、R、ダイオード等を含む (1,648)

Fターム[5F048AC10]に分類される特許

101 - 120 / 1,648

記憶素子、記憶装置、信号処理回路

【課題】消費電力を抑えることができる信号処理回路を提供する。

【解決手段】記憶素子に電源電圧が供給されない間は、揮発性のメモリに相当する第1の記憶回路に記憶されていたデータを、第2の記憶回路に設けられた第1の容量素子によって保持する。酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、第1の容量素子に保持された信号は長期間にわたり保たれる。こうして、記憶素子は電源電圧の供給が停止した間も記憶内容(データ)を保持することが可能である。また、第1の容量素子によって保持された信号を、第2のトランジスタの状態(オン状態、またはオフ状態)に変換して、第2の記憶回路から読み出すため、元の信号を正確に読み出すことが可能である。

(もっと読む)

半導体装置

【課題】導体半導体接合を用いて、優れた特性を示す、あるいは、作製の簡単な、あるいは、より集積度の高い電界効果トランジスタを提供する。

【解決手段】半導体層の電子親和力よりも仕事関数の小さな導体との接合においては、導体より半導体層にキャリアが注入された領域が生じる。そのような領域を電界効果トランジスタ(FET)のオフセット領域、あるいは、インバータ等の半導体回路の抵抗として用いる。また、ひとつの半導体層中にこれらを設けることにより集積化した半導体装置を作製できる。

(もっと読む)

半導体装置

【課題】高速動作、低消費電力である半導体装置の提供。

【解決手段】結晶性のシリコンをチャネル形成領域に有する第1のトランジスタを用いた記憶素子と、当該記憶素子のデータを記憶する容量素子と、当該容量素子における電荷の供給、保持、放出を制御するためのスイッチング素子である第2のトランジスタとを有する。第2のトランジスタは第1のトランジスタを覆う絶縁膜上に位置する。第1及び第2のトランジスタは、ソース電極又はドレイン電極を共有している。上記絶縁膜は、加熱により一部の酸素が脱離する第1の酸化絶縁膜と、酸素の拡散を防ぎ、なおかつ当該第1の酸化絶縁膜の周囲に設けられた第2の酸化絶縁膜とを有し、第2のトランジスタが有する酸化物半導体膜は、上記第1の酸化絶縁膜に接し、かつチャネル形成領域である第1の領域と、第1の領域を挟み、第1及び第2の酸化絶縁膜に接する一対の第2の領域とを有する半導体装置。

(もっと読む)

記憶装置及び信号処理回路

【課題】電源の供給を停止しても、記憶している論理状態が消えない記憶装置を提供する。また、該記憶装置を用いることで、電源供給停止により消費電力を抑えることができる信号処理回路を提供する。

【解決手段】第1及び第2のノードを有する論理回路と、第1のノードに接続された第1の記憶回路と、第2のノードに接続された第2の記憶回路と、第1のノード、第2のノード、第1の記憶回路、及び第2の記憶回路に接続されたプリチャージ回路と、を有し、読み出しの際に、プリチャージ回路は、プリチャージ電位を第1のノード及び第2のノードに出力し、第1の記憶回路及び第2の記憶回路は、チャネルが酸化物半導体膜に形成されるトランジスタを含む記憶装置である。

(もっと読む)

位相同期回路および位相同期回路を用いた半導体装置

【課題】スタンバイ状態からの復帰後、電圧制御発振器に入力される電圧信号が短時間で一定となる、消費電力の低減された位相同期回路を提供することを課題とする。

【解決手段】電圧制御発振器の入力端子とループフィルタを構成する容量素子の間に、酸化物半導体材料を用いて半導体層を形成したトランジスタを設け、通常動作状態の時には当該トランジスタをオン状態に、スタンバイ状態の時には当該トランジスタをオフ状態とする。

(もっと読む)

半導体装置

【課題】同一チップ内にショットキーバリアダイオードを備える半導体装置およびその製造技術において、信頼性を向上させる。

【解決手段】p型の半導体基板1の主面S1上に形成された、n型のnウェル領域w1nと、その中の一部に形成された、nウェル領域w1nよりも不純物濃度の高いn型カソード領域nCa1と、それを環状に囲むようにして形成されたp型ガードリング領域pgと、n型カソード領域nCa1とp型ガードリング領域pgとを一体的に覆い、かつ、それぞれに電気的に接続するようにして形成されたアノード導体膜EAと、p型ガードリング領域pgの外側に分離部2を隔てて形成されたn型カソード導通領域nCbと、これを覆い、かつ、電気的に接続するようにして形成されたカソード導体膜ECとを有し、アノード導体膜EAとn型カソード領域nCa1とはショットキー接続されていることを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】装置面積を増大させることなく、保護素子を有する半導体装置を提供する。

【解決手段】P型のIII族窒化物半導体からなる第1P型層200と、第1P型層200の一部上には、ゲート絶縁膜420およびゲート電極440とが設けられている。第1P型層200内のうち、ゲート電極440の両脇には、N型のソース領域340およびドレイン領域320が設けられている。また、第1P型層200の下には、N型のIII族窒化物半導体からなる第1N型層100が設けられている。基板内には、N型のIII族窒化物半導体とオーミック接続する材料からなるオーミック接続部(たとえばN型GaN層520)が、ソース領域340および第1N型層100と接するように設けられている。また、ドレイン電極600は、ドレイン領域320および第1P型層200と接するように設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】メタルゲート電極とポリシリコン抵抗素子とを同じ半導体基板に混載するとともに、半導体装置の設計の自由度を向上し、また、半導体装置の小型化を図る。

【解決手段】半導体基板1の主面上にゲート絶縁膜を介してMISFET用のメタルゲート電極が形成され、また、半導体基板1の主面上に積層パターンLPを介してポリシリコン抵抗素子用のシリコン膜パターンSPが形成されている。メタルゲート電極は金属膜とその上のシリコン膜とを有し、積層パターンLPは絶縁膜3aとその上の金属膜4aとその上の絶縁膜5aとを有し、絶縁膜3aは、前記ゲート絶縁膜と同層の絶縁膜により形成され、金属膜4aはメタルゲート電極の金属膜と同層の金属膜により形成され、シリコン膜パターンSPは、メタルゲート電極のシリコン膜と同層のシリコン膜により形成されている。シリコン膜パターンSPは、平面視で絶縁膜5aに内包されている。

(もっと読む)

検波器及び受信機

【課題】低電圧、低電流、或いは低電力といった条件下でも使用することが可能な検波器を提供する。

【解決手段】検波器は、信号入力端子に接続された第1導電型の第1の半導体領域と、信号出力端子に接続された第2導電型の第2の半導体領域であって、第1の半導体領域に接して位置する第2の半導体領域と、交流的に接地された第1導電型の第3の半導体領域であって、第1の半導体領域から離間し且つ第2の半導体領域に接して位置する第3の半導体領域と、一端が第2の半導体領域に接続され、他端が交流的に接地された第1の抵抗素子と、を含む。

(もっと読む)

半導体記憶装置

【課題】電源電圧の供給の停止及び再開を行う構成において、揮発性の記憶装置と不揮発性の記憶装置との間のデータの退避及び復帰の必要のない半導体記憶装置を提供する。

【解決手段】不揮発性の半導体記憶装置とする際、揮発性の記憶装置と不揮発性の記憶装置を分離することなく構成する。具体的に半導体記憶装置には、酸化物半導体を半導体層に有するトランジスタ及び容量素子に接続されたデータ保持部にデータを保持する構成とする。そしてデータ保持部に保持される電位は、電荷をリークすることなくデータの出力が可能なデータ電位保持回路及び電荷をリークすることなくデータ保持部に保持した電位を容量素子を介した容量結合により制御可能なデータ電位制御回路で制御される。

(もっと読む)

半導体装置

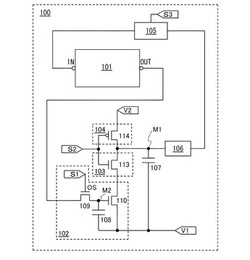

【課題】待機電力を十分に低減した新たな半導体装置を提供することを目的の一とする。

【解決手段】第1の電源端子と、第2の電源端子と、酸化物半導体材料を用いたスイッチ

ングトランジスタと、集積回路と、を有し、前記第1の電源端子と、前記スイッチングト

ランジスタのソース端子またはドレイン端子の一方は電気的に接続し、前記スイッチング

トランジスタのソース端子またはドレイン端子の他方と、前記集積回路の端子の一は電気

的に接続し、前記集積回路の端子の他の一と、前記第2の電源端子は電気的に接続した半

導体装置である。

(もっと読む)

半導体装置

【課題】動作速度の低下を抑制しつつ、消費電力を低減する。

【解決手段】第1の半導体領域の上に絶縁領域を有し、且つ絶縁領域の上に第2の半導体領域を有する基板に設けられた第1の電界効果トランジスタと、基板の上に設けられた絶縁層と、絶縁層の一平面に設けられ、酸化物半導体層を含む第2の電界効果トランジスタと、第2の電界効果トランジスタのソース及びドレインと同一工程により形成され、第1の電界効果トランジスタの閾値電圧を制御するための電圧が供給される制御端子と、を備える。

(もっと読む)

半導体装置

【課題】トランジスタが仮にディプレッション型である場合でも、安定して動作することができる半導体装置を提供する。

【解決手段】開示する発明の一態様の半導体装置は、第1の電位を第1の配線に供給する機能を有する第1のトランジスタと、第2の電位を第1の配線に供給する機能を有する第2のトランジスタと、第1のトランジスタのゲートに第1のトランジスタがオンをオンにするための第3の電位を供給した後、第3の電位の供給を止める機能を有する第3のトランジスタと、第2の電位を第1のトランジスタのゲートに供給する機能を有する第4のトランジスタと、第1の信号にオフセットを施した第2の信号を生成する機能を有する第1の回路と、を有し、第4のトランジスタのゲートには、第2の信号が入力され、第2の信号の最小値は、第2の電位未満の値である。

(もっと読む)

半導体集積回路

【課題】半導体集積回路における消費電力を低減すること。また、半導体集積回路における動作の遅延を低減すること。

【解決手段】記憶回路が有する複数の順序回路のそれぞれにおいて、酸化物半導体によってチャネル形成領域が構成されるトランジスタと、該トランジスタがオフ状態となることによって一方の電極が電気的に接続されたノードが浮遊状態となる容量素子とを設ける。なお、酸化物半導体によってトランジスタのチャネル形成領域が構成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。そのため、記憶回路に対して電源電圧が供給されない期間において当該トランジスタをオフ状態とすることで、当該期間における容量素子の一方の電極が電気的に接続されたノードの電位を一定又はほぼ一定に保持することが可能である。その結果、上述した課題を解決することが可能である。

(もっと読む)

半導体装置

【課題】占有面積が小さく、冗長性があり、かつリーク電流の小さい保護回路を提供する。

【解決手段】保護回路は、複数の非線形素子が重畳するように積層され、かつ該非線形素子が電気的に直列接続されている構成であり、該保護回路に含まれる少なくとも一つの非線形素子は、チャネル形成領域に酸化物半導体を用いたトランジスタをダイオード接続した素子であり、他の非線形素子は、チャネル形成領域にシリコンを用いたトランジスタをダイオード接続した素子、または、接合領域にシリコンを用いたダイオードとする。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、配線数を削減することによって高集積化が図られた半導体装置を提供することを目的とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込み用のワード線と読み出し用のワード線を共通化し、かつ書き込み用のビット線と読み出し用のビット線を共通化することにより配線数を削減し、単位面積あたりの記憶容量を増加させる。

(もっと読む)

半導体装置

【課題】周辺の回路構成を複雑にすることなく、繰り返しのデータの書き込みの際の劣化を低減することが可能な、不揮発性スイッチとして用いる半導体装置を提供する。

【解決手段】電源電圧が停止しても導通状態に関するデータの保持を、チャネル形成領域に酸化物半導体層を有する薄膜トランジスタに接続されたデータ保持部で行う構成とする。そしてデータ保持部は、ダーリントン接続された電界効果トランジスタ及びバイポーラトランジスタを有する電流増幅回路における、電界効果トランジスタのゲートに接続することでデータ保持部の電荷をリークすることなく、導通状態を制御する。

(もっと読む)

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

拡散抵抗素子およびその製造方法

【課題】ノイズおよび抵抗バラツキが小さな拡散抵抗の製造方法を提供することを目的とする。

【解決手段】半導体基板の表面付近にp型拡散層114を形成する工程と、拡散抵抗体となるp型拡散層114の第1領域の表面上に、層間絶縁膜とは異なる絶縁膜であって当該第1領域の表面を保護するカバー膜125を形成する工程と、カバー膜125を形成する工程の後、カバー膜125の前記第1領域に接する第2領域に前記第1領域よりも高い濃度で拡散抵抗体のコンタクト部となるp型拡散層116を形成する工程とを含む。

(もっと読む)

半導体装置

【課題】開示する発明の一態様は、安定して動作することが可能なパルス信号出力回路及

びそれを含むシフトレジスタを提供することを課題の一とする。

【解決手段】開示する発明の一態様のパルス信号出力回路は、第1乃至第10のトランジ

スタを有し、第1のトランジスタおよび第3のトランジスタのチャネル長Lに対するチャ

ネル幅Wの比W/Lは、第6のトランジスタのW/Lよりも大きく、第5のトランジスタ

のW/Lは、第6のトランジスタのW/Lよりも大きく、第5のトランジスタのW/Lは

、第7のトランジスタのW/Lと等しく、第3のトランジスタのW/Lは、第4のトラン

ジスタのW/Lよりも大きくする。これによって、安定して動作することが可能なパルス

信号出力回路及びそれを含むシフトレジスタを提供することができる。

(もっと読む)

101 - 120 / 1,648

[ Back to top ]