Fターム[5F048AC10]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 集積回路要素 (9,617) | L、C、R、ダイオード等を含む (1,648)

Fターム[5F048AC10]に分類される特許

61 - 80 / 1,648

ダイオード、半導体装置およびMOSFET

【課題】 発熱による半導体基板の温度上昇の影響を受けにくい構造で、ダイオードにおけるスイッチング損失の低減を実現することが可能な技術を開示する。

【解決手段】 本明細書で開示するダイオードは、カソード電極と、第1導電型の半導体からなるカソード領域と、低濃度の第1導電型の半導体からなるドリフト領域と、第2導電型の半導体からなるアノード領域と、アノード電極を備えている。そのダイオードは、前記ドリフト領域と前記アノード領域の間に形成された、前記ドリフト領域よりも濃度が高い第1導電型の半導体からなるバリア領域を備えている。そのダイオードでは、前記バリア領域が、外部の整流素子を介して、前記アノード電極と電気的に接続している。そのダイオードでは、前記整流素子の順方向電圧降下が、前記アノード領域と前記バリア領域の間のpn接合のビルトイン電圧よりも小さい。

(もっと読む)

半導体装置の作製方法

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

半導体集積回路

【課題】保護素子とガードリング領域との間のウィークスポットが破壊される危険性を軽減する。

【解決手段】半導体集積回路は、静電保護回路の保護素子Mn2を形成するために、第1導電型の半導体領域P−Wellと第2導電型の第1不純物領域Nと第1導電型の第2不純物領域Pにより形成されたガードリングGrd_Rngを具備する。第1不純物領域Nは、長辺と短辺を有する長方形の平面構造として半導体領域の内部に形成される。ガードリングは、第1不純物領域Nの周辺を取り囲んで半導体領域の内部に形成される。第1不純物領域Nの長方形の平面構造の短辺には、ウィークスポットWk_SPが形成される。長方形の長辺と対向するガードリングの第1部分では、複数の電気的コンタクトが形成される。長方形の短辺に形成されるウィークスポットと対向するガードリングの第2部分では、複数の電気的コンタクトの形成が省略される。

(もっと読む)

ダイオード、半導体装置およびMOSFET

【課題】 ダイオードにおけるスイッチング時の損失を低減することが可能な技術を開示する。

【解決手段】 本明細書で開示するダイオードは、カソード電極と、第1導電型の半導体からなるカソード領域と、低濃度の第1導電型の半導体からなるドリフト領域と、第2導電型の半導体からなるアノード領域と、金属からなるアノード電極を備えている。そのダイオードは、前記ドリフト領域と前記アノード領域の間に形成された、前記ドリフト領域よりも濃度が高い第1導電型の半導体からなるバリア領域と、前記バリア領域と前記アノード電極を接続するように形成された、前記バリア領域よりも濃度が高い第1導電型の半導体からなるピラー領域を備えている。そのダイオードでは、前記ピラー領域と前記アノード電極がショットキー接合している。

(もっと読む)

固体撮像装置、固体撮像装置の製造方法、電子機器

【課題】ランダムノイズの低減が図られた固体撮像装置を提供することを目的とする。また、その固体撮像装置を備えることにより、画質の向上が図られた電子機器を提供することを目的とする。

【解決手段】増幅トランジスタTraのドレイン側では、高濃度不純物領域28のみでドレイン領域38を構成し、ソース側では、増幅ゲート電極22側に形成され、ドレイン領域38を構成する高濃度不純物領域28よりも不純物濃度が低い低濃度不純物領域29からなるソース領域32を構成する。ドレイン領域38において、低濃度不純物領域を形成しないことで、実効ゲート長Leffを長くできる。また、増幅ゲート電極22のソース側では、増幅ゲート電極22側に低濃度不純物領域29が形成されるため、基板表面のポテンシャル変動を抑えることができる。

(もっと読む)

半導体装置

【課題】小面積、低電力動作、高速動作を並立する論理ゲートを含む半導体装置の構成を提供する。

【解決手段】本発明に係る半導体装置は、基板上にゲート絶縁膜を介してゲート電極と半導体層が配置され、半導体層に接続してソース電極とドレイン電極とが配置される薄膜トランジスタを2つ以上含む論理ゲートで構成される。少なくとも第一の薄膜トランジスタは、そのゲート電極が電気的に浮遊状態にあり、かつ、その半導体層は基板面に対して垂直方向について、ゲート電極とソース電極により挟まれる第1の重なり領域とゲート電極とドレイン電極により挟まれる第2の重なり領域を有する。また、少なくとも第二の薄膜トランジスタは、そのゲート電極が入力端子に接続され、かつ、そのチャネル層は基板面に対して垂直方向について、ゲート電極とソース電極により挟まれる第1の重なり領域とゲート電極とドレイン電極により挟まれる第2の重なり領域を有する。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いて作製された抵抗素子及び薄膜トランジスタを利用した論理回路、並びに該論理回路を利用した半導体装置を提供する。

【解決手段】抵抗素子354に適用される酸化物半導体層905上にシラン(SiH4)及びアンモニア(NH3)などの水素化合物を含むガスを用いたプラズマCVD法によって形成された窒化シリコン層910が直接接するように設けられ、且つ薄膜トランジスタ355に適用される酸化物半導体層906には、バリア層として機能する酸化シリコン層909を介して、窒化シリコン層910が設けられる。そのため、酸化物半導体層905には、酸化物半導体層906よりも高濃度に水素が導入される。結果として、抵抗素子354に適用される酸化物半導体層905の抵抗値が、薄膜トランジスタ355に適用される酸化物半導体層906の抵抗値よりも低くなる。

(もっと読む)

半導体装置およびその製造方法

【課題】抵抗素子の抵抗値のばらつきが抑制される半導体装置と、その製造方法とを提供する。

【解決手段】抵抗素子となるポリシリコン膜が形成される。そのポリシリコン膜が所定の形状にパターニングされる。パターニングされたポリシリコン膜PSAを覆うCVD酸化膜ZF1,ZF2にエッチングを施すことによって、抵抗本体となるポリシリコン膜の部分を覆う部分を残して、コンタクト領域が形成されるCVD酸化膜の部分が除去される。ポリシリコン膜を覆う残されたCVD酸化膜ZF1,ZF2の部分を注入マスクとして、BF2を注入することにより、コンタクト領域に高濃度領域HCが形成される。

(もっと読む)

EL表示装置

【課題】開口率を向上することができるEL表示装置である。

【解決手段】薄膜トランジスタと、容量と、発光素子と、発光素子へ電流を供給することができる機能を有する配線と有するEL表示装置である。発光素子は、陰極と、陽極と、陰極と陽極との間に設けられたEL材料とを有し、容量は、第2の領域と、第2の領域上に第1の絶縁膜を介して設けられる第3の領域とを有する。第1の絶縁膜は、薄膜トランジスタのゲート絶縁膜となり、さらに容量の絶縁膜となることができる。

(もっと読む)

集積されたダイオードを有するSOI基板を備える複合半導体装置

【課題】高電圧が印加されても、故障しにくい複合半導体装置を提供する。

【解決手段】複合半導体装置200は、ダイオード210及び絶縁層204を含むSOI基板(semiconductor on insulator)を備える。複合半導体装置200は、ダイオード210の上に形成された遷移体220及び遷移体220の上に形成されたトランジスタ230も含む。ダイオード210は半導体貫通ビア、外部電気接続部又はその両方の組み合わせを用いてトランジスタ230の両端間に接続される。

(もっと読む)

半導体装置

【課題】小型でコストが低い半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、導電形がp形のソース領域と、導電形がp形のドレイン領域と、前記ソース領域と前記ドレイン領域との間に設けられ、導電形がn形のチャネル領域と、前記チャネル領域上に設けられた下側ゲート絶縁膜と、前記下側ゲート絶縁膜上に設けられた下側ゲート電極と、前記下側ゲート電極上に設けられた上側ゲート絶縁膜と、前記上側ゲート絶縁膜上に設けられた上側ゲート電極と、前記下側ゲート電極と前記ソース領域との間に接続されたスイッチング素子と、を備える。

(もっと読む)

ネスト化複合スイッチ

【課題】高いスイッチング速度及び低いオン状態抵抗を有し、電圧降伏耐性を強化したネスト化複合スイッチを提供する。

【解決手段】ネスト化複合スイッチ240は、複合スイッチに結合されたノーマリオン・プライマリ・トランジスタを含む。複合スイッチは、中間型トランジスタ222とカスコード接続された低電圧(LV)トランジスタ224を含み、中間型トランジスタは、LVトランジスタよりは大きく、ノーマリオン・プライマリ・トランジスタよりは小さい降伏電圧を有する。1つの実現では、ノーマリオン・プライマリ・トランジスタはIII-V族トランジスタとすることができ、LVトランジスタはIV族LVトランジスタとすることができる。

(もっと読む)

電気光学装置、電気光学装置の駆動方法および電子機器

【課題】シリコン基板にOLEDのような発光素子を含む画素回路を形成する。

【解決手段】画素回路が配列する表示部100と、表示部100から離間して囲むように設けられ、複数の画素回路を駆動する走査線駆動回路140、データ線駆動回路150とがシリコン基板に形成される。Nウェル104は、表示部100にわたって連続的に形成される。複数の画素回路の各々は、それぞれ複数のトランジスターを有し、当該トランジスターはNウェル104に共通に形成されるとともに、基板電位を共通である。表示部100におけるNウェル104は導電型の異なるP型半導体基板領域102で囲まれる。

(もっと読む)

炭化珪素半導体装置

【課題】スイッチング素子のソースおよびドレイン間に還流ダイオードが接続された構造を有する炭化珪素半導体装置を一の炭化珪素基板を用いて提供する。

【解決手段】第1層34は第1導電型を有する。第2層35は、第1層34の一部が露出されるように第1層34上に設けられ、第2導電型を有する。第1〜第3不純物領域は、第2層35を貫通して第1層34に達する。第1および第2不純物領域11、12の各々は第1導電型を有する。第3不純物領域13は、第1および第2不純物領域11、12の間に配置され、かつ第2導電型を有する。第1〜第3電極S1、D1、G1は、第1〜第3不純物領域11〜13のそれぞれの上に設けられている。ショットキー電極SKは、第1層34の一部の上に設けられ、第1電極S1に電気的に接続されている。

(もっと読む)

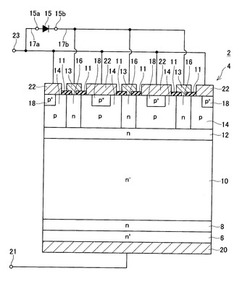

トレンチポリシリコンダイオード

【課題】シリコン内にダイオード構造を位置させた半導体製造方法を提供する。

【解決手段】トレンチポリシリコンダイオードを製造する方法は、N+(P+)型基板上にN−(P−)型エピタキシャル領域を形成すること、エピタキシャル領域内にトレンチを形成すること、さらに、前記トレンチ内に絶縁層を形成し、前記トレンチをポリシリコンで充填する。さらに、P+(N+)型ドーパントをインプラントして、前記トレンチ内に前記ポリシリコンのP+(N+)型領域を、N+(P+)型ドーパントをインプラントして、前記トレンチ内に前記ポリシリコンのN+(P+)型領域を形成しトレンチ内にポリシリコンダイオードを形成することを含み、ダイオードの一部は、トレンチの上面より低い。

(もっと読む)

半導体装置およびその製造方法

【課題】素子特性を悪化させず、アクティブ領域を終端領域に対して、簡単な方法により電気的に独立させることができ、さらには素子サイズの小型化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】エピタキシャル層23のアクティブ領域12と終端領域11との間に、エピタキシャル層23の表面24を形成するように、当該表面24に沿って全体にわたって形成されたチャネル層26を、ゲートトレンチ28の深さD1と同じ深さD2を有するアイソレーショントレンチ39で分断する。互いに同じ深さのゲートトレンチ28およびアイソレーショントレンチ39は、同一のエッチング工程で形成される。

(もっと読む)

半導体装置

【課題】消費電力の増加を招くことなくオフの状態を実現することのできる半導体装置を

提供する。

【解決手段】ゲートに電圧が印加されていない状態でオン状態であるパワー素子と、パワ

ー素子のゲートに第1の電圧を印加するためのスイッチング用の電界効果トランジスタと

、パワー素子のゲートに第1の電圧より低い電圧を印加するためのスイッチング用の電界

効果トランジスタと、を有し、上記スイッチング用の電界効果トランジスタはオフ電流が

小さい半導体装置である。

(もっと読む)

組合せ出力バッファおよびESDダイオードデバイス

【課題】改良されたESD保護デバイスおよび該動作方法が、必要とされる。

【解決手段】集積回路ESD保護回路270は、ゲートダイオード271および出力バッファMOSFET272を含有する組合せデバイスとともに形成される。第1導電性タイプのボディタイフィンガ307は、基板301、302に形成され、複数のダイオードポリフィンガ231、232を用いて第2導電性タイプ310のドレイン領域から分離される。複数のダイオードポリフィンガ231、232は、出力バッファMOSFET272を形成する複数のポリゲートフィンガ204、205と交互配置される。

(もっと読む)

半導体装置

【課題】回路誤動作を防止できる半導体装置を提供する。

【解決手段】低電位基準回路部LVおよび高電位基準回路部HVを構成する絶縁分離された半導体素子の外周に、n型ガードリング42c等を形成する。また、活性層2cにて構成されるn-型層42a等の中にp型ウェル42d等を形成し、このp型ウェル42d内に半導体素子を形成する。また、外部電源61に接続されるラインを電源供給ラインとガードリング端子固定ラインとを分岐し、電源供給ラインの電流が流れないガードリング端子固定ラインに抵抗63を備えることで、バイパスコンデンサ64をディスクリート部品としなくても良い回路構成とする。

(もっと読む)

半導体装置

【課題】異なる電源系統を含む半導体装置において、静電気による破壊から出力回路を保護する保護素子を備えた半導体装置の提供。

【解決手段】半導体装置は、第1の電源電圧と第1の接地電圧からなる第1の電源系統と、第2の電源電圧と第2の接地電圧からなる第2の電源系統と、第2の電源系統から電源供給を受ける出力回路と、第1の電源系統から電源供給を受け、出力回路を駆動する信号を出力する第1の駆動回路と、第1の接地電圧と第2の接地電圧との間に接続された第1の保護回路と、一端が、出力回路の出力ノードに接続され、他の一端が、第1の接地電圧に接続されている第1の保護素子と、を備えている。

(もっと読む)

61 - 80 / 1,648

[ Back to top ]