Fターム[5F048BC06]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ソース・ドレイン (8,322) | 追加領域の形成 (3,324) | LDD (2,469)

Fターム[5F048BC06]に分類される特許

361 - 380 / 2,469

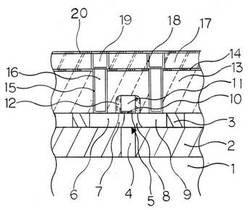

半導体装置及びその製造方法

【課題】貼り合わせSOI基板を使用せずに、容易なプロセスにより、高速なMIS電界効果トランジスタを提供する。

【解決手段】p型のSi基板1上に、一部に空孔4を有するシリコン酸化膜2が設けられ、空孔4を挟んでシリコン酸化膜2上に延在したp型のSOIC基板(Si)5が設けられ、シリコン窒化膜3により素子分離されている。空孔4に自己整合して、SOIC基板5上にゲート酸化膜10を介してゲート電極11が設けられ、ゲート電極11の側壁にサイドウォール12が設けられ、SOIC基板5には、ゲート電極11に自己整合してn型ソースドレイン領域(7、8)及びサイドウォール12に自己整合してn型ソースドレイン領域(6、9)が設けられ、n型ソースドレイン領域には、バリアメタル15を有する導電プラグ16を介してバリアメタル18を有するCu配線19が接続されている構造からなるNチャネルのMIS電界効果トランジスタ。

(もっと読む)

MISFET及びその製造方法

【課題】 LDD領域の長さを精度良く調整可能で、高周波動作に適用できる非対称な横方向二重拡散型MISFETを提供する。

【解決手段】 第1導電型のウェル1の上方にゲート絶縁膜3を介してゲート電極5を形成する工程、ウェル1に第2導電型の不純物イオン注入によりドレイン領域7を形成する工程、ウェル1の上方にゲート電極5が形成されるゲート電極領域とドレイン領域7を少なくとも覆い、ゲート電極領域とドレイン領域の間が開口したマスクパターン層を形成する工程、マスクパターン層をマスクとして自己整合的に、マスクパターン層で覆われていない領域に第2導電型の不純物イオン注入によりドレイン領域より低濃度のLDD拡散領域6を形成する工程、及び、ウェル1のゲート電極5を挟んでドレイン領域7の反対側の領域に第2導電型の不純物イオン注入によりLDD拡散領域より高濃度のソース領域を形成する工程を有する。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法の一部は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法の一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。様々な効果を達成するようDDCを構成する手法が数多く存在し得るとともに、ここに提示される更なる構造及び方法は、更なる利益を生み出すように単独あるいはDDCとともに使用され得る。  (もっと読む)

(もっと読む)

半導体素子の製造方法

【課題】ピッティング不良が抑制され、簡単な工程を通じて形成することができる高性能の半導体素子の製造方法を提供する。

【解決手段】半導体基板にゲート電極を形成する段階と、ゲート電極に側壁スペーサを形成する段階と、側壁スペーサの両側の半導体基板を一部エッチングしてトレンチを形成する段階と、トレンチ内にSiGe混晶層を形成する段階と、SiGe混晶層上にシリコン層を形成する段階と、シリコン層の面の結晶方向に従って、エッチング率が異なるエッチング液を利用してシリコン層の一部をエッチチングすることによって111傾斜面を有するシリコンファセット(Si facet)を含むキャッピング層を形成する段階と、を有する。キャッピング層を含むことによって半導体素子でホールの移動度が高まる。キャッピング層内のピッティング不良が減少することによって半導体素子の特性が良好になる。

(もっと読む)

半導体装置、半導体装置の製造方法、および、リソグラフィマスクの製造方法

【課題】リソグラフィを用いて形成される半導体装置を高性能化させる。

【解決手段】互いに同じ材質からなる第1導体パターンPE1および第1ダミー導体パターンDM1を含む第1の層L1と、第2導体パターンPE2を含む第2の層L2とがシリコン基板SUB1上に積層されている。第2導体パターンPE2は、第1導体パターンPE1または第1の層L1より下層の導電部と、コンタクトプラグCP1によって電気的に接続されている。第1ダミー導体パターンDM1のうち、コンタクトプラグCP1と重なる部分には、それよりも断面積の大きい孔部HL1が形成されている。そして、コンタクトプラグCP1は孔部HL1内を通って配置されることで、第1ダミー導体パターンDM1と接触しないようにして形成されている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】1メモリセルが6トランジスタを有するSRAMにおいて、コンタクトの微細化をするとリークの発生を回避できる半導体記憶装置及びその製造方法を提供する。

【解決手段】1メモリセルが第1及び第2ドライバトランジスタ(DTr1、DTr2)、第1及び第2転送トランジスタ(TTr1,TTr2)並びに第1及び第2ロードトランジスタ(LTR1,LTr2)の6トランジスタを有するSRAMにおいて第1ドライバトランジスタと第2ドライバトランジスタのソースドレイン領域に基準電位を印加するための接地コンタクトCgと、第1ロードトランジスタと第2ロードトランジスタのソースドレイン領域に電源電位を印加するための電源電位コンタクトCcの径が、共通コンタクトCsを除く他のコンタクト(Cb,Cn,Cw)の径より大きく形成された構成とする。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域に応力を印加しつつ、基板やソース/ドレイン領域においてリーク電流の発生が効果的に抑制された半導体装置を提供する。

【解決手段】半導体装置は、第1導電型の不純物を含み、素子形成領域170を有する半導体基板101と、素子形成領域170上にゲート絶縁膜132を挟んで形成されたゲート電極125と、ゲート電極125の両側方に形成され、第2導電型の不純物を含むソース/ドレイン領域150とを備える。素子形成領域170のうちゲート電極の両側方に位置する領域には、半導体基板101の主面に対して傾いた半導体単結晶のファセット面を露出させる側壁を有し、コーナー部が丸められたリセス130が形成されており、ソース/ドレイン領域150は、リセス130に埋め込まれたシリコン混晶で構成されている。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法の一部は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法の一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

状態密度が設計された電界効果トランジスタ

【課題】nチャネルおよびp型チャネルトランジスタに用いられる層構造を提供する。

【解決手段】nチャネルトランジスタを製作するのに用いる層構造を含む。層構造は、伝導帯底EC1を有する第1の半導体層、離散正孔準位H0を有する第2の半導体層、第1と第2の半導体層との間に配置された広バンドギャップ半導体バリア層、第1の半導体層の上方に配置されたゲート誘電体層、およびゲート誘電体層の上方に配置されたゲート金属層を含み、離散正孔準位H0は、伝導帯底EC1の下方に位置され、ゲート金属層にゼロバイアスが供給される。

(もっと読む)

半導体装置及びその製造方法

【課題】MISトランジスタに適当なしきい値電圧が与えられる一方、抵抗素子はシリコン膜からなる抵抗体層の異常成長を抑制して、シリコン膜の膜厚を安定化する。

【解決手段】半導体装置は、半導体基板10の上部に形成された素子分離領域12によって囲まれた第1の活性領域10a、第1の活性領域の上に形成された第1の高誘電体膜14aを有する第1のゲート絶縁膜27a、及び第1のゲート絶縁膜の上に形成された第1のゲート電極28aとを有する第1導電型の第1のMISトランジスタ1aと、素子分離領域の上に形成された第2の高誘電体膜14x、及び該第2の高誘電体膜の上に形成されたシリコンからなる抵抗体層20xを有する抵抗素子1xとを備えている。第1の高誘電体膜と第2の高誘電体膜とは、互いに同一の高誘電体材料からなり、第1の高誘電体膜は第1の調整用金属を含み、第2の高誘電体膜は第1の調整用金属を含まない。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率ゲート絶縁膜、及び、ゲート電極としてメタル膜を含む半導体装置において、逆短チャネル効果の発生を防止して高性能化を実現する。

【課題手段】半導体装置は、半導体基板101の上に形成されたランタンを含有する高誘電率ゲート絶縁膜102と、高誘電率ゲート絶縁膜102の上に形成されたキャップ膜103と、キャップ膜103の上に形成されたメタル膜104と、メタル膜104の上に形成されたポリシリコン膜105と、高誘電率ゲート絶縁膜102、キャップ膜103、メタル膜104、及びポリシリコン膜105それぞれの両側面に形成されたランタンを含有するゲート側壁絶縁膜106とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】第1のMISトランジスタの閾値電圧が高くなることを防止する。

【解決手段】半導体装置は、第1,第2のMISトランジスタTr1,Tr2を備えている。第1,第2のMISトランジスタは、第1,第2の活性領域10a,10b上に形成され、第1,第2の高誘電率膜13a,13bを有する第1,第2のゲート絶縁膜13A,14Bと、第1,第2のゲート絶縁膜上に形成された第1,第2のゲート電極18A,18Bとを備えている。第1のゲート絶縁膜13Aと第2のゲート絶縁膜14Bとは、第1の素子分離領域11L上において分離されている。第1の素子分離領域11Lを挟んで対向する第1の活性領域10aの一端と第2の活性領域10bの一端との距離をsとし、第1の活性領域10aの一端から第1の素子分離領域11L上に位置する第1のゲート絶縁膜13Aの一端までの突き出し量をd1としたとき、d1<0.5sの関係式が成り立っている。

(もっと読む)

半導体装置の製造方法

【課題】 置換ゲート工程で発生する不良を防止できる半導体装置の製造方法を提供する。

【解決手段】本発明による半導体装置の製造方法は、半導体基板上にゲート絶縁膜および犠牲ゲート電極を含むゲートパターンを形成する段階、前記半導体基板および前記ゲートパターン上にエッチング停止層および絶縁層を形成する段階、前記エッチング停止層が露出するまで前記絶縁層を除去する段階、前記犠牲ゲート電極が露出するまで前記エッチング停止層をエッチバックする段階、前記犠牲ゲート電極を除去し、結果物の全体構造の上面に金属層を形成する段階、前記絶縁層が露出するまで前記金属層を除去する段階、および前記金属層を所定の深さでエッチバックする段階を含む。

(もっと読む)

半導体集積回路装置の製造方法

【課題】低抵抗で、かつ接合リーク電流の少ないCoシリサイド層を形成することのできるサリサイドプロセスを提供する。

【解決手段】Co純度が99.99%以上で、FeおよびNiの含有量が10ppm以下、より好ましくはCo純度が99.999%の高純度Coターゲットを用いたスパッタリング法によってウエハの主面上に堆積したCo膜をシリサイド化することにより、MOSFETのゲート電極(8n、8p)、ソース、ドレイン(p+型半導体領域13、n+型半導体領域14)の表面に低抵抗で接合リーク電流の少ないCoSi2層(16b)を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】MISトランジスタにおけるシリコン混晶層からなるソースドレイン領域を、不純物の拡散による不具合を防止しながらチャネル領域に近づけることができるようにする。

【解決手段】半導体装置は、半導体基板10からなるn型の活性領域の上に、ゲート絶縁膜12を介在させて形成されたゲート電極13と、活性領域におけるゲート電極13の両側方の領域に形成されたp型ソースドレイン領域20と、活性領域における各p型ソースドレイン領域20の側面からそれぞれゲート電極13の下側に向かって形成されたn型ポケット領域18とを有している。p型ソースドレイン領域20は、シリコンとIV族元素との混晶層からなり、混晶層は、ゲート長方向におけるゲート電極側の側面がゲート電極側に突き出す凸部20aを有している。凸部20aの先端は、ポケット領域18によって覆われている。

(もっと読む)

二種類の仕事関数メタルを備える半導体装置

【課題】高誘電率ゲート絶縁膜を備える半導体装置の閾値電圧を適切に制御すること。

【解決手段】半導体装置の形成方法は、仕事関数メタルを含むダミーメタルゲート層をベース絶縁膜の直上に形成することと、アニーリングによって仕事関数メタルをベース絶縁膜中に拡散させることと、ウェットエッチングによってダミーメタルゲート層を除去することと、ベース絶縁膜211、212上に高誘電率ゲート絶縁膜213、213を形成することと、高誘電率ゲート絶縁膜213上にメタルゲート214、215を形成することと、を含む。

(もっと読む)

トレンチ型絶縁ゲート半導体装置及びその製造方法

【課題】トレンチ型絶縁ゲート半導体素子と多結晶シリコンダイオードを同一チップ上に形成して性能を高める。

【解決手段】本発明では、半導体基板上の半導体層の主面に形成されたトレンチ型絶縁ゲート半導体素子のトレンチ溝の外側には、トレンチ溝に連なる多結晶シリコン層を形成する。また、トレンチ溝の外側には、前記トレンチ溝に連なる多結晶シリコン層とは別の多結晶シリコン層が形成され、この多結晶シリコン層には多結晶シリコンダイオードが形成され、そして、この多結晶シリコンダイオードが形成された多結晶シリコン層の膜厚が、前記トレンチ溝に連なる多結晶シリコン層の膜厚よりも薄くなるように形成することを特徴とする。

(もっと読む)

半導体装置

【課題】SRAM回路の動作速度を向上させる。

【解決手段】駆動MISFETと転送MISFETとそれらの上部に形成された縦型MISFETとでメモリセルを構成したSRAMにおいて、周辺回路を構成するMISFET間の電気的接続を、メモリセルの縦型MISFET(SV1、SV2)よりも下部に形成されるプラグ28および中間導電層46、47で行うとともに、縦型MISFET(SV1、SV2)よりも上部に形成されるプラグ、第1および第2金属配線層を用いて行うことにより、配線の自由度を向上でき、高集積化できる。また、MISFET間の接続抵抗を低減でき、回路の動作スピードを向上できる。

(もっと読む)

半導体装置の製造方法

【課題】NMOSトランジスタおよびPMOSトランジスタを有する半導体装置において、ショートチャネル効果を抑制するとともに、ゲート−ドレイン間での電流リークを低減し、また、ゲートオーバーラップに起因する寄生容量を低減して、回路動作速度の低下を低減した半導体装置を提供する。

【解決手段】低電圧NMOS領域LNRにおけるシリコン基板1の表面内に、N型不純物、例えばヒ素をイオン注入により比較的低濃度に導入して、エクステンション層61を形成する。そして、シリコン基板1の全面を覆うように、シリコン酸化膜OX2を形成し、ゲート電極51〜54の側面においてはシリコン酸化膜OX2をオフセットサイドウォールとして使用し、低電圧PMOS領域LPRにおけるシリコン基板1の表面内に、ボロンをイオン注入により比較的低濃度に導入して、エクステンション層62となるP型不純物層621を形成する。

(もっと読む)

半導体素子及びその製造方法、並びに固体撮像装置

【課題】工数の増加を招くことなく、更には、特性劣化を抑止して高品質の製品を供給することができる半導体素子の製造方法を提供する。

【解決手段】画素2に形成されたトランジスタのゲート電極305〜307の周辺にイオン注入を行うことでソース領域及びドレイン領域として機能するn+領域426、427を形成し、その後に、ブロック膜として機能する第1の絶縁膜35及び第2の絶縁膜36を成膜し、エッチバックによって第1の絶縁膜35及び第2の絶縁膜36をその一部としたゲート電極のサイドウォールを形成する。

(もっと読む)

361 - 380 / 2,469

[ Back to top ]