Fターム[5F048BC06]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ソース・ドレイン (8,322) | 追加領域の形成 (3,324) | LDD (2,469)

Fターム[5F048BC06]に分類される特許

301 - 320 / 2,469

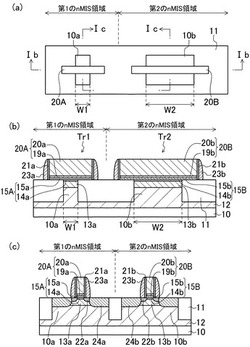

半導体装置及びその製造方法

【課題】ゲート幅が互いに異なる第1,第2のMISトランジスタを備えた半導体装置において、第1,第2のMISトランジスタの閾値電圧を、所望の閾値電圧に制御する。

【解決手段】半導体装置は、第1,第2のMISトランジスタを備えた半導体装置である。第1のMISトランジスタは、第1の高誘電率絶縁膜15aを有する第1のゲート絶縁膜15Aと、第1のゲート電極20Aとを備えている。第2のMISトランジスタは、第2の高誘電率絶縁膜15bを有する第2のゲート絶縁膜15Bと、第2のゲート電極20Bとを備えている。第1,第2のゲート絶縁膜は、調整用金属を含む。第1のMISトランジスタの第1のゲート幅W1は、第2のMISトランジスタの第2のゲート幅W2よりも小さい。第1のゲート絶縁膜中における調整用金属の平均調整用金属濃度は、第2のゲート絶縁膜中における調整用金属の平均調整用金属濃度に比べて低い。

(もっと読む)

スタンダードセル、スタンダードセルを備えた半導体装置、およびスタンダードセルの配置配線方法

【課題】複数のスタンダードセルを有する半導体装置のチップ面積をさらに小さくする。

【解決手段】半導体装置SD1は第1および第2スタンダードセルSC1,SC2を備える。第1スタンダードセルSC1は、拡散領域An11、拡散領域An11に対向する機能素子領域FE1、および金属層MT11を有する。第2スタンダードセルSC2は、拡散領域An11に連続する拡散領域An21、拡散領域An21に対向する機能素子領域FE2、ならびに拡散領域An21および機能素子領域FE2の間に形成された拡散領域CR21を有する。金属層MT11および機能素子領域FE2は、拡散領域An11、拡散領域An21、および拡散領域CR21通して電気的に接続される。

(もっと読む)

半導体装置の製造方法

【課題】キャップ材料を使用した半導体装置のウェハ面内における閾値電圧Vtのバラツキを抑制することを目的とする。

【解決手段】まず、半導体基板1001の上に、高誘電率ゲート絶縁膜1006及び第1のキャップ膜1008を順に形成する。次に、熱処理を行って、第1のキャップ膜1008中の第1の金属を高誘電体膜1006に拡散させる。その後、高誘電体膜1006に拡散せずに高誘電体膜1006の上に残存した第1のキャップ膜1008を除去して、第1の金属が拡散した高誘電率ゲート絶縁膜1006Aの上に金属電極1010を形成する。

(もっと読む)

半導体装置及びそのレイアウト作成方法

【課題】半導体装置及びその製造方法において、ゲート電極部の幅及びゲート電極部からの突き出し長のばらつきを低減する。

【解決手段】半導体装置は、ゲート電極部及び突き出し部を有する実パターン431と、実パターン431に並んで配置されるダミーパターン433とを含む複数のラインパターンを備える。2つのダミーパターン433と、これらに挟まれ且つ実パターン432を含むラインパターンとにより、同一間隔を空けて並走するラインパターン並走部が構成される。ラインパターン並走部の各ラインパターンは、同一の幅を有すると共に、互いに実質的に面一なライン終端部414を有する。各ライン終端部414の延長線上に、同一の終端部間距離403を空けて、ライン終端部均一化ダミーパターン420が形成される。ライン終端部均一化ダミーパターン420は、ラインパターンと同一幅で且つ同一間隔に形成された複数のライン状のパターンを含む。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の向上に寄与し得る半導体装置の製造方法を提供する。

【解決手段】半導体基板10にトランジスタ36を形成する工程と、半導体基板上に、トランジスタを覆う第1のシリコン窒化膜38を形成する工程と、第1のシリコン窒化膜にNH4Fラジカルを供給する工程と、NH4Fラジカルを供給する工程の後、第1のシリコン窒化膜に対して熱処理を行う工程と、熱処理を行う工程の後、第1のシリコン窒化膜上に第2のシリコン窒化膜を形成する工程とを有している。

(もっと読む)

半導体装置およびその製造方法

【課題】高耐圧MISFETを含む半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】高耐圧MISFETQ4のゲート絶縁膜GOX4を、酸化シリコン膜と窒化シリコン膜という異なる種類の膜から形成する。具体的に、高耐圧MISFETQ4では、ゲート絶縁膜GOX4を、酸化シリコン膜PREOX1と、この酸化シリコン膜PREOX1上に形成された酸化シリコン膜OX1と、酸化シリコン膜OX1上に形成された窒化シリコン膜SN1と、窒化シリコン膜SN1上に形成された酸化シリコン膜OX2から形成している。

(もっと読む)

半導体基板の再生方法、再生半導体基板の作製方法、及びSOI基板の作製方法

【課題】半導体基板の再生に適した方法、半導体基板の再生に適した方法を用いた再生半導体基板の作製方法、及び当該再生半導体基板を用いたSOI基板の作製方法の提供を目的とする。

【解決手段】損傷した半導体領域と絶縁層とを含む凸部が周縁部に存在する半導体基板に対し、絶縁層が除去されるエッチング処理と、半導体基板を構成する半導体材料を酸化する物質、酸化された半導体材料を溶解する物質、及び、半導体材料の酸化の速度及び酸化された半導体材料の溶解の速度を制御する物質、を含む混合液を用いて、未損傷の半導体領域に対して損傷半導体領域が優先的に除去されるエッチング処理と、レーザ光照射工程と、を行うことで半導体基板を再生する。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】多層配線構造を使って、キャパシタンスが大きく、かつキャパシタンス値が安定なキャパシタ素子を半導体基板上に集積化する。

【解決手段】多層配線構造18は、少なくとも第1層目の層間絶縁膜16と、第1層目の層間絶縁膜中に埋設された第1配線層と、を含み、第1配線層は、第1の電源に接続され前記第1の層間絶縁膜中に埋設された第1の配線パタ―ン15C1と、第2の電源に接続され前記第1の層間絶縁膜中に埋設された第2の配線パタ―ン15C2と、を含み、第1の配線パタ―ンと前記第2の配線パタ―ンとは容量結合して第1のキャパシタを形成し、第1の配線パタ―ンは積層配線パタ―ン13C上に形成されて、前記第4の電極パターン13Gと容量結合して第2のキャパシタを形成し、第4の電極パターンは第2の配線パタ―ンに電気的に接続されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】シリコン抵抗とメモリ回路とを混載した半導体装置において、メモリの情報の保持時間を長くして、かつ書込・読出時間を短くする。

【解決手段】容量素子400はメモリセルを構成しており、第1トランジスタ200は、ソース及びドレインとなる第1拡散層226が容量素子400に接続している。シリコン抵抗素子300はシリコン層からなる。第1拡散層226はシリサイド層を有していない。また第1ゲート電極230は、金属層232及びシリコン層234を積層した積層構造を有している。そして第1ゲート電極230は、素子分離膜50上に位置する領域の少なくとも一部にシリサイド層235を有しており、かつ第1拡散層226に挟まれた領域にはシリサイド層を有していない。そしてコンタクト513は、シリサイド層235を介して第1ゲート電極230に接続している。

(もっと読む)

半導体基板の作製方法及び半導体装置の作製方法

【課題】平坦性の高い表面を有する単結晶半導体層を備えた半導体基板の作製方法を提供することを目的の一とする。平坦性の高い単結晶半導体層を備えた半導体基板を用いて信頼性の高い半導体装置を作製することを目的の一とする。

【解決手段】半導体基板の作製工程において、単結晶半導体基板に希ガスイオン照射工程、レーザー照射工程および水素イオン照射工程を行うことで、単結晶半導体基板の所定の深さに大きな結晶欠陥を含有した薄い脆化領域を形成し、剥離加熱工程を行うことで脆化領域より表面側の単結晶半導体層をベース基板に転載する。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI構造の縦型のMISFETの提供

【解決手段】Si基板1上に、一部に空孔4を有する絶縁膜2が設けられ、空孔4上及び絶縁膜2の一部上に横方向半導体層6が設けられ、半導体層6の側面の一部に導電膜3が接して設けられ、絶縁膜2により素子分離されている。半導体層6上の、空孔4直上部に縦方向半導体層7が設けられ、半導体層7の上部にドレイン領域(10,9)が設けられ、離間し、相対して下部にソース領域8が設けられ、ソース領域8は延在して、半導体層6全体に設けられている。半導体層7の全側面には、ゲート酸化膜11を介してゲート電極12が設けられ、ドレイン領域10、ゲート電極11及び導電膜3を介したソース領域8には、バリアメタル18を有する導電プラグ19を介してバリアメタル21を有する配線22が接続されている縦型のMISFET。

(もっと読む)

半導体装置及びその製造方法

【課題】良好な電気的特性を有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上に形成されたゲート絶縁膜20と、ゲート絶縁膜上に形成されたキャップ膜22と、キャップ膜上に形成されたシリコン酸化膜23と、シリコン酸化膜上に形成された金属ゲート電極24と、金属ゲート電極の両側の半導体基板内に形成されたソース/ドレイン拡散層48とを有している。

(もっと読む)

半導体装置及び電子機器

【課題】逆スタガ型TFTにおいて、薄膜の応力を用いてしきい値電圧を制御する。

【解決手段】基板上に形成された電極上に設けられた第1の絶縁層の応力と膜厚の積と、前記第1の絶縁層上に設けられた引張り応力を有する結晶質半導体膜からなる活性層の応力と膜厚の積と、前記活性層上に設けられた第2の絶縁層の応力と膜厚の積を適当な大きさに設定することでしきい値電圧を制御する。

(もっと読む)

半導体装置の製造方法

【課題】NMOSFETにSiGe層が成長されることを抑制し、かつPMOSFETのSiGe層の形状不良の発生を抑止する。

【解決手段】半導体装置の製造方法は、半導体基板の第1領域に第1ゲート電極6Aを形成し、前記半導体基板の第2領域に第2ゲート電極6Bを形成し、前記第1ゲート電極の側壁に第1サイドウォール12Aを形成し、前記第2ゲート電極の側壁に第2サイドウォール12Bを形成し、前記半導体基板、前記第1ゲート電極、前記第2ゲート電極、前記第1サイドウォール及び前記第2サイドウォールを覆うように酸化膜20を形成し、前記酸化膜上に、前記第1領域を覆うようにレジストを形成し、前記レジストをマスクとして前記酸化膜20をエッチングすることにより、前記第2領域の前記酸化膜20を除去し、前記レジストを除去し、前記半導体基板及び前記第1領域の前記酸化膜20に対して、塩素を含むガスを用いてプラズマ処理を行う。

(もっと読む)

半導体装置の設計方法及び製造方法

【課題】トランジスタ等の電気的特性のばらつきを低減し得る半導体装置の設計方法及び半導体装置の製造方法を提供する。

【解決手段】素子領域の実パターンである複数の第1の実パターンと、ゲート配線の実パターンである複数の第2の実パターンとを配置するステップと、レイアウト領域を複数の分割領域に分割するステップと、レイアウト領域内に、ダミーの素子領域のパターンである複数の第1のダミーパターンと、ダミーのゲート配線のパターンである複数の第2のダミーパターンとを配置するステップであって、分割領域内における第1の実パターン、第2の実パターン、第1のダミーパターン及び第2のダミーパターンの周囲長の総和の、分割領域間におけるばらつきが、所定の範囲内となるように、第1のダミーパターン及び第2のダミーパターンを配置する。

(もっと読む)

電気光学装置及び電子機器、並びに電気光学装置の製造方法

【課題】液晶装置等の電気光学装置において、TFTで発生する光リーク電流を低減させ

る。

【解決手段】電気光学装置は、表示領域(10a)に設けられた複数の画素電極(9a)

と、画素電極に画像信号を供給するデータ線(6a)と、画素電極に電気的に接続された

画素電極側ソースドレイン領域(1e)、データ線に電気的に接続されたデータ線側ソー

スドレイン領域(1d)、並びに画素電極側ソースドレイン領域及びデータ線側ソースド

レイン領域間に位置するチャネル領域(1a’)を有する半導体層(1a)と、半導体層

のチャネル領域にゲート絶縁膜(2a,2b)を介して対向配置されたゲート電極(3b

)とを備える。半導体層は、チャネル領域の膜厚が、画素電極側ソースドレイン領域及び

データ線側ソースドレイン領域の膜厚より薄くなるように形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】静電保護素子である保護トランジスタのサイズを縮小することができ、ゲート端子の抵抗成分を同程度に抑え、時定数を増加させることなく、保護トランジスタの回路動作スピードの低下を防ぐことができるとともに、電荷集中を緩和し、静電破壊耐量を向上させることができる。

【解決手段】本発明に係る半導体装置は、ソース・ドレイン領域と、ソース・ドレイン領域の上方に形成されたゲート電極と、ゲート電極の側面に形成されたサイドウォールと、ソース・ドレイン領域の上面に、サイドウォールから所定の距離だけ離間して形成された第1のシリサイド膜と、ゲート電極の上面に、サイドウォールから所定の距離だけ離間して形成された第2のシリサイド膜とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】サリサイドプロセスで金属シリサイド層を形成した半導体装置の性能を向上させる。

【解決手段】ゲート電極GEと上部に金属シリサイド層11bが形成されたソース・ドレイン領域とを有するMISFETが半導体基板1の主面に複数形成されている。金属シリサイド層11bは、Pt,Pd,V,Er,Ybからなる群から選択された少なくとも一種からなる第1金属元素およびニッケルのシリサイドからなる。半導体基板1の主面に形成された複数のMISFETのソース・ドレイン領域のうち、ゲート長方向に最も近接して隣り合うゲート電極GE間に配置されたソース・ドレイン領域のゲート長方向の幅W1cよりも、金属シリサイド層11bの粒径が小さい。

(もっと読む)

半導体装置

【課題】半導体装置の性能を向上させる。また、半導体装置の信頼性を確保する。また、半導体装置のチップサイズの縮小を図る。特に、SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を損なわずにゲート電極の下部のウエルの電位を制御し、寄生容量の発生を防ぐ。また、MOSFETにおける欠陥の発生を防ぐ。

【解決手段】ゲート電極配線3に形成された孔部27内を通るウエルコンタクトプラグ8により、ゲート電極2の下部のウエルの電位を制御することで寄生容量の発生を防ぐ。また、ゲート電極2に沿って素子分離領域4を延在させることで、ゲッタリング効果によりゲート絶縁膜における欠陥の発生を防ぐ。

(もっと読む)

半導体装置の製造方法

【課題】デュアルゲート構造を有する半導体装置の製造技術において、MISFETのしきい値電圧の上昇を抑制することができる製造技術を提供する。

【解決手段】ポリシリコン膜PF1上にレジスト膜FR2を形成する。そして、レジスト膜FR2に対して露光・現像処理を施すことにより、レジスト膜FR2をパターニングする。その後、パターニングしたレジスト膜FR2をマスクにしたイオン注入法により、露出しているnチャネル型MISFET形成領域NTRのポリシリコン膜PF1にアルゴン(Ar+)を導入する。このアルゴン注入工程により、nチャネル型MISFET形成領域NTRのポリシリコン膜PF1はアモルファス化する。

(もっと読む)

301 - 320 / 2,469

[ Back to top ]