Fターム[5F048BC06]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ソース・ドレイン (8,322) | 追加領域の形成 (3,324) | LDD (2,469)

Fターム[5F048BC06]に分類される特許

261 - 280 / 2,469

半導体装置及びその製造方法

【課題】ストレッサ膜を有する半導体装置及びその製造方法に関し、ストレッサ膜からの応力を効率よくチャネル領域に印加してMISFETの電流駆動能力を向上しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に、素子領域を画定する素子分離絶縁膜を形成し、素子領域上に、ゲート絶縁膜を介してゲート電極を形成し、ゲート電極の両側の半導体基板内にソース/ドレイン領域を形成し、ゲート電極及びソース/ドレイン領域が形成された半導体基板上に第1の絶縁膜を形成し、素子分離絶縁膜の端部に生じた窪み内に第1の絶縁膜が残存するように第1の絶縁膜をエッチバックし、半導体基板上に、半導体基板の表面に平行な方向に応力を印加する第2の絶縁膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】容易なプロセスにより単結晶半導体層を形成したSOI構造のMISFETの提供

【解決手段】半導体基板1上に、第1の絶縁膜2を介して、一部に空孔4を有する第2の絶縁膜3が設けられ、空孔4上及び第2の絶縁膜3の一部上に島状に絶縁分離された半導体層6が設けられ、半導体層6上にゲート酸化膜12を介して、空孔4直上に空孔4の幅以下のゲート電極13が設けられ、半導体層6には、ゲート電極13に自己整合して低濃度のソースドレイン領域(9,10)が、ゲート電極13の側壁に設けられたサイドウォール14に自己整合して高濃度のソースドレイン領域(8,11)がそれぞれ設けられ、ゲート電極13(配線図示せず)及び高濃度のソースドレイン領域(8,11)にはバリアメタル17を有する導電プラグ18を介してバリアメタル20を有する配線21が接続されているMISFET。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル形成領域に印加する応力の組み合わせを調整して従来例よりもキャリア移動度を向上させる半導体装置を提供する。

【解決手段】チャネル形成領域を有する半導体基板10上にゲート絶縁膜20が形成され、ゲート絶縁膜20の上層にゲート電極21が形成され、ゲート電極21の上層にチャネル形成領域に応力を印加する第1応力導入層22が形成されており、ゲート電極21及び第1応力導入層22の両側部における半導体基板10の表層部にソースドレイン領域13が形成されており、少なくとも第1応力導入層22の領域を除き、ソースドレイン領域13の上層に、チャネル形成領域に第1応力導入層22と異なる応力を印加する第2応力導入層26が形成されている構成とする。

(もっと読む)

半導体装置の製造方法、及び、半導体装置

【課題】CMOS回路の閾値を簡易なプロセスで効率よく制御して、信頼性の高い半導体装置を作製する。

【解決手段】下地ゲート絶縁膜を形成し、下地ゲート絶縁膜上に選択的にマスク膜を形成し、下地ゲート絶縁膜、及び、マスク膜上に第1の金属元素を含む第1のキャップ膜を形成し、nMOSトランジスタ領域の下地ゲート絶縁膜に第1の金属元素を拡散させ、マスク膜、及び、第1のキャップ膜を選択的に除去し、第1の金属元素が拡散したnMOSトランジスタ領域の下地ゲート絶縁膜、及び、pMOSトランジスタ領域の下地ゲート絶縁膜上に第2の金属元素を含む第2のキャップ膜を形成し、下地ゲート絶縁膜に第2の金属元素を拡散させる。

(もっと読む)

半導体装置の製造方法

【課題】信頼性に優れた半導体装置が得られる製造方法を提供する。

【解決手段】半導体装置の製造方法は、p型電界効果トランジスタおよびn型電界効果トランジスタを備える半導体装置の製造方法であって、基板上に、界面絶縁層および高誘電率層をこの順で形成する工程と、高誘電率層上に、犠牲層のパターンを形成する工程と、犠牲層が形成されている第1の領域の高誘電率層上および犠牲層が形成されていない第2の領域の高誘電率層上に、金属元素を含む金属含有膜を形成する工程と、熱処理を行うことにより、第2の領域における界面絶縁層と高誘電率層との界面に金属元素を導入する工程と、犠牲層をウエットエッチングにより除去する工程と、を含み、除去する工程において、犠牲層は、高誘電率層よりもエッチングされやすい。

(もっと読む)

高電圧動作電界効果トランジスタとそのバイアス回路およびその高電圧動作回路要素

【課題】 ICまたはLSIの標準電源電圧用のトランジスタ構成部分ないしはプロセス技術を活用して高電圧動作電界効果トランジスタを該IC中に作りこむ。

【解決手段】 電界効果トランジスタの動作電圧を大きくするために、ゲートにドレイン電位に応じて変化する電位分布を設ける手段をとる。

(もっと読む)

半導体装置

【課題】プロセスばらつきに起因する電気的特性のばらつきが小さい半導体装置を提供する。

【解決手段】半導体基板の上面に形成された第1及び第2のトランジスタ11,12と、を備える。第1及び第2のトランジスタは、それぞれ、半導体基板上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられたゲート電極17と、半導体基板と前記ゲート電極との間に設けられた、半導体基板の上層部分におけるゲート電極の直下域を挟む領域に設けられた第2導電形のソース領域21及びドレイン領域22と、上層部分におけるゲート電極の直下域のうち、ソース領域側の領域に形成され、第1導電形であり、実効的な不純物濃度が上層部分の実効的な不純物濃度よりも高い高濃度チャネル領域を有し、第1と第2トランジスタのソース領域からドレイン領域に向かう方向が同じ向きである。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】素子分離領域13は、溝11に埋め込まれた酸化シリコン膜からなり、上部が半導体基板1から突出しており、半導体基板1から突出している部分の素子分離領域13の側壁上に、窒化シリコンまたは酸窒化シリコンからなる側壁絶縁膜SW1が形成されている。MISFETのゲート絶縁膜は、ハフニウムと酸素と低しきい値化用の元素とを主成分として含有するHf含有絶縁膜5からなり、メタルゲート電極であるゲート電極GEは、活性領域14、側壁絶縁膜SW1および素子分離領域13上に延在している。低しきい値化用の元素は、nチャネル型MISFETの場合は希土類またはMgであり、pチャネル型MISFETの場合は、Al、TiまたはTaである。

(もっと読む)

半導体装置及びその製造方法

【課題】High-kゲート絶縁膜を用いたMOSFETにおいて、信頼性劣化、チャネル移動度低下及びEOTの増加を抑制する方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板101上に、シリコン酸化物を含む第1絶縁層104を形成する工程(a)と、第1絶縁層104上に第1金属層105を形成する工程(b)と、第1金属層105上にゲート電極108を形成する工程(c)とを備える。第1絶縁層104及び第1金属層105からゲート絶縁膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜にHK絶縁膜を用いたMIS構造の半導体装置において、HK絶縁膜端部近傍における酸素過剰領域の発生に起因するトランジスタ特性の劣化を防止する。

【解決手段】半導体基板100上にゲート絶縁膜108a、108bを介してゲート電極109a、109bが形成されている。ゲート電極109a、109bの側面上に導電性酸化物からなるサイドウォールスペーサ111a、111bが形成されている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】工程を追加せずに、アライメントマークの形成領域におけるゲート電極膜の残渣を低減する。

【解決手段】半導体装置の製造方法は、アライメントマーク10を有する第1領域R1と、抵抗体40が形成される第2領域R2と、ゲート電極15が形成される第3領域R3と、を主面1aに有する基板の主面1a上に、金属材料を含有するゲート電極膜11を形成する工程を有する。更に、第1及び第2領域R1、R2のゲート電極膜11を等方性エッチングにより除去する工程を有する。更に、ゲート電極膜11を除去した第2領域R2と、第3領域R3と、に導電膜(ポリシリコン膜13)を成膜する工程を有する。更に、導電膜を成膜する工程の後に、基板の主面1a上にフォトレジスト膜を形成し、アライメントマーク10をアライメントに用いて所定のパターンをフォトレジスト膜に転写する工程を有する。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】LSI中の高耐圧MOSFETを含む高耐圧回路は、純粋な内部回路と異なり、外部との関係で動作電圧が高い状態で固定されているため、通常のように、低電圧化による微細化が適用できない。このため、内部回路部の低電圧化に伴って、ますます、チップ内の占有面積を肥大化させる結果となっている。この問題について、本願発明者等が、各種の対策について評価したところによると、CMOSFET回路構成およびデバイス構成との適合性等の問題がネックとなっていることが明らかとなった。

【解決手段】本願発明は、各チャネル表面に波状起伏が設けられたNチャネル型およびPチャネル型MISFETを有する半導体集積回路装置において、Pチャネル型MISFETのチャネル表面に設けられた波状起伏に比べて、Nチャネル型MISFETのチャネル表面に設けられた波状起伏のピッチを狭くしたものである。

(もっと読む)

半導体装置及びその製造方法

【課題】小さいサイズでラッチアップの発生を防止できる半導体装置を提供する。

【解決手段】第1導電型の半導体基板1と、前記半導体基板内に形成された第1導電型の第1ウェル領域4と、前記半導体基板内に形成され、第1ウェル領域と隣り合う領域に配置された第2導電型のエピタキシャル領域2と、前記エピタキシャル領域内下方の領域に形成され、前記エピタキシャル領域よりも不純物濃度が高い第2導電型の埋め込み領域6と、第1ウェル領域と前記エピタキシャル領域及び前記埋め込み領域との境界に形成されたトレンチ8と、第1ウェル領域上に形成され、第2導電型のソース及びドレイン領域を有する第1半導体素子と、前記エピタキシャル領域上に形成され、第1導電型のソース及びドレイン領域を有する第2半導体素子と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域に応力を印加するシリコン混晶層を活性領域に設けた半導体装置において、電流駆動能力の向上とリーク電流の低下と図れるようにする。

【解決手段】半導体装置は、シリコンからなる半導体基板10に形成され、周囲を素子分離領域11により囲まれてなる第2の活性領域10bと、該第2の活性領域10b及び素子分離領域11の上に、ゲート絶縁膜13を介在させて形成されたゲート電極14とを有している。第2の活性領域10bには、ゲート電極14の両側方の領域が掘り込まれてなるリセス領域19cにp型シリコン混晶層21が形成されており、該p型シリコン混晶層21における素子分離領域11と接触する接触位置の上端21bは、第2の活性領域10bの上面におけるゲート絶縁膜13の下側部分よりも低い。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第1のトランジスタのゲート電極と、該ゲート電極に接する第2のトランジスタのソース電極とは、エッチングの選択比がとれる材料を用いて形成される半導体装置を提供する。第1のトランジスタのゲート電極と、第2のトランジスタのソース電極とをエッチングの選択比がとれる材料を用いて形成することで、レイアウトのマージンを低減させることができるため半導体装置の集積度を向上させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】プロセス負荷を軽減するとともに、EOTを十分に低減するための絶縁膜の薄膜化と、バンドエッジ近傍の仕事関数を有するゲート構造とを実現した半導体装置を提供する。

【解決手段】基板101の異なる領域に形成されたp型トランジスタ100a及びn型トランジスタ100bを備える半導体装置100であって、p型トランジスタ100aは、基板101上方に形成された、第1高誘電率材料からなる第1高誘電率膜106aと、第1高誘電率膜106a上方に形成された、全体が金属によりシリサイド化された第1フルシリサイド電極107aとを備え、n型トランジスタ100bは、基板101上方に形成された、第2高誘電率材料が添加された第1高誘電率材料からなる第2高誘電率膜106bと、第2高誘電率膜106b上方に形成された、全体が金属によりシリサイド化された第2フルシリサイド電極107bとを備える。

(もっと読む)

半導体装置

【課題】高度な集積化を実現した、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】チャネル形成領域を含む半導体層と、チャネル形成領域と電気的に接続するソース電極およびドレイン電極と、チャネル形成領域と重畳するゲート電極と、チャネル形成領域とゲート電極との間のゲート絶縁層と、を含み、ゲート絶縁層の側面の一部と、ソース電極またはドレイン電極の側面の一部と、は、平面方向から見て概略一致している半導体装置である。

(もっと読む)

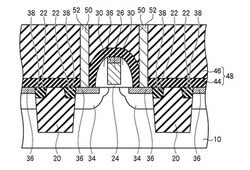

MOSトランジスタおよびその製造方法、半導体集積回路装置

【課題】MOSトランジスタのチャネル領域に、基板上に形成した応力膜からより効率的に応力を印加する半導体装置の構造及びその製造方法を提供する。

【解決手段】MOSトランジスタは、n型またはp型のソース・ドレイン領域21e〜hと、素子分離領域21Iからチャネル領域に向かって延在し、ソース・ドレイン領域21e〜hを覆って形成された、引張応力、圧縮応力のいずれかである応力膜27A、27Bを備える。応力膜27A,27Bは、ゲート電極23A,23Bの側壁面に沿って、ただし側壁面からは隙間32A〜Dを介して形成される。ソース・ドレイン領域21e〜hがn型である場合、応力膜の応力は引張応力であり、ソース・ドレイン領域21e〜hがp型である場合、応力膜の応力は圧縮応力である。

(もっと読む)

半導体装置

【課題】占有面積を増大させずに、電源投入開始後のチップ動作時にESD保護素子で発生するリーク電流を低減することができるESD保護素子を提供する。

【解決手段】電源ライン及び接地ラインを含む電子回路が形成された半導体基板10と、半導体基板10において電源ライン(Vdd)及び接地ライン(Vss)間に設けられ、サイリスタSCR及びサイリスタを駆動するトリガーダイオードTDを含む静電気放電保護素子とを有し、トリガーダイオードは、半導体基板10に形成されたアノード拡散層22と、アノード拡散層22から離間して半導体基板10に形成されたカソード拡散層21と、アノード拡散層22及びカソード拡散層21間において半導体基板10上にゲート絶縁膜16を介して形成されたゲート電極17とを有し、外部電源に接続された外部端子(パッド電極27)がゲート電極17に電気的に接続されている構成とする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】規則的に配列した複数の微細な開口部OPを有するフィルタFLを通過したイオンビーム22をレンズ26で収束して半導体ウエハ1Wに照射することにより、チャネルドープイオン注入を行なう。この際、フィルタFLには、イオンビーム22と同じ極性の電圧を印加する。フィルタFLの開口部OPの中央部に向かって入射した不純物イオンは、そのまま直進して開口部OPを通過することができるが、フィルタFLの開口部OPの中央部以外の領域に向かって入射する不純物イオンは、フィルタFLによる電場によって進行方向が曲げられて、開口部OPを通過することができない。このため、半導体ウエハ1Wに注入された不純物イオンは、規則的な配列を有したものとなり、MISFETのしきい値電圧のばらつきを抑制できる。

(もっと読む)

261 - 280 / 2,469

[ Back to top ]