Fターム[5F048BC06]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ソース・ドレイン (8,322) | 追加領域の形成 (3,324) | LDD (2,469)

Fターム[5F048BC06]に分類される特許

281 - 300 / 2,469

半導体装置

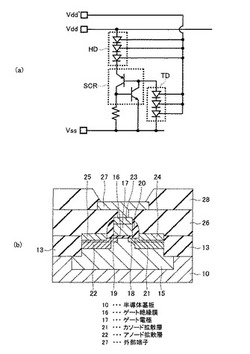

【課題】占有面積を増大させずに、電源投入開始後のチップ動作時にESD保護素子で発生するリーク電流を低減することができるESD保護素子を提供する。

【解決手段】電源ライン及び接地ラインを含む電子回路が形成された半導体基板10と、半導体基板10において電源ライン(Vdd)及び接地ライン(Vss)間に設けられ、サイリスタSCR及びサイリスタを駆動するトリガーダイオードTDを含む静電気放電保護素子とを有し、トリガーダイオードは、半導体基板10に形成されたアノード拡散層22と、アノード拡散層22から離間して半導体基板10に形成されたカソード拡散層21と、アノード拡散層22及びカソード拡散層21間において半導体基板10上にゲート絶縁膜16を介して形成されたゲート電極17とを有し、外部電源に接続された外部端子(パッド電極27)がゲート電極17に電気的に接続されている構成とする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】規則的に配列した複数の微細な開口部OPを有するフィルタFLを通過したイオンビーム22をレンズ26で収束して半導体ウエハ1Wに照射することにより、チャネルドープイオン注入を行なう。この際、フィルタFLには、イオンビーム22と同じ極性の電圧を印加する。フィルタFLの開口部OPの中央部に向かって入射した不純物イオンは、そのまま直進して開口部OPを通過することができるが、フィルタFLの開口部OPの中央部以外の領域に向かって入射する不純物イオンは、フィルタFLによる電場によって進行方向が曲げられて、開口部OPを通過することができない。このため、半導体ウエハ1Wに注入された不純物イオンは、規則的な配列を有したものとなり、MISFETのしきい値電圧のばらつきを抑制できる。

(もっと読む)

半導体装置及びその製造方法

【課題】サリサイド構造を有するMIS型電界効果トランジスタにおいて、ゲート電極とソース・ドレインコンタクトとの間の短絡を防止する。

【解決手段】ゲート電極175上にはシリサイド層230が形成されている。シリサイド層230の上面は、シリサイド層230の中央から両端に向けて低くなっており、当該両端におけるシリサイド層230の上面の高さは、オフセットスペーサ180の高さ以下である。

(もっと読む)

高誘電率のゲート絶縁膜を有する半導体装置及びそれの製造方法

【課題】本発明はゲート構造物として高誘電率を有する物質として、高誘電率を有する物質からなるゲート絶縁膜を含む半導体装置及びその製造方法に関する。

【解決手段】半導体装置及びその製造方法において、基板上に形成され、ハフニウムシリコン酸化物含有固体物質を含むゲート絶縁膜パターンと前記ゲート絶縁膜パターン上に形成される第1ゲート導電膜パターンを含むゲート構造物及び前記ゲート構造物と隣接する基板の表面部位に配置されており、n型不純物がドーピングされたソース/ドレイン領域を含むことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】界面キャリア層SCLを構成する電子の移動抑制手段として、MISFETQN1とMISFETQN2の間に電極層ELを設けて電極層ELと界面キャリア層SCLとの間に容量素子Cを形成する手段をとっている。そして、この容量素子Cの上部電極となる電極層ELに正電位を印加することにより、電極層ELに相対する界面キャリア層SCLの電子を固定している。

(もっと読む)

半導体装置及びその製造方法

【課題】動作電圧やしきい値電圧が相異なり、高誘電率ゲート絶縁膜/メタルゲート電極構造を有するP型MISFETを共通の基板上に混載可能にする。

【解決手段】半導体装置は、半導体基板100と、半導体基板100のうち第1のTr領域内に位置する領域に形成された第1の活性領域103aと、半導体基板100のうち第2のTr領域内に位置する領域に形成された第2の活性領域103bと、第1の活性領域103a上に形成された第1のP型MISFET150aと、第2の活性領域103b上に形成された第2のP型MISFET150bとを備えている。第1のP型MISFET150aは、ゲルマニウムを含有する半導体で構成された第1の半導体層104と、シリコンで構成された第2の半導体層105とを備えている。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】絶縁表面上に設けられたnチャネル型TFTを有する半導体装置は、半導体膜が引っ張り応力を受けるように、導電膜、例えばゲート電極に不純物元素が導入され、絶縁表面上に設けられたpチャネル型TFTを有する半導体装置は、半導体膜が圧縮応力を受けるように、導電膜、例えばゲート電極に不純物が導入されている。

(もっと読む)

半導体装置およびその製造方法

【課題】メモリセル領域のトランジスタにおけるソース/ドレイン電極上の半導体層同士の接触による短絡を防止しつつ、周辺回路領域のトランジスタにおけるせり上げソース/ドレイン領域を含むソース/ドレイン電極の高濃度不純物層の接合深さの均一性を図り、短チャネル効果を抑制する。

【解決手段】メモリセル領域における隣接するトランジスタ間で半導体層同士が接触しない膜厚にエピタキシャル成長させ、その際、周辺回路領域の素子分離2のみを後退させて露出した基板面からもエピタキシャル成長半導体層10を成長させることで、周辺回路領域の半導体層のファセットFが活性領域外に形成されるようにし、その後、周辺回路領域に高濃度不純物層11用のイオン注入を行う。

(もっと読む)

半導体基板の保持用トレイ、並びに半導体基板および半導体装置の作製方法

【課題】複数枚の絶縁層被覆単結晶半導体基板に対して効率よくイオン注入を行い、大面積の単結晶半導体層を備えた半導体基板の作製方法を提供することを課題の一とする。

【解決手段】半導体基板の作製工程において、表面のファンデルワールス力を調整した保持用トレイに表面に絶縁層が形成された複数枚の単結晶半導体基板を貼り合わせ、複数枚の単結晶半導体基板にイオン照射工程を行うことで複数枚の単結晶半導体基板の所定の深さに脆化層を形成し、複数枚の単結晶半導体基板にファンデルワールス力を調整したベース基板を貼り合わせることでファンデルワールス力の差を利用して保持用トレイを選択的に分離し、剥離加熱処理を行い劈開面を形成して単結晶半導体基板をベース基板から分離することにより、絶縁層を介して単結晶半導体基板をベース基板に転載する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1の主面にゲート絶縁膜用のHf含有膜4、Al含有膜5及びマスク層6を形成してから、nチャネル型MISFET形成予定領域であるnMIS形成領域1Aのマスク層6とAl含有膜5を選択的に除去する。それから、nMIS形成領域1AのHf含有膜4上とpチャネル型MISFET形成予定領域であるpMIS形成領域1Bのマスク層6上に希土類含有膜7を形成し、熱処理を行って、nMIS形成領域1AのHf含有膜4を希土類含有膜7と反応させ、pMIS形成領域1BのHf含有膜4をAl含有膜5と反応させる。その後、未反応の希土類含有膜7とマスク層6を除去してから、メタルゲート電極を形成する。マスク層6は、窒化チタン又は窒化タンタルからなる窒化金属膜6aと、その上のチタン又はタンタルからなる金属膜6bとの積層構造を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】pチャネル型の電界効果トランジスタのしきい値電圧を確実に制御して所望の特性が得られる半導体装置と、その製造方法とを提供する。

【解決手段】温度約700〜900℃のもとで施す熱処理に伴い、素子形成領域RPでは、アルミニウム(Al)膜7a中のアルミニウム(Al)がハフニウム酸窒化(HfON)膜6へ拡散することによって、ハフニウム酸窒化(HfON)膜6に元素としてアルミニウム(Al)が添加される。また、チタンアルミニウムナイトライド(TiAlN)膜からなるハードマスク8a中のアルミニウム(Al)とチタン(Ti)とがハフニウム酸窒化(HfON)膜6へ拡散することによって、ハフニウム酸窒化(HfON)膜6に元素としてアルミニウム(Al)とチタン(Ti)とが添加される。

(もっと読む)

半導体装置及びその製造方法

【課題】同一のチップに含まれるMISトランジスタの閾値電圧に、ばらつきが生じることを抑制する。

【解決手段】ゲート絶縁膜形成膜上に高融点金属膜16を形成する。次に、高融点金属膜をパターニングして、ゲート絶縁膜形成膜における第1の部分を露出する一方、ゲート絶縁膜形成膜における第2の部分を覆う金属マスク16bを形成すると共に、ゲート絶縁膜形成膜における第3の部分を覆うダミー金属マスク16cを形成する。次に、ゲート絶縁膜形成膜上に、調整用金属化合物膜17を形成する。次に、金属マスク及びダミー金属マスクを導入防止マスクとして、熱処理によりゲート絶縁膜形成膜に調整用金属化合物膜中の調整用金属を導入する。次に、調整用金属化合物膜、金属マスク及びダミー金属マスクを除去する。次に、ゲート絶縁膜形成膜上に、ゲート電極形成膜20を形成する。次に、ゲート電極形成膜及びゲート絶縁膜形成膜をパターニングする。

(もっと読む)

SOI基板の作製方法

【課題】エアボイドなどの貼り合わせに起因する欠陥を十分に抑制できるSOI基板の作製方法を提案することを目的の一とする。

【解決手段】ボンド基板とベース基板を対向させ、ボンド基板またはベース基板の端部に圧力をかけてボンド基板とベース基板の貼り合わせを開始させる時、または前に、ボンド基板表面、または、ベース基板表面の貼り合わせの開始地点における接平面に対して、ボンド基板における貼り合わせの終了地点がベース基板から離れるようにボンド基板を反らせ、および/または、ベース基板における貼り合わせの終了地点がボンド基板から離れるようにベース基板を反らせ、貼り合わせを開始させた後に、ボンド基板の反り量、および/または、ベース基板の反り量を制御することにより、ボンド基板とベース基板の貼り合わせに係る速度を制御する、SOI基板の作製方法である。

(もっと読む)

半導体装置

【課題】アンテナスイッチのコスト削減を図る観点から、特に、アンテナスイッチをシリコン基板上に形成された電界効果トランジスタから構成する場合であっても、アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】TXシャントトランジスタSH(TX)を構成するMISFETQN1〜MISFETQN5において、GND端子に近い側に接続されたMISFETQN5から送信端子TXに近い側に接続されたMISFETQN1になるに連れて、ゲート幅Wgが大きくなるように構成されている。

(もっと読む)

半導体装置の製造方法

【課題】p型MOSトランジスタの半導体埋め込み領域形成に付随する不具合が抑制される技術を提供する。

【解決手段】半導体装置の製造方法は、n型、p型MOSトランジスタの配置される第1、第2活性領域にまたがりシリコンでゲート電極を形成する工程と、第1活性領域とその近傍のゲート電極へのn型不純物注入工程と、第2活性領域及びその近傍のゲート電極を露出するマスクの形成工程と、マスク開口内の第2活性領域及びゲート電極をエッチングする凹部形成工程と、凹部表面の自然酸化膜を除去しこれに伴い開口が後退する工程と、凹部表面をハロゲンガスでクリーニングする工程と、凹部への半導体埋め込み領域形成工程とを有し、クリーニング工程時に後退した開口内にゲート電極上n型領域が露出していないように、ゲート電極上n型領域の第2活性領域側の端とマスク開口の第1活性領域側の縁とが離される。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】単結晶シリコン基板に形成されたnチャネル型MOSFETを有する半導体装置において、チャネル形成領域が引っ張り応力を受けるように、導電膜には不純物が導入され、単結晶シリコン基板に形成されたpチャネル型MOSFETを有する半導体装置において、チャネル形成領域が圧縮応力を受けるように、導電膜には不純物が導入されている。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタの特性を劣化させることなくポリシリコン抵抗素子を製造できる半導体装置の製造方法を提供する。

【解決手段】半導体基板30の抵抗素子形成領域に抵抗素子となるポリシリコン膜35aを形成するとともに、トランジスタ形成領域にポリシリコンゲート35b及び高濃度不純物領域40を形成する。その後、全面に絶縁膜41を形成した後、トランジスタ形成領域をフォトレジスト膜42で覆い、ポリシリコン膜35aに導電性不純物をイオン注入する。次いで、フォトレジスト膜42をアッシングにより除去する。このとき、トランジスタは絶縁膜41に覆われているため、アッシングによるダメージが回避される。また、抵抗素子領域に導入された導電性不純物が大気中のO及びHと反応して酸が発生しても、ポリシリコンゲート及び高濃度不純物領域40が酸により溶解することが回避される。

(もっと読む)

半導体装置およびその製造方法

【課題】SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を向上させる。また、半導体装置の製造工程を簡略化する。

【解決手段】SOI基板SB上に形成された複数のnチャネル型MOSFETQnを有する半導体装置において、BOX膜の下部の支持基板の上面に拡散層であるn+型半導体領域を形成し、n+型半導体領域と電気的に接続され、素子分離領域1を貫くコンタクトプラグCT2を形成することで、支持基板の電位を制御する。SOI基板SBの平面において、各nチャネル型MOSFETQnは第1方向に延在しており、第1方向に複数形成されて隣り合うコンタクトプラグCT2同士の間に配置された構造とする。

(もっと読む)

半導体装置及びその作製方法

【課題】半導体装置の作製工程数を減少させること、半導体装置の歩留まりを向上させること、半導体装置の作製コストを低減することを課題とする。

【解決手段】基板上に、単結晶半導体層をチャネル形成領域に有する第1のトランジスタと、当該第1のトランジスタと絶縁層を介して分離され、酸化物半導体層をチャネル形成領域に有する第2のトランジスタと、当該単結晶半導体層及び酸化物半導体層を有するダイオードを有する半導体装置、及び、その作製方法に関する。

(もっと読む)

半導体薄膜基板および半導体薄膜基板を用いた半導体装置の作製方法

【課題】一層の半導体層から膜厚の異なる半導体層を有する半導体薄膜基板を提供することを目的の一とする。または、半導体薄膜基板を適用した半導体装置を提供することを目的の一とする。

【解決手段】基板上に半導体層を形成し、半導体層を加工して第1の島状半導体層および第2の島状半導体層を形成し、第1の島状半導体層にレーザー照射を行うことにより第1の島状半導体層を溶融させ、第1の島状半導体層から第2の島状半導体層より膜厚が厚い第3の島状半導体層を形成する、半導体薄膜基板の作製方法である。

(もっと読む)

281 - 300 / 2,469

[ Back to top ]