Fターム[5F048BC06]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ソース・ドレイン (8,322) | 追加領域の形成 (3,324) | LDD (2,469)

Fターム[5F048BC06]に分類される特許

2,301 - 2,320 / 2,469

半導体装置の製造方法及び半導体装置

【課題】ポリシリコン配線の表面においてシリサイド膜が高抵抗化する領域をできにくくし、かつポリシリコン配線に導入されたP型不純物がN型素子領域に拡散することが抑制できる半導体装置の製造方法を提供する。

【解決手段】素子分離膜2を形成し、次いで、第1及び第2ゲート酸化膜4b,4aを形成する。次いで、第1ゲート電極4b、第2ゲート電極4a、及びポリシリコン配線4cを形成する。第1の境界線Sより第1素子領域1b側に位置するポリシリコン配線4c、及び第1ゲート電極4bに、N型の不純物を注入する。また、第2の境界線Mより第2素子領域側1aに位置するポリシリコン配線4c、及び第2ゲート電極4aに、P型の不純物を注入する。第1の境界線Sは、第1素子領域1bと第2素子領域1aの中間1bより第2素子領域1a側に設定され、第2の境界線Mは、中間に設定される。

(もっと読む)

半導体装置

【課題】 ゲートリーク電流および閾値電圧が低く、CMOS構造を有する半導体装置を提供する。

【解決手段】 NMOSFETは、シリコン酸化膜10と、ハフニウムシリケート膜11とからなるゲート絶縁膜と、このゲート絶縁膜の上に形成されたN型ポリシリコン膜15を有するゲート電極とを備える。また、PMOSFETは、シリコン酸化膜12と、ハフニウムシリケート膜13と、アルミニウム酸化膜14とからなるゲート絶縁膜と、このゲート絶縁膜の上に形成されたP型ポリシリコン膜16を有するゲート電極とを備える。アルミニウム酸化膜14の膜厚は2nm以下であることが好ましい。

(もっと読む)

半導体装置

【課題】接合リーク電流の増大、接合耐圧の劣化を抑制したシリサイドコンタクトを達成する半導体装置の製造方法を提供する。

【解決手段】ソース及びドレイン領域(S,D)形成のドーパントイオン打ち込み工程を、ウエル領域(3)との間にp/n接合を形成する1回のドーパントイオン打ち込みと、ソース・ドレイン領域(S,D)とウエル領域との間のp/n接合位置に影響を与えない打ち込み深さが浅く、かつ打ち込み量の多い1回のドーパントイオン打ち込みに分けて行う。そして、ドーパントの活性化熱処理を実施した後、ソース・ドレイン領域表面をシリサイド化(12)することにより、ソース・ドレイン領域(S,D)の低抵抗化とともにp/n接合リークの低減を図ることができる。

(もっと読む)

不揮発性半導体記憶装置とその製造方法

【課題】メモリセルトランジスタと低電圧トランジスタと高電圧トランジスタのゲート電極の間に絶縁膜を埋め込むことが容易な不揮発性半導体記憶装置を提供する。

【解決手段】メモリセルトランジスタのトンネル絶縁膜15と低電圧トランジスタの低電圧ゲート絶縁膜14と高電圧トランジスタの高電圧ゲート絶縁膜16を半導体基板7の上に形成する。第1のn型半導体膜17をトンネル絶縁膜15と低電圧ゲート絶縁膜14と高電圧ゲート絶縁膜16の上に成膜する。第1絶縁膜19を第1のn型半導体膜17の上に成膜する。第2のn型半導体膜21を露出した第1の半導体膜17と第1絶縁膜19の上に形成する。メモリセルトランジスタの制御ゲート電極23と低電圧トランジスタと高電圧トランジスタのゲート電極21、23をマスクに第2のn型半導体膜21においてn型不純物の濃度よりp型不純物の濃度が低くなるようにp型不純物のイオン注入を行い半導体基板7内に導電型がp型であるソース・ドレイン領域38を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 High−k膜を用いたMISFETの電子移動度および正孔移動度を共に増加させ高性能の相補型MISFETを形成する。

【解決手段】 シリコン基板1の表面部にpウェル層2およびnウェル層3が形成され、素子分離領域4により区画されたnチャネルMISFETには、窒素添加のないnチャネル界面層5、窒素添加のないnチャネル高誘電体ゲート絶縁膜6およびnチャネルゲート電極7が形成されている。そして、n型ソース・ドレイン拡散層8が設けられている。これに対して、pチャネルMISFETでは、窒素添加のpチャネル界面層9、窒素添加のpチャネル高誘電体ゲート絶縁膜10およびpチャネルゲート電極11が形成されている。そして、p型ソース・ドレイン拡散層12が設けられている。

(もっと読む)

半導体装置の製造方法

【課題】 相補型半導体装置における閾値電圧のバラツキの発生を抑制する。

【解決手段】 シリコン基板11に素子分離12を形成し、p型ウェル13とn型ウェル14を形成する。シリコン基板11上にシリコン酸化膜よりも高い比誘電率を有するHfAlOx膜16を形成し、ポリシリコンゲルマニウム膜18を形成する。PMIS領域を覆うレジストパターン19を形成した後、NMIS領域のポリシリコンゲルマニウム膜18にリンイオン20を注入した後、拡散用の熱処理を行う。NMIS領域を覆うレジストパターン21を形成した後、PMIS領域のポリシリコンゲルマニウム膜18にボロンイオンを注入した後、拡散用の熱処理を行う。その後、ポリシリコンゲルマニウム膜18をパターニングしてゲート電極を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】

本発明はMOSFETのジャンクションリークの劣化を抑えつつ、かつ、ショートチャネル効果の抑制を可能とする半導体装置およびその製造方法を提供することを目的とする。

【解決手段】

DRAM/Logic混載デバイス又はDRAMデバイスにおけるDRAMアレイ領域のトレンチセルを構成するトレンチキャパシタTCと転送トランジスタにおいて、転送トランジスタのドレイン領域21下の領域に半導体基板10と同じ導電型の不純物イオンを注入し、高濃度のポケットインプラ領域23を形成させる。一方、転送トランジスタのソース領域22下の領域にはこのポケットインプラ領域は形成させない。

(もっと読む)

半導体装置、ICカード、ICタグ、RFID、トランスポンダ、紙幣、有価証券類、パスポート、電子機器、バッグ及び衣類

【課題】 IDチップに用いる半導体装置において、役割が終了したり、失効したときにその後の動作を停止する半導体装置を提供することを課題とする。

【解決手段】 本発明は、絶縁基板上にアンテナ回路と、電圧検出回路と、電流増幅回路と、信号処理回路と、ヒューズとを有し、アンテナ回路に大電力が印加されたときに、電圧検出回路にて電圧を検出し、その電流に応じた電流を電流増幅回路で増幅し、ヒューズを溶断する。また、アンチヒューズが用いられる時は過大な電圧を加えて、アンチヒューズを短絡させる。このように信号処理回路の動作を停止させ、役割が終了した、または失効したときに無効とする機能を有する半導体装置であることを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】正孔または電子の移動度を高めるとともに、NMOS領域とPMOS領域との表面の段差を抑制することが可能な半導体装置および半導体装置の製造方法を提供する。

【解決手段】本発明は、NMOS領域AとPMOS領域Bとを同一の基板11に備えた半導体装置であって、NMOS領域Aの基板11上に設けられるとともに、基板11の表面と異なる面方位を有する歪みSi層21と、PMOS領域Bの基板11上に設けられるとともに、基板11の表面と同じ面方位を有する歪み層からなる歪みSiGe層31とを備えたことを特徴とする半導体装置およびその製造方法である。

(もっと読む)

半導体装置およびその製造方法

【課題】 高いON電流を有し、しかも消費電力の低いCMOS回路を実現するためのMISトランジスタ構造を提供する。

【解決手段】 nチャネル型MISトランジスタ(Qn)とpチャネル型MISトランジスタ(Qp)のそれぞれのゲート絶縁膜5は、酸化ハフニウム膜で構成されている。また、ゲート電極18は、ゲート絶縁膜5と接する領域の近傍において、Pt原子に対するSi原子の比がほぼ1(PtSix:x=1)のPtシリサイド膜で構成されている。pチャネル型MISトランジスタ(Qp)のゲート電極17は、ゲート絶縁膜5と接する領域の近傍において、Pt原子に対するSi原子の比が1未満(PtSix:x<1)のPtシリサイド膜で構成され、ゲート電極17のフェルミレベルピニングが抑制されている。

(もっと読む)

無線チップ

【課題】 無線通信によりデータの交信が可能なIDタグにおいて、IDタグのサイズやICチップのサイズを縮小し、チップ内の限られた面積の有効活用、消費電流の低減、通信距離の低下を防止すること課題とする。

【解決手段】集積回路と、共振容量部と、保持容量部とを備えたICチップと、前記ICチップ上に絶縁膜を介して少なくとも一部が重なるようにアンテナを設け、前記アンテナと前記絶縁膜と前記集積回路を形成する配線または半導体膜とからなる積層構造を設け、当該積層構造によって、共振容量部および保持容量部の一方または両方の容量素子を構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 消費電力を抑えた、信頼性の高い半導体装置を提供する。

【解決手段】 半導体基板1上に形成された種類の異なる第一トランジスタと第二トランジスタを少なくとも有し、第一トランジスタは、LDD注入を行った後、アニール処理を行い、第二トランジスタはLDD注入を行った後、ソース/ドレイン注入前にアニール処理を行わず、ソース/ドレイン注入後にアニール処理することにより作成されている。第一トランジスタにおけるドレイン領域31とLDD領域20の境界からLDD領域20とチャンネル領域41の境界までの最短距離が、第二トランジスタにおけるドレイン領域33とLDD領域22の境界からLDD領域22とチャンネル領域43の境界までの最短距離よりも短い。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されたCMOS半導体装置に適したpMOSとnMOSにおいてそれぞれ適切に制御されたGe濃度分布及び形状を有するSi/SiGeゲート電極構造を備えた半導体装置を提供することである。

【解決手段】上記の課題を解決した半導体装置は、半導体基板上に形成された絶縁膜と、前記絶縁膜上に形成され、前記絶縁膜との界面近くで高いゲルマニウム濃度を有し、その反対側表面で低いゲルマニウム濃度を有する第1のゲート電極と、前記絶縁膜上に形成され、電極中でほぼ一様なゲルマニウム濃度を有し、6×1020atoms/cm3以上の濃度のn型不純物を有する第2のゲート電極とを具備する。

(もっと読む)

基板傾斜を用いた半導体ドーピング

【課題】半導体基板をドープする方法、特に、注入源に対する基板の傾斜角を変えることによってドーパントを注入する方法を提供する。

【解決手段】基板にドーパントを注入する方法、及びそのような注入を利用して半導体素子を製造する方法。ドーパントを注入する方法は、他の段階の中でもとりわけ、注入プラテン(305)上又はその上に位置する基板(310)を注入源(320)に対して第1の方向の軸線に関して傾斜させる段階と、第1の方向に傾斜した基板(310)を使用して注入線量の一部分を注入する段階と、次に、基板(310)を第1の方向と反対の第2の方向に傾斜させる段階と、第2の方向に傾斜した基板(310)を使用して注入線量の別の部分を注入する段階とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】

5〜10V程度のスナップバック耐圧をもつデバイスをセルフアライン法で実現することができる半導体装置及びその製造方法を提供すること。

【解決手段】

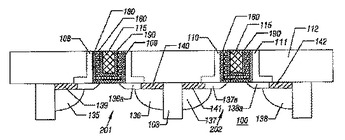

主ゲート6aの隣に所定の間隔をおいて配された2個以上の副ゲート6b、6cと、副ゲート6b、6cの下であってソース/ドレイン層9a、9bの端部から主ゲート6aの端部近傍まで連続的に配されるとともに、ソース/ドレイン層9a、9bと同電位型であり、不純物の濃度がソース/ドレイン層9a、9bよりも低濃度である低濃度層7a、7bと、を備える。

(もっと読む)

半導体装置とその製造方法

【課題】 トランジスタの閾値を十分制御することのできるシリサイドゲート電極を作成できる半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、(a)シリコン基板の複数の活性領域上に、夫々、ゲート絶縁膜、多結晶シリコン層を含む積層構造を形成する工程と、(b)前記多結晶シリコン層の各々にn型またはp型の不純物を注入する工程と、(c)前記多結晶シリコン層の各々に注入された不純物を活性化する工程と、(d)工程(c)の後、前記各多結晶シリコン層を覆ってシリサイド反応可能な金属層を堆積する工程と、(e)全記多結晶シリコン層と前記金属層との間でシリサイド化反応を生じさせ、前記多結晶シリコン層の全厚さがシリサイド化されたゲート電極を形成する工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】微細なMISトランジスタにおいても基板バイアスによる閾値電圧の制御を可能としうる高性能の半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10内に形成され、チャネル領域を有するウェル58と、チャネル領域上に絶縁膜32を介して形成されたゲート電極34nと、ゲート電極34nの両側のウェル58内に、チャネル領域を挟むように配置されたソース/ドレイン領域60と、ソース/ドレイン領域60とチャネル領域との間に形成されたポケット領域40とを有する。ウェル58は、ポケット領域40よりも深くソース/ドレイン領域60の底部よりも浅い領域に不純物濃度の第1のピークを有し、ソース/ドレイン領域60の底部近傍の領域に不純物濃度の第2のピークを有する。

(もっと読む)

適応型負性微分抵抗デバイス

【課題】 単一のシリコンウェーハ中に形成した互いに異なる回路に多様な負性微分抵抗(NDR)特性を付与できるように製造工程中または出荷後のフィールドでの通常動作中に最大電流対最小電流比(PVR)値などの特性値を調整できるようにしたNDRデバイスを提供する。

【解決手段】 互いに異なるNDRモードを発現するように動作中に多様にNDR特性を変える過程を含むNDR素子の制御の方法を開示している。NDR素子(シリコン利用のNDR FETなど)に印加するバイアスの条件を変えることによって、最大電流対最小電流比(PVR)値(またはそれ以外の特性)をNDR素子利用回路の所望の動作変化の実現のために動的に変えることができる。例えば、メモリ用または論理回路用では、動作電力の削減のために最小電流値を休止期間中に小さくすることができる。すなわち、適応型NDR素子を慣用の半導体回路の中で有利に活用することができる。

(もっと読む)

金属ゲート電極半導体デバイス

高誘電率ゲート誘電体を有するNMOS及びPMOSトランジスタを含む相補型金属酸化物半導体集積回路が半導体基板上に形成される。ゲート誘電体上に金属障壁層が形成される。金属障壁層上に仕事関数設定金属層が形成され、仕事関数設定金属層上にキャップ金属層が形成される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 従来のチャネル領域に不純物を注入することのみで閾値電圧を調整するよりも少ない不純物量で電界効果型トランジスタの閾値電圧を調整する。

【解決手段】 半導体装置100は、シリコン基板101と、シリコン基板101上に形成されたSiON膜113および多結晶シリコン膜106を含むP型MOSFET103を備える。多結晶シリコン膜106とSiON膜113との界面115に、Hf、Zr、Al、La、Pr、Y、Ti、TaおよびWからなる群から選択される一または二以上の金属が存在する構成とし、界面115における当該金属の濃度を5×1013atoms/cm2以上1.4×1015atoms/cm2未満とする。

(もっと読む)

2,301 - 2,320 / 2,469

[ Back to top ]