Fターム[5F048BC06]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ソース・ドレイン (8,322) | 追加領域の形成 (3,324) | LDD (2,469)

Fターム[5F048BC06]に分類される特許

2,341 - 2,360 / 2,469

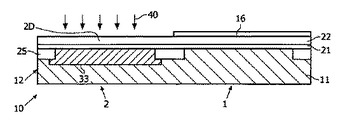

薄膜トランジスタパネル及びその製造方法

【課題】 アモルファスシリコン薄膜トランジスタとポリシリコン薄膜トランジスタとを備えた薄膜トランジスタパネルにおいて、より一層の小型化を図る。

【解決手段】 アモルファスシリコンからなる半導体薄膜41を有する光電気変換型の薄膜トランジスタ3は、ポリシリコンからなる半導体薄膜25、26を有する駆動回路用のCMOS薄膜トランジスタ21、22よりも上層側に設けられている。これにより、半導体薄膜41を半導体薄膜25、26と同一の層上に設ける場合と比較して、より一層の小型化を図ることができる。この場合、薄膜トランジスタ3のボトムゲート電極9、ソース・ドレイン電極10及びトップゲート電極8と薄膜トランジスタ21、22のソース・ドレイン電極を含む導電体層35、36とを接続する接続配線の一部である上層接続配線48、51、54は、トップゲート電極8が設けられたトップゲート絶縁膜39上に設けられている。

(もっと読む)

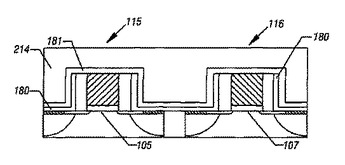

分離ウェルを用いるMOSバラクタ

【課題】 向上した調節能力と高い品質係数Qとを有するバラクタ及びその製造方法を提供すること。

【解決手段】 本発明は、向上した調節能力と高い品質係数Qとを有するバラクタ22、及び、バラクタ22を製造する方法を提供する。本発明の方法は、従来のCMOS処理スキーム又はBiCMOS処理スキームに組み込むことができる。この方法は、第1の導電型の半導体基板12と、該基板12の上部領域11の下方に配置された、第2の導電型のサブコレクタ14又は分離ウェル(すなわち、ドープ領域)とを含む構造体であって、該第1の導電型は、第2の導電型とは異なる構造体を準備するステップを含む。次に、複数の分離領域16が、基板12の上部領域11内に形成され、次いで、ウェル領域が、基板12の上部領域11内に形成される。場合によっては、本発明のプロセスのこの時点で、ドープ領域14が形成される。ウェル領域は、第2の導電型の外側ウェル領域20A及び20Cと、第1の導電型の内側ウェル領域20Bとを含む。ウェル領域の各々のウェルは、分離領域16によって上面で分離される。次に、内側ウェル領域20Bの上方に、少なくとも第1の導電型のゲート導体26を有する電界効果トランジスタが形成される。

(もっと読む)

ボイドのないゲート電極を具備したトランジスタの製造方法

【課題】 ボイドのないゲート電極を具備したトランジスタの製造方法を提供する。

【解決手段】 半導体基板上にゲート酸化膜を形成した後、前記ゲート酸化膜の上部にゲート電極用ポリシリコン膜を蒸着する。次いで、前記ポリシリコン膜にp型不純物をイオン注入し、前記ポリシリコン膜の所定厚さほどを化学機械的研磨方法で除去する。

(もっと読む)

半導体装置およびその製造方法

【課題】ボディコンタクトを有するSOIデバイスにおいて、ボディコンタクトとボディ領域との間に所望の抵抗値を持たせると共に、当該抵抗値のばらつきを抑制する。

【解決手段】SOI層3におけるコンタクト61との接続部分(即ち、素子分離絶縁膜41の下)に、不純物濃度の高いP+領域を形成せずに、SOI層3とボディコンタクト61とをショットキー接合させる。また、ボディコンタクト61の表面にはバリアメタル61aが形成されており、ボディコンタクト61とSOI層3との間に、バリアメタル61aとSOI層3とが反応したシリサイド70が形成される。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置の製造方法として、縦型バイポーラトランジスタの底部に、形状良く低抵抗層を設ける方法を提供する。

【解決手段】2重SOI基板を用意する工程と、ディープトレンチを形成する工程と、ディープトレンチを埋め込む工程と、開口部54を設ける工程と、空孔部56を設ける工程と、多結晶シリコン層80を堆積する工程と、バイポーラトランジスタを形成する工程とを有している。開口部を設ける工程では、ドライエッチングを行って、バイポーラトランジスタ被形成領域55の、第2埋め込み酸化膜40を露出させる。空孔部を設ける工程では、ウェットエッチングにより、バイポーラトランジスタ被形成領域内の第2埋め込み酸化膜を除去する。多結晶シリコン層を堆積する工程では、上述の工程で形成された、互いに連通している開口部及び空孔部に多結晶シリコン層を堆積する。

(もっと読む)

半導体装置

【課題】直接トンネル電流が流れる程度に薄膜化されたゲート絶縁膜におけるゲート電極からのドーパント原子の基板への拡散を防止すると共に、ゲートリーク電流を低減できるようにする。

【解決手段】第1の素子形成領域51及び第2の素子形成領域52に区画された半導体基板11上に、酸化膜からなる第1のゲート絶縁膜13Aを形成する。次に、第1のゲート絶縁膜13Aの第2の素子形成領域52に含まれる部分を除去し、半導体基板11に対して酸窒化性雰囲気で熱処理を行なうことにより、第2の素子形成領域52上に膜厚が第1のゲート絶縁膜13Aよりも小さい酸窒化膜からなる第2のゲート絶縁膜15Bを形成する。次に、第1のゲート絶縁膜13B及び第2のゲート絶縁膜15Bを窒素プラズマに暴露することにより、窒素原子をさらに導入された第1のゲート絶縁膜13C及び第2のゲート絶縁膜15Cを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】サイドウォールの応力によってキャリア移動度を高めることにより、CMOSトランジスタの高速化を図る半導体装置及びその製造方法を提供する。

【解決手段】NMISトランジスタのゲート電極14a及びPMISトランジスタのゲート電極14bの側面上に、引張応力を有する第1のサイドウォール16a、16bを形成する。その後、基板上の全面に、圧縮応力を有する圧縮応力含有絶縁膜17を形成する。その後、レジスト18をマスクにして、圧縮応力含有絶縁膜17を選択的にエッチングして、ゲート電極14bの側面上に、第2のサイドウォール17aを形成する。その後、第2のサイドウォール17aを覆うレジスト19をマスクにして、圧縮応力含有絶縁膜17を除去する。その後、半導体基板11上の全面に、実質的に応力が生じない層間絶縁膜21を形成する。

(もっと読む)

半導体装置とその製造方法

【課題】PMOSFETにおいて、ショートチャネル効果を抑制でき、より短いゲート長での動作を確保できる半導体装置及びその製造方法を提供することである。

【解決手段】半導体基板に形成されたnウエル領域とnウェル領域上に形成されたゲート電極と、ゲート電極の両端部のnウェルの表面層に形成された一対のボロン含有拡散領域と、ボロン含有拡散領域と同等もしくはより深く、かつ、ゲート電極下においてボロン含有拡散領域と同等もしくはより広い、フッ素、窒素、または炭素からなる群から選択される少なくともいずれかの一の拡散抑制元素を拡散した拡散抑制元素拡散領域と、ボロン含有拡散領域より深く、かつ、横方向端部がボロン含有拡散領域の横方向端部よりゲート電極端から離れた位置にあるp型の不純物拡散領域とを有する半導体装置である。

(もっと読む)

相補型金属−酸化膜−半導体電界効果トランジスタ構造

相補型金属−酸化膜−半導体電界効果トランジスタ構造(100)はイオン注入領域(126,128)を2つの相補型素子の内の一方のみに含む。トランジスタ構造(100)は通常、化合物半導体基板(102)と、そしてエピタキシャル層構造(104)と、を含み、エピタキシャル層構造は、エピタキシャル層構造の導電型を決定する一つ以上のドナー層を含む。イオン注入領域は、これらの相補型素子の内の一方に位置するエピタキシャル層構造(104)の導電型を「反転する」または「逆にする」ように作用する。例示として実施形態では、p型アクセプターをドープしたイオン注入領域がpチャネル素子(122)において使用され、nチャネル素子(120)はイオン注入されない状態のままである。  (もっと読む)

(もっと読む)

薄膜半導体装置及びその製造方法、電気光学装置、電子機器

【課題】 サージ電圧から内部回路を良好に保護することができる保護回路を構成でき、過大電圧により破壊された場合にも回路動作に不具合を生じることがない、信頼性に優れた保護回路素子を具備した薄膜半導体装置を提供する。

【解決手段】 基体と、該基体上に形成された半導体膜とを具備した薄膜半導体装置において、前記基体上に内部回路(主回路部)17と、保護回路部18と、端子部19とが設けられており、前記保護回路部18に、前記半導体膜を有するPINダイオードと、該PINダイオードのI層と絶縁膜を介して対向配置された浮遊電極とを備えた保護回路素子181,182が設けられている構成とした。

(もっと読む)

半導体装置及びその製造方法

【課題】同一の半導体基板上に、2種類以上のゲート絶縁膜及びゲート電極を有するMIS型トランジスタを備えた半導体装置及びその製造方法を提供する。

【解決手段】半導体基板11の第1のNMISトランジスタ形成領域AreaAには、ハフニウム酸化膜のような金属酸化膜からなるゲート絶縁膜21aとタングステン膜のような金属膜からなるゲート電極22aを有する第1のNMISトランジスタを形成する。また、半導体基板11の第2のNMISトランジスタ形成領域AreaCには、シリコン酸化膜からなるゲート絶縁膜13とポリシリコン膜のような半導体材料からなるゲート電極14cを有する第2のNMISトランジスタを形成する。ゲート電極22aは、ゲート電極14cと同時に形成した第1のダミーゲート電極14aを除去して設けられたゲート電極形成用開口20a内に金属膜を埋め込んで形成されたダマシン構造を有する。

(もっと読む)

移動度を半導体素子において増加させる方法及び装置

トランジスタのチャネル領域における移動度の増大を実現する方法及び装置が提示される。一の実施形態では、チャネル領域(18)は2軸応力が発生する基板の上に形成される。ソース領域(30)及びドレイン領域(32)は基板の上に形成される。ソース領域及びドレイン領域は1軸応力を2軸応力発生チャネル領域に追加する形で発生させるように作用する。1軸応力及び2軸応力はPチャネルトランジスタに関しては共に圧縮応力であり、そしてNチャネルトランジスタに関しては共に引っ張り応力である。その結果、キャリア移動度が短チャネルトランジスタ及び長チャネルトランジスタの両方に関して増加する。両方のタイプのトランジスタを同じ集積回路に搭載することができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 素子分離部(STI)によって基板内に生じる応力を抑制し、接合リーク電流の問題を低減する。

【解決手段】 シリコン基板1の活性領域(ウェル領域)中に溝部8が形成され、その内周に熱酸化膜2による側壁部2A及び底部2Bが形成され、その内部に補填材としてのポリシリコン膜4が充填され、その上部にCVDによるシリコン酸化膜(蓋部)3が設けられている。STIの溝部8内にシリコン基板1と熱膨張率の近いポリシリコン膜4を設けたことから、STIとその周辺領域とで熱変動に対する体積変化率が近くなり、内部応力を抑制することができる。

(もっと読む)

半導体装置及びかかる半導体装置の製造方法

本発明は、金属及び更なる元素の両方を含有する化合物を含むゲート領域(1D、2D)を有するNMOST1及びPMOST2を備えるCMOSデバイス(10)に関する。本発明によれば、第1及び第2導電材料はいずれも、モリブデン及びタングステンを含むグループから選択される金属を前記金属として含む化合物を備えると共に、炭素、酸素、カルコゲナイドを含むグループから選択される元素を前記更なる元素として含んでいる。第1及び第2導電材料はいずれも、モリブデン及び炭素または酸素から成る化合物を含むことが好ましい。また本発明は、かかるデバイスを製造する魅力的な方法も提供する。  (もっと読む)

(もっと読む)

高性能なサブ0.1マイクロメートルトランジスタ用のソース/ドレイン構造

【課題】チャネルパンチスルーおよび短チャネル効果が低減された、高性能な短チャネル長のトランジスタ構造を提供すること。

【解決手段】本発明によるトランジスタ構造(10)は、基板内に形成されたp型ウェル12を備える。ゲート構造(14)は、ソース領域(18)とドレイン領域(20)との間に挿入されたチャネル領域(16)上に形成される。ゲート構造(14)は、ゲート誘電体24上にゲート電極(22)と、ゲート(22)の面に沿った側壁26を有する。ソース領域(18)は、n型の低濃度ドープ領域(32)と、n+領域34とを有するが、ソースhalo領域は有しない。ドレイン領域(20)は、n型の低濃度ドープ領域42と、n+領域44と、p型ドレインhalo領域(50)とを有する。ドレインhalo領域(50)は、ドレイン領域にイオンを斜めに注入することにより形成された、ドープ領域である。

(もっと読む)

非対称なヘテロドープされた高電圧のMOSFET(AH2MOS)

非対称なヘテロドープされた金属酸化物(AH2MOS)半導体デバイスは基板と、前記基板の頂部にあってソース領域とドレイン領域との間に配置された絶縁ゲートと、からなる。ゲートの一方の側面には、ヘテロドープされたタブ及びソース領域が形成されている。タブ領域は第2極性のドーパントを有している。ソース領域が各タブ領域内に配置されており、第2極性と反対の第1極性のドーパントを有している。ゲートの他方の側面には、ヘテロドープされたバッファ及びドリフト領域が形成されている。バッファ領域は第2極性のドーパントからなる。ドリフト領域がバッファ領域内に配置され、第1極性のドーパントによってドーピングされている。ドレインn+タップ領域がドリフト領域内に配置されている。  (もっと読む)

(もっと読む)

半導体集積回路装置及びそれを用いた半導体システム

【課題】簡単な構成によりNBTI対策機能を備え、高信頼性を実現した半導体集積回路装置と半導体システムを提供する。

【解決手段】MOSFET回路を構成するPチャネルMOSFETのうち、NBTIによって回路動作マージンが劣化すると予測されるMOSFETをターゲットとして、そのゲートに信号供給を行う伝達経路に第1スイッチを設け、所定の動作モードのときに上記第1スイッチをオフ状態にし、かつ、上記MOSFETのゲートにチャネル電圧よりも絶対値的に高い電圧を供給する回復電圧印加回路を設ける。

(もっと読む)

半導体装置

【課題】 集積度の向上が容易な半導体装置を提供する。

【解決手段】 活性領域4aには、nMOSトランジスタ10の1対のソース/ドレイン領域11、11が形成されている。1対のソース/ドレイン領域11、11に挟まれる半導体基板の領域上にゲート酸化膜を介してゲート電極層13が形成されている。ゲート電極層13は、活性領域4a上および素子分離構造上の双方に延在し、かつ素子分離構造上にコンタクトパッド部13aを有し、かつ活性領域4aとコンタクトパッド13aとの平面的な間隔S1が0.5μm未満である。

(もっと読む)

置換金属ゲート形成のための半導体構造の平坦化

窒化物および充填層を含む犠牲ゲート構造は、金属ゲート電極と置換される。金属ゲート電極は、充填層で被覆された窒化物層で再度被覆される。窒化物および充填層の置換によって、歪みが再導入され、エッチング停止層が提供される。  (もっと読む)

(もっと読む)

半導体基板内の分離溝に隣接するコンタクト用開口の形成方法

【課題】フィールド分離マスに隣接する領域にコンタクト用開口を形成する半導体製造方法を提供する。

【解決手段】トレンチ形成・埋め込み法によって半導体基板の中にフィールド分離マスを形成し、該フィールド分離マスに隣接した基板上に基板マスキング層を形成する工程であって、前記フィールド分離マスの上面はエッチングストップキャップによって覆われ、その側壁は前記マスキング層によって覆われる工程と、前記分離マス側壁の少なくとも一部を露出するために、分離マスから分けて前記基板マスキング層を除去する工程と、露出した分離マス側壁上にエッチングストップカバーを形成する工程と、前記分離マス及び該分離マスに隣接する基板領域上に絶縁層を形成する工程と、前記分離マスエッチングストップキャップ及びカバーに対して選択的に、前記分離マスに隣接する前記絶縁層を貫通するコンタクト用開口をエッチング開口する工程とからなる、フィールド分離マスに隣接する領域にコンタクト用開口を形成する半導体製造方法。

(もっと読む)

2,341 - 2,360 / 2,469

[ Back to top ]