Fターム[5F048BC06]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ソース・ドレイン (8,322) | 追加領域の形成 (3,324) | LDD (2,469)

Fターム[5F048BC06]に分類される特許

2,321 - 2,340 / 2,469

半導体装置及びそれを用いたスイッチング電源装置

【課題】LC共振を用いたソフトスイッチングの電源装置において、スイッチング素子のドレイン電圧の振れによる制御回路の誤動作を防止し、安定に動作するスイッチング電源装置を提供する。

【解決手段】本発明のスイッチング電源装置において、スイッチング素子1とスイッチング素子1を駆動する制御回路3は同一の半導体チップ20上に形成されている。半導体チップ20はSOI基板であり、スイッチング素子1と制御回路3とは基板内の絶縁層126およびシリコン酸化膜が埋め込まれた分離溝127によって電気的に分離されている。

(もっと読む)

高密度二重平面デバイス

基板(10)上に形成された第1及び第2の自立型半導体本体(40N、40P)を有するMOSデバイスである。第1の自立型半導体本体(40N又は40P)の第1の部分は、第2の自立型半導体本体(40P又は40N)の第1の部分に対して非直交かつ非平行な向きに配置される。第1及び第2の自立型半導体本体(40N、40P)のこれらの部分は、それぞれ第1及び第2の結晶配向を有する。第1のゲート電極(60)は、第1の自立型半導体本体(40N又は40P)の第1の部分の少なくとも一部と非直角に交差し、第2のゲート電極(60)は、第2の自立型半導体本体(40P又は40N)の第1の部分の少なくとも一部と非直角に交差する。  (もっと読む)

(もっと読む)

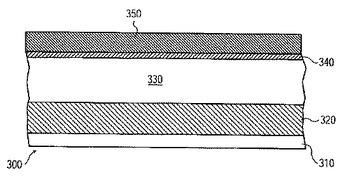

リンが注入されたポリシリコンのシート抵抗の減少

リンが注入されたポリシリコンのシート抵抗を減少するプロセスが存在する。一実施の形態において、MOSトランジスタ構造(300)が存在する。構造は、ゲート領域、ドレイン領域及びソース領域を有する。ゲート領域のシート抵抗を減少する方法(220)は、予め決定された温度で真性アモルファスシリコンをゲート領域に堆積する(221)。アモルファス化の種が、真性アモルファスシリコンに注入される(222)。その後、リンの種が、MOSトランジスタ構造のゲート領域に注入される(223)。この実施の形態の特徴は、アモルファス化の種としてのAr+の使用を含む。  (もっと読む)

(もっと読む)

半導体装置およびその作製方法

【課題】レーザビームが照射された領域全体に占める微結晶が形成される領域の割合を減らし、半導体膜に対して良好にレーザ照射を行うことができるレーザ照射装置を提供すること、およびレーザ照射方法を提供すること。

【解決手段】レーザ発振器101から出射したレーザ光104をスリット102を通過させることによって強度の弱い部分を遮断した後にミラー103で偏向させ、このレーザ光を凸型シリンドリカルレンズ105,106または凸型球面レンズを用いて任意の大きさにビームの整形をした後に照射面に照射する。

(もっと読む)

スタック状ヘテロドーピング周縁部及び徐々に変化するドリフト領域を備えた促進された表面電界低減化高耐圧P型MOSデバイス

基板(20)上に形成された高耐圧P型MOSデバイス(12)は、第2極性タイプのエピタキシャル層(22)内に形成された第1極性タイプのHVウエル(26)を有し、該基板上において少なくとも部分的にHVウエルの上部に1対のフィールド酸化領域(32、34)を有している。絶縁ゲート(40、42)が該基板上においてフィールド酸化領域の間に形成されている。スタック状のヘテロドーピングされた周縁部(50、52、60、62)がHVウエル内において両ゲートの外側端部に自己アラインメントして形成されている。第1極性タイプのバッファ領域(66)がHVウエル内において両ゲートの内側端部の間に自己アラインメントして形成されている。第2極性タイプのドリフト領域(68)がバッファ領域内において両ゲートの内側端部の間に自己アラインメントして形成されている。該ドリフト領域はドーパント濃度が徐々に変化する領域(104)を有し、これは第2極性タイプのドレイン領域(110)を含んでいる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明の目的は、ゲート長が高精度に制御され、かつ、ショートチャネル効果を抑制する半導体装置及びその製造方法を提供することである。

【解決手段】 第1のゲート電極膜17aと、第1のゲート電極膜17aのゲート長よりも長いゲート長を具備する第2のゲート電極膜20とを有する2段型ゲート電極20aを形成することにより、ゲート長が高精度に制御される。また、エクステンション領域21は第2のゲート電極膜20をマスクにして不純物導入がされるため、ショートチャネル効果を抑制することができる。

(もっと読む)

半導体製造装置の製造方法

【課題】

簡易な方法で同一半導体基板上に、ゲート絶縁膜の膜厚、又は閾値電圧が異なる3種類のMOSトランジスタを製造する方法を提供すること。

【解決手段】

本発明の半導体装置の製造方法は、同一半導体基板上に、所定厚さの第1ゲート絶縁膜を有する第1のMOSトランジスタと、第1ゲート絶縁膜よりも薄い第2ゲート絶縁膜を共通に有する第2及び第3のMOSトランジスタとを備え、第3のMOSトランジスタは、その閾値電圧が第2のMOSトランジスタより低い半導体装置の製造方法において、第1及び第3のMOSトランジスタの閾値電圧調整のために第1のイオン注入を行う工程と、第2のMOSトランジスタの閾値電圧調整のために第1のイオン注入とは注入条件の異なる第2のイオン注入を行う工程を備えることを特徴とする。

(もっと読む)

高移動性バルク・シリコンPFET

【課題】 従来のPFETに比べて減少されたシリコン面積および電力消費での高速のスイッチング速度をもつ改良されたPFETと、改良されたPFETと同時に製造されることができるNFETとの両方を提供すること。

【解決手段】 電界効果トランジスタ(100)及び電界効果トランジスタを製造する方法である。電界効果トランジスタは、ゲート誘電体層(155)の上面(170)に形成されたゲート電極(165)と、単結晶シリコン・チャネル領域(110)の上面(160)のゲート誘電体層と、Ge含有層(135)の上面の単結晶シリコン・チャネル領域と、単結晶シリコン基板(150)の上面のGe含有層と、単結晶シリコン基板の上面における第1誘電体層(215A)と第2誘電体層(215B)との間のGe含有層とを含む。

(もっと読む)

電界効果トランジスタ

【課題】 基板バイアス電圧を印加することなく、正確且つ確実な低温動作を実現する構成を有する電界効果トランジスタを提供する。

【解決手段】 本発明の実施の一形態に係る電界効果トランジスタは、300K以下の温度条件で動作することが想定された電界効果トランジスタであって、4.05未満の仕事関数WFnを有するゲート電極材により形成されたゲート電極を備えているnチャネル電界効果トランジスタを含むものである。また、本発明の実施の一形態に係る電界効果トランジスタは、5.17を超える仕事関数WFpを有するゲート電極材により形成されたゲート電極を備えているpチャネル電界効果トランジスタを含み得るものである。

(もっと読む)

半導体装置およびその製造方法

【課題】 p型MOSトランジスタおよびn型MOSトランジスタのオン電流を共に増加可能とすると共に、コンタクトの不良発生を防止する半導体装置およびその製造方法を提供する。

【解決手段】 シリコン基板11の第1領域13pに形成されたp型MOSトランジスタ14と、第2領域13nに形成されたn型MOSトランジスタ15と、第2領域13nには、シリコン基板11および素子分離領域12の一部の表面とゲート積層体34を覆う引っ張り応力を有する第2応力制御膜38と、第1領域13pのシリコン基板11および素子分離領域12の一部の表面とゲート積層体23を覆うと共に、第2領域の第2応力制御膜38を覆う、圧縮応力を有する第1応力制御膜26が形成される。第1応力制御膜26の膜厚t1、圧縮応力の大きさP1、第2応力制御膜38の膜厚t2、圧縮応力の大きさP2として、t1×P1<t2×P2の関係を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】 高いON電流を有し、しかも消費電力の低いCMOS回路を実現するためのMISトランジスタ構造を提供する。

【解決手段】 nチャネル型MISトランジスタ(Qn)およびpチャネル型MISトランジスタ(Qp)のそれぞれのゲート絶縁膜5は、酸化ハフニウム(HfO2)膜で構成されている。また、nチャネル型MISトランジスタ(Qn)のゲート電極6は、Ni(ニッケル)シリサイド膜で構成され、pチャネル型MISトランジスタ(Qp)のゲート電極7は、Pt(プラチナ)膜で構成されている。この構造により、ゲート電極6、7のフェルミレベルピニングが生じないので、nチャネル型MISトランジスタ(Qn)およびpチャネル型MISトランジスタ(Qp)のそれぞれのしきい値電圧の上昇が抑制される。

(もっと読む)

MIS型FETの製造方法

【課題】 ダマシン構造のゲート電極を備えたMIS型FETにおいて、高い電流駆動能力と低消費電力とを有するMIS型FETの製造方法を提供する。

【解決手段】 シリコン基板1の表面部にソース/ドレイン拡散層(14,15)を形成し、その表面にシリサイド層17を形成する。そして、ゲート側壁(12,13)で区画されたゲート開口溝20底部のシリコン基板1表面に、550℃以下の温度で界面層21を形成し、ゲート開口溝20内、界面層21および層間絶縁膜19を被覆するようにHigh−k膜22を堆積させ、酸化性雰囲気中550℃以下の温度での熱処理を施す。そして、全面を被覆する導電体膜23およびメタル膜24を形成した後、CMP法により層間絶縁膜19上の不要部分を研磨除去しダマシン構造のメタルゲート電極を備えたMIS型FETを形成する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ポリシリコン抵抗に導入された不純物の外方拡散を抑制することができる半導体装置の製造方法及び半導体装置を提供する。

【解決手段】この半導体装置の製造方法は、ゲート電極4a及びポリシリコン抵抗4cそれぞれを形成する工程と、ゲート電極4a上及びポリシリコン抵抗4c上に、絶縁膜を形成する工程と、絶縁膜上に、ポリシリコン抵抗4cの上方に位置するレジストパターン12を形成する工程と、レジストパターン12をマスクとして絶縁膜をエッチバックすることにより、ゲート電極4aの側壁にサイドウォール5aを形成するとともに、ポリシリコン抵抗4c上に拡散防止膜5cを形成する工程とを具備する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 パンチスルー現象を抑えた半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法が、シリコン基板を準備する工程と、シリコン基板に、ゲート電極と、ゲート電極の両側に配置されるソース領域およびドレイン領域を形成し、ソース領域とドレイン領域で挟まれた領域をチャネル領域とするチャネル領域形成工程と、ソース領域とドレイン領域を覆う金属膜を形成する金属膜形成工程と、金属膜と、ソース領域およびドレイン領域とを反応させ、ソース領域およびドレイン領域の表面に金属シリサイド層を形成するシリサイド工程と、金属シリサイド層をイオン注入マスクに用いてチャネル領域にイオンを注入し、ソース領域およびドレイン領域とは導電型の異なるパンチスルーストッパ領域を、ソース領域およびドレイン領域に隣接するように形成する注入工程とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】 信頼性を向上することのできる半導体装置およびその製造方法を提供する。

【解決手段】 本発明の半導体装置は、メモリセル領域と周辺回路領域とを有する半導体装置であって、シリコン基板1と、シリコン基板1の表面に形成されたシリコン酸化膜6よりなる素子分離6a,6bとを備えている。メモリセル領域における素子分離6aの深さd1は、周辺回路領域における素子分離6bの深さd2よりも浅く、メモリセル領域における素子分離6aの分離高さh1と、周辺回路領域における素子分離6bの分離高さh2とがほぼ同じである。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】製造工程の数を少なくすることが出来る半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、第1導電型素子領域1b、第2導電型素子領域1a、及び素子分離膜2上に、第1導電型の不純物が導入されたポリシリコン膜4を形成し、ポリシリコン膜4をパターニングすることにより、第1ゲート電極4b、第2ゲート電極4a、及び抵抗素子4cを形成する。第1ゲート電極4b及び抵抗素子4cを第1のマスクで覆い、第2導電型の不純物を注入することにより、第2の不純物領域を形成するとともに、第2ゲート電極4aを低抵抗化する。また、第2導電型素子領域1a及び抵抗素子4cを第2のマスクで覆い、第1導電型の不純物を注入することにより、第1の不純物領域を形成するとともに、第1ゲート電極4bを低抵抗化する。

(もっと読む)

絶縁ゲート型電界効果トランジスタの製法

【課題】微細なゲート電極を有するLDD(Lightly Doped Drain)構造の絶縁ゲート型電界効果トランジスタを製造する方法において、製造歩留りを向上させる。

【解決手段】P型ウェル領域14の表面に素子孔を有するフィールド絶縁膜16を形成した後、素子孔内の半導体表面にゲート絶縁膜20を形成する。絶縁膜20の上に破線で示すようにポリシリコン等のゲート電極層24を形成した後、電極層24及び絶縁膜20の積層と絶縁膜16とをマスクとするイオン注入処理によりN+型ソース領域28及びN+型ドレイン領域30を形成する。等方性エッチング処理により電極層24を実線で示すように細く且つ薄くした後、電極層24及び絶縁膜20の積層と絶縁膜16とをマスクとするイオン注入処理によりN−型ソース領域32及びN−型ドレイン領域34を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 ポリシリコンからなるゲート電極の空乏化を防ぐことができる半導体装置及びその製造方法を得る。

【解決手段】 半導体基板に形成された第1の導電型のウェル領域と、ウェル領域の表面近くに形成された、第1の導電型とは反対の導電型である第2の導電型のソース・ドレイン領域と、ウェル領域上に形成された、金属酸化物からなるゲート絶縁膜と、ゲート絶縁膜上に形成された、第1の導電型のポリシリコンからなるゲート電極とを有する。

(もっと読む)

高誘電体膜、この高誘電体膜を用いた電界効果トランジスタおよび半導体集積回路装置ならびに高誘電体膜の製造方法

【課題】ハフニウムを含む高誘電体膜からなるゲート絶縁膜を備えた電界効果トランジスタにおいて、シリコン基板とゲート絶縁膜との界面における界面準位密度を低減し、ゲート絶縁膜におけるキャリアの移動度を高めることにある。

【解決手段】HfSiONまたはHfAlOxなどのハフニウムを含む薄膜に対して、自然界に存在する重水素と水素との比率よりも大きな比率で重水素を含有させた高誘電率の第2絶縁膜8を電界効果トランジスタのゲート絶縁膜として使用する。第2絶縁膜8は、ALD法により成膜することが好ましい。

(もっと読む)

半導体装置の製造方法

【課題】 LDD構造を有し所定の膜厚の第1のゲート酸化膜を有する第1の半導体素子と、前記第1のゲート酸化膜より厚い膜厚の第2のゲート酸化膜を有する第2の半導体素子とを、簡単な製造工程によって同一基板上に形成する。

【解決手段】 高耐圧の第2の半導体素子の第2のゲート酸化膜の形成と同時に、第1の半導体素子のLDD構造の形成に必要なサイドウォールを形成する。サイドウォール形成プロセスを高耐圧半導体素子に特有な膜厚の厚いゲート酸化膜の形成プロセスと共通化することによって、サイドウォール形成工程を別途設ける必要がなくなり、製造工程を省略することができる。

(もっと読む)

2,321 - 2,340 / 2,469

[ Back to top ]