Fターム[5F048BC06]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ソース・ドレイン (8,322) | 追加領域の形成 (3,324) | LDD (2,469)

Fターム[5F048BC06]に分類される特許

2,401 - 2,420 / 2,469

キャパシタと好ましくはプレーナ型のトランジスタとを有する集積回路構造およびその製造方法

プレーナ型であることが好ましいトランジスタ(142)とキャパシタ(144)とを有する集積回路構造(140)が開示されている。キャパシタ(44)の下部電極は、トランジスタ(142)のチャネル領域と共に、1つのSOI基板に配置されている。回路構造(140)は、簡単に製造でき、優れた電子特性を有している。  (もっと読む)

(もっと読む)

高誘電率のゲート絶縁膜を有する半導体装置及びそれの製造方法

【課題】 本発明はゲート構造物として高誘電率を有する物質として、高誘電率を有する物質からなるゲート絶縁膜を含む半導体装置及びその製造方法に関する。

【解決手段】 半導体装置及びその製造方法において、基板上に形成され、ハフニウムシリコン酸化物含有固体物質を含むゲート絶縁膜パターンと前記ゲート絶縁膜パターン上に形成される第1ゲート導電膜パターンを含むゲート構造物及び前記ゲート構造物と隣接する基板の表面部位に配置されており、n型不純物がドーピングされたソース/ドレイン領域を含むことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 安定した低抵抗のシリサイド膜を形成する技術を提供する。

【解決手段】 半導体基板1上にゲート絶縁膜5を形成する工程、ゲート絶縁膜5上にシリコン膜7を形成する工程、シリコン膜7と半導体基板1との表面にBF2イオンおよびBイオンを注入し、pチャネル型MISトランジスタQpのゲート電極11pと高濃度n型半導体領域15からなるソース/ドレインとを形成する工程、ゲート電極11pの上部に第1コバルトシリサイド膜を形成し、ソース/ドレインの上部に第2コバルトシリサイド膜を形成する工程を有する。

(もっと読む)

半導体装置およびその製造方法

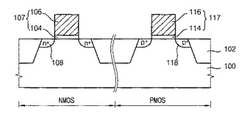

【課題】 ゲート絶縁膜に生じるリーク電流を抑制でき、高いトランジスタ特性を維持したまましきい値電圧の制御を個々のトランジスタごとに実行することができる相補型MISFETを提供することである。

【解決手段】 相補型のトランジスタのうちのn型トランジスタのゲート絶縁膜8とp型トランジスタのゲート絶縁膜9との対比において、膜厚および組成のうち少なくともいずれか一方が異なる。それにより、ゲート絶縁膜のしきい値電圧が個々のトランジスタごとに異なる。

(もっと読む)

半導体装置およびその製造方法

【課題】STIを備えた半導体装置において、トランジスタ特性の劣化を招かない構成を有する半導体装置およびその製造方法を提供する。

【解決手段】本発明の半導体装置は、主面を複数の素子領域A1〜A3に区分する分離領域に形成されたトレンチ分離構造を有するSi基板1を備え、素子領域A2、A3にはエピタキシャル層が選択的に成長させられている。この半導体装置は、素子領域A1に形成されたチャネル領域を有する第1のNチャネル型MOSトランジスタと、エピタキシャル層に形成されたチャネル領域を有する第2のNチャネル型MOSトランジスタおよびPチャネル型MOSトランジスタとを備えている。第2のNチャネル型MOSトランジスタのチャネル領域が形成されているエピタキシャル層のチャネル長方向サイズは、第1のNチャネル型MOSトランジスタのチャネル領域が形成されている素子領域A1のチャネル長方向サイズよりも小さい。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】微細化してもウエル抵抗を上昇させず、優れたラッチアップ耐性を有する半導体装置及びその製造方法を提供する。

【解決手段】P型の半導体基板1aに半導体基板1aの主表面から深さ方向に濃度を増加し不純物濃度ピーク6を有するNウエル7及び半導体基板1aの主表面から深さ方向に濃度を増加し不純物濃度ピーク10を有するPウエル11を形成する。このとき、Nウエル7及びPウエル11は、N型不純物のイオン注入エネルギー及びP型不純物のイオン注入エネルギーを調整することによりPウエル11の不純物濃度ピーク10がNウエル7の不純物濃度ピーク6よりも深くなるように形成される。これにより、Nウエルの抵抗を低減でき、Nウエルの電気的に有効となる不純物が確保でき、従来のレトログレードウエルより優れたラッチアップ耐性となる。特に、ウエル領域が微細化しても有効となる不純物が確保できるため、微細化に適した半導体装置となる。

(もっと読む)

メモリ

【課題】メモリセルサイズを小さくすることが可能なメモリを提供する。

【解決手段】このメモリでは、選択トランジスタ11aと選択トランジスタ11bとは、ソース領域17を共有し、選択トランジスタ11aのゲート電極19aと選択トランジスタ11bのゲート電極19bとは、ワード線7と一体的に設けられ、かつ、平面的に見て、メモリセル9の形成領域におけるn型不純物領域14の延びる方向に対して斜め方向に延びるとともに、選択トランジスタ11aおよび11bの形成領域におけるn型不純物領域14と交差するように配置され、選択トランジスタ11aと選択トランジスタ11bとでn型不純物領域14を分割している。

(もっと読む)

半導体装置

【課題】

酸化シリコン層、窒化シリコン層の積層ライナを備えたSTIを有し、帯電を低減できる半導体装置およびその製造方法を提供する。

【解決手段】

半導体装置は、シリコン基板と、前記シリコン基板の表面から下方に向かって形成され、前記シリコン基板の表面に活性領域を画定するトレンチと、前記トレンチの内壁を覆う酸化シリコン層の第1ライナ層と、前記第1ライナ層の上に形成された窒化シリコン層の第2ライナ層と、前記第2ライナ層の上に形成され、前記トレンチを埋める絶縁物の素子分離領域と、前記活性領域に形成されたpチャネルMOSトランジスタと、前記pチャネルMOSトランジスタを覆って,前記シリコン基板上方に形成され,紫外光遮蔽能を有さない窒化シリコン層のコンタクトエッチストッパ層と、前記コンタクトエッチストッパ層の上方に形成され、紫外光遮蔽能を有する窒化シリコン層の遮光膜と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極端部のリーク電流の発生を抑制し、かつ、ソース/ドレイン拡散層形成時のイオン注入において、基板に注入される不純物のドーズ量の低下を抑制する。

【解決手段】半導体装置は、半導体基板10と、この半導体基板10上に形成された窒素を含むゲート絶縁膜25と、このゲート絶縁膜25上に選択的に形成されたゲート電極27と、このゲート電極27の側壁に形成された酸化膜28とを具備し、ゲート絶縁膜25は、ゲート電極27の中央部下に位置する第1の部分とゲート電極27の端部下に位置する第2の部分とを有し、ゲート絶縁膜25の第2の部分は、ゲート電極側に突出する第1の突出部と半導体基板側に突出する第2の突出部とを有し、ゲート絶縁膜25の第1の部分の上面の高さと第1の突出部のピークの高さとの間の距離は、ゲート絶縁膜25の第1の領域の下面の高さと第2の突出部のピークの高さとの間の距離よりも大きく、ゲート絶縁膜25は、0.1%乃至10%の窒素を含む酸化膜である。

(もっと読む)

半導体装置及びその製造方法

【課題】 微細化が進められてもトランジスタのオン電流を十分に確保することができる半導体装置及びその製造方法を提供する。

【解決手段】 全面に高電圧トランジスタ用のゲート絶縁膜4を形成した後、低電圧領域内に存在するゲート絶縁膜4を除去する際に、活性領域3が露出した時点でエッチングを終了するのではなく、低電圧領域内において、活性領域3の表面よりも素子分離絶縁膜2の表面が、例えば15nm程度低くなるまでオーバーエッチングを行う。次に、低電圧領域内の活性領域3に対して高温急速水素加熱処理を行う。この結果、低電圧領域内の活性領域3の表面から自然酸化膜が除去され、平坦度が増すと共に、角部が丸まる。

(もっと読む)

半導体装置及びその製造方法

【課題】 MIS構造のトランジスタの微細化と、ドレイン出力アナログ信号のソースへのリークの低減とを両立できるようにした半導体装置及びその製造方法を提供する。

【解決手段】 MOSトランジスタ100を微細化しても寄生抵抗増大の副作用を伴わせないようにするために、LDD構造のソース60及びドレイン70を非対称構造にする。つまり、N−−層73の不純物濃度は、Esatの低減を目的に低くしておく。また、N−層63の不純物濃度は、寄生抵抗低減を目的にN−−層73よりも高くする。さらに、シリコン基板1のソース60側だけにポケットインプラを行って、P−層80を形成する。これにより、アナログCMOSとしては短チャネルに部類される0.35[μm]ゲート長トランジスタにおいて、ドレイン電圧誘起Vth低下現象(DIBL)と、ピンチオフ点でのチャネル変調効果(CLM)とを同時に低減可能である。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】相対的に高いON電流と、相対的に低いしきい値電圧とを有するMISFETを形成する。

【解決手段】ゲート溝19の内壁に沿って高誘電率膜20を形成し、高誘電率膜20上に相対的に低い温度により酸化する金属膜を積層し、金属膜に不純物をイオン注入した後、相対的に低い温度で金属膜を酸化させて酸化金属膜を形成すると同時に、不純物を高誘電率膜20と酸化金属膜との界面に偏析させる。次いで、酸化金属膜を実質的に全て除去した後、改めて相対的に抵抗の低い金属膜をゲート溝19の内部に埋め込むことにより、金属ゲート24を形成する。

(もっと読む)

埋設導電層を備えた高電圧トランジスタ

【課題】埋設導通層を備えた低オン抵抗値の横方向高電圧電界効果トランジスタ(HVFET)を提供する。

【解決手段】P型基板に形成されたN型ウエル内にP型埋設層領域を設け、これをN型ウエル領域に形成された第1のP型ドレイン拡散領域によってドレイン電極に接続すると共に、PMOSゲート領域の一端で表面から下方に延びる第2のP型ドレイン拡散領域にも接続し、ソース電極に接続されるP型ソース拡散領域でゲート領域の他端を定める。

(もっと読む)

改良した歪みシリコンCMOSデバイスおよび方法

【課題】 デバイス・チャネルに一軸性歪みを生成してキャリア移動度を向上させた半導体デバイスを提供する。

【解決手段】 本発明は、半導体デバイスのデバイス・チャネルに一軸性歪みを生成する半導体デバイスおよびその形成方法を提供する。一軸性歪みは、引張り性または圧縮性とすることができ、デバイス・チャネルに平行な方向である。一軸性歪みは、歪み誘発ライナ、歪み誘発ウェル、またはそれらの組み合わせによって、二軸性歪み基板表面において生成することができる。一軸性歪みは、歪み誘発ウェルおよび歪み誘発ライナの組み合わせによって、緩和基板において生成することも可能である。また、本発明は、歪み誘発分離領域によって二軸性歪みを増大させるための手段も提供する。更に、本発明が提供するCMOSデバイスにおいては、CMOS基板のデバイス領域を別個に処理して、圧縮性または引張り性の一軸性歪み半導体表面を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】 リーク電流を増加させることなく半導体増幅装置の効率を向上させる。

【解決手段】 SOI基板20のドライバ段LDMOSFET形成領域20Aおよび出力段LDMOSFET形成領域20BのそれぞれにLDMOSFETが形成されている。LDMOSFETのソースは、p-型半導体層23および絶縁層22を貫通するn型打抜き層25を介して基板21および裏面電極72に電気的に接続されている。n型打抜き層25とp-型半導体層23およびp型ウエル28とは、PN接合が形成されることによって電気的に分離されている。p型ウエル28に形成されたp+型半導体領域41は、プラグ53cを介してベース電極54cが電気的に接続されている。LDMOSFETのベース電位とソース電位とは独立に制御され、LDMOSFETのオン時にはベース電位をソース電位よりも高くし、オフ時にはベース電位をソース電位と等しくする。

(もっと読む)

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】 MONOS型トランジスタを有する不揮発性半導体記憶装置の高性能化を推進する。

【解決手段】 MONOS型不揮発性メモリのメモリセル(MC1)は、コントロールトランジスタ(C1)とメモリトランジスタ(M1)とで構成されている。コントロールトランジスタ(C1)のコントロールゲート8はn型多結晶シリコン膜からなり、酸化シリコン膜からなるゲート絶縁膜6上に形成されている。また、メモリトランジスタ(M1)のメモリゲート9はn型多結晶シリコン膜からなり、コントロールゲート8の一方の側壁に配置されている。メモリゲート9はドープド多結晶シリコン膜からなり、アンドープドシリコン膜に不純物をイオン注入して形成した多結晶シリコン膜からなるコントロールゲート8よりもシート抵抗が低い。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体装置の小型化を可能にする。

【解決手段】 基板21上のエピタキシャル層22に、ゲート電極32と、n-型オフセットドレイン領域35、n型オフセットドレイン領域39およびn+型ドレイン領域42からなるドレイン領域と、n-型ソース領域36およびn+型ソース領域43からなるソース領域とを有するLDMOSFEを形成するとともに、n型ウエル27上に複数のショットキ電極52を形成してショットキ電極52およびn型ウエル27間にショットキ接合を形成することでショットキダイオード素子を形成している。複数のショットキ電極52はプラグ63およびアノード電極74を介して互いに電気的に接続されている。複数のショットキ接合部の間および両側に設けられたn+型半導体領域44は、プラグ63およびカソード電極73を介して互いに電気的に接続されている。

(もっと読む)

半導体装置の製造方法

【課題】p型トランジスタの動作速度を高め、n型トランジスタとの動作速度の均衡がとれた半導体装置の製造方法を提供する。

【解決手段】p−MOS領域30aのソース/ドレイン領域にSiGe膜からなる圧縮応力印加部20を形成し、その後にp−MOS領域30aおよびn−MOS領域30bに不純物注入を行い、浅い接合領域22a、22bおよび深い接合領域23a、23bを形成する。SiGe膜を形成する際の加熱により浅い接合領域22a、22bの不純物がゲート絶縁膜15の直下に拡散することを防止し、短チャネル効果を防止すると共に、p−MOSトランジスタ13aのチャネル領域の正孔移動度を高め、n−MOSトランジスタ13bの動作速度との均衡により、相補型の半導体装置10の総合的な動作速度を高める。

(もっと読む)

pinダイオードを備えた集積回路構造およびその製造方法

特に、pinフォトダイオード(14)と、バイポーラトランジスタ(58)の高ドープされた接続領域(62)とを含んだ集積回路構造(10)を開示する。高度な制御方法により、pinダイオード(14)の非常に深い中間領域(30)を、オートドーピングを用いずに形成できる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体装置の信頼性や性能を向上させる。

【解決手段】 CMISFETを有する半導体装置において、nチャネル型MISFET30aのゲート電極31aを、NiとNiの仕事関数よりも低い仕事関数を有する金属とSiとを含有する金属シリサイドにより形成し、pチャネル型MISFET30bのゲート電極31bを、NiとNiの仕事関数よりも低い仕事関数を有する金属とSiとを含有する金属シリサイドにより形成する。ゲート電極31aにNiの仕事関数よりも低い仕事関数を有する金属を含有させ、ゲート電極31bにNiの仕事関数よりも高い仕事関数を有する金属を含有させることで、nチャネル型MISFET30aとpチャネル型MISFET30bの両方で低しきい値電圧化が可能になる。また、ゲート電極31a,31bはノンドープのシリコン膜を金属膜と反応させることで形成される。

(もっと読む)

2,401 - 2,420 / 2,469

[ Back to top ]