Fターム[5F048BC06]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ソース・ドレイン (8,322) | 追加領域の形成 (3,324) | LDD (2,469)

Fターム[5F048BC06]に分類される特許

2,421 - 2,440 / 2,469

半導体装置およびその製造方法

【課題】 半導体装置の小型化を可能にする。

【解決手段】 基板21上のエピタキシャル層22に、ゲート電極32と、n-型オフセットドレイン領域35、n型オフセットドレイン領域39およびn+型ドレイン領域42からなるドレイン領域と、n-型ソース領域36およびn+型ソース領域43からなるソース領域とを有するLDMOSFEを形成するとともに、n型ウエル27上に複数のショットキ電極52を形成してショットキ電極52およびn型ウエル27間にショットキ接合を形成することでショットキダイオード素子を形成している。複数のショットキ電極52はプラグ63およびアノード電極74を介して互いに電気的に接続されている。複数のショットキ接合部の間および両側に設けられたn+型半導体領域44は、プラグ63およびカソード電極73を介して互いに電気的に接続されている。

(もっと読む)

半導体装置の製造方法

【課題】p型トランジスタの動作速度を高め、n型トランジスタとの動作速度の均衡がとれた半導体装置の製造方法を提供する。

【解決手段】p−MOS領域30aのソース/ドレイン領域にSiGe膜からなる圧縮応力印加部20を形成し、その後にp−MOS領域30aおよびn−MOS領域30bに不純物注入を行い、浅い接合領域22a、22bおよび深い接合領域23a、23bを形成する。SiGe膜を形成する際の加熱により浅い接合領域22a、22bの不純物がゲート絶縁膜15の直下に拡散することを防止し、短チャネル効果を防止すると共に、p−MOSトランジスタ13aのチャネル領域の正孔移動度を高め、n−MOSトランジスタ13bの動作速度との均衡により、相補型の半導体装置10の総合的な動作速度を高める。

(もっと読む)

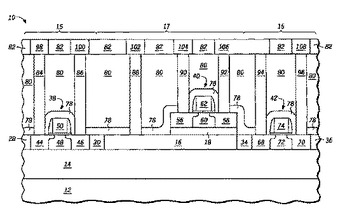

pinダイオードを備えた集積回路構造およびその製造方法

特に、pinフォトダイオード(14)と、バイポーラトランジスタ(58)の高ドープされた接続領域(62)とを含んだ集積回路構造(10)を開示する。高度な制御方法により、pinダイオード(14)の非常に深い中間領域(30)を、オートドーピングを用いずに形成できる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体装置の信頼性や性能を向上させる。

【解決手段】 CMISFETを有する半導体装置において、nチャネル型MISFET30aのゲート電極31aを、NiとNiの仕事関数よりも低い仕事関数を有する金属とSiとを含有する金属シリサイドにより形成し、pチャネル型MISFET30bのゲート電極31bを、NiとNiの仕事関数よりも低い仕事関数を有する金属とSiとを含有する金属シリサイドにより形成する。ゲート電極31aにNiの仕事関数よりも低い仕事関数を有する金属を含有させ、ゲート電極31bにNiの仕事関数よりも高い仕事関数を有する金属を含有させることで、nチャネル型MISFET30aとpチャネル型MISFET30bの両方で低しきい値電圧化が可能になる。また、ゲート電極31a,31bはノンドープのシリコン膜を金属膜と反応させることで形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】静電破壊耐性を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極とドレイン領域とソース領域とを有する半導体装置であって、ドレイン領域は、ゲート電極の第1の側に形成された第1導電型の第1の不純物拡散領域18aと;第1の不純物拡散領域より深く形成された第1導電型の第2の不純物拡散領域20aと;第1の不純物拡散領域より浅く形成され、不純物拡散層より不純物濃度が高い第1導電型の第3の不純物拡散領域28a、28bと;第3の不純物拡散領域上に形成され、ドレインコンタクト部22Dに接続されるシリサイド膜32a、32bとを有し、ドレインコンタクト部とサイドウォール絶縁膜との間にシリサイド膜が形成されていない領域が存在しており、ドレインコンタクト部の下方の半導体基板内に第2の不純物拡散領域が形成されていない。

(もっと読む)

半導体装置及びその製造方法

【課題】MOS−FETの駆動力を向上させる高性能な半導体装置及びその製造方法を提供すること。

【解決手段】CMOS−FET回路を備える半導体装置において、NMOS形成領域周辺の素子分離膜(102)の一部に設けられ引張応力を有する引張応力膜(119)と、PMOS形成領域周辺の素子分離膜(102)の一部に設けられ圧縮応力を有する圧縮応力膜(120)と、の少なくとも一方を備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体装置の性能や信頼性を向上させる。

【解決手段】 CMISFETを有する半導体装置において、nチャネル型MISFET30aのゲート電極31aは、P、AsまたはSbをドープしたシリコン膜をNi膜と反応させることで形成されたニッケルシリサイド膜からなり、pチャネル型MISFET30bのゲート電極31bは、ノンドープのシリコンゲルマニウム膜をNi膜と反応させることで形成されたニッケルシリコンゲルマニウム膜からなる。ゲート電極31aの仕事関数はP、AsまたはSbをドープすることによって制御され、ゲート電極31bの仕事関数はGe濃度を調節することによって制御される。

(もっと読む)

基板への相互接続を有する集積回路およびその製造方法

ソース/ドレイン(20)とゲート(26)との間の接点(32)が、ゲート誘電体(46)の選択部分(35)へ埋設物を注入することによりゲート誘電体(46)の選択部分(35)を導電性にすることで行われる。ゲート材料は集積回路全体(10)の上の層に位置する。ゲート(26)がソース/ドレイン(20)に接続する領域(32)が識別され、この識別位置(35)においてゲート誘電体(46)が導電性となるよう埋設物が注入される。ソース/ドレイン(20)が導電性ゲート誘電体(35)のそのような導電性領域の下を延び、該位置で埋設物が注入されたゲート誘電体(35)がゲート(26)をソース/ドレイン(20)に短絡するように、ソース/ドレイン(20)は形成される。これによって集積回路(10)上のスペースが節約され、相互接続層の必要性が低減され、露出したシリコン基板上にポリシリコンを堆積およびエッチングさせることに付随する問題を回避することができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 熱処理を最小限に抑えることにより、高誘電率ゲート絶縁膜の結晶化を防止する。

【解決手段】 シリコン基板1上にHfAlOx膜5とポリシリコンゲルマニウム膜6を積層する。ポリシリコンゲルマニウム膜6にボロンイオン7を注入した後、パターニングしてゲート電極6aを形成する。ゲート電極6aをマスクとしてエクステンション領域形成用のボロンイオン9を注入した後、ゲート電極6a側壁にサイドウォール12を形成する。サイドウォール12及びゲート電極6aをマスクとしてソース/ドレイン領域形成用のボロンイオン13を注入する。熱処理を行うことにより、ゲート電極6aにおいてボロンイオン7を拡散させると共に、基板1においてボロンイオン9,13を活性化させてエクステンション領域10a及びソース/ドレイン領域14aを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 Bモード故障とシリサイド未形成による動作不良の双方を解消した半導体装置を提供する。

【解決手段】 素子分離領域により画成された第1および第2の素子領域を有する基板と、前記第1の素子領域に形成された第1のポリシリコンゲート電極を有する第1の電界効果トランジスタと、前記第2の素子領域に形成された第2のポリシリコンゲート電極を有する第2の電界効果トランジスタと、前記第1のポリシリコンゲート電極と前記第2のポリシリコンゲート電極とを結んで前記素子分離領域上を延在するポリシリコンパターンと、前記第1のポリシリコンゲート電極の表面および前記第2のポリシリコンゲート電極の表面、さらに前記ポリシリコンパターンの表面に形成され、前記第1のポリシリコンゲート電極から前記第2のポリシリコンゲート電極まで、前記ポリシリコンパターン上を延在するシリサイド層とよりなる半導体装置において、前記シリサイド層は前記ポリシリコンパターン上において層厚が増大した厚膜部を含み、前記厚膜部では、前記シリサイド層の表面が上方に突出する。

(もっと読む)

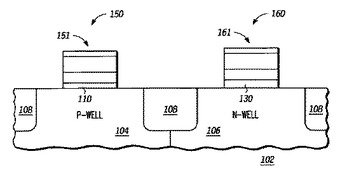

複数の半導体層を備えた半導体デバイス

半導体デバイス構造(10)では、N及びPチャネルトランジスタキャリア移動度を別々に最適化するため、二つの半導体層(16、20)が使用される。これを決定する導電特性は、半導体の材料の種類、結晶面、配向性及び歪みの組み合わせである。シリコンゲルマニウムの半導体材料、圧縮性歪み、(100)の結晶面及び<100>の配向性を特徴とする導電特性の場合、Pチャネルトランジスタ(38)においてホール移動度が向上する。また、結晶面は(111)であってもよく、この場合、配向性は重要ではない。N型伝導に適した基板は、P型伝導に適した(又は最適)基板とは異なる。Nチャネルトランジスタ(40)は、好ましくは、引っ張り歪み、シリコン半導体材料及び(100)面を有する。別の半導体層(16、20)では、N及びPチャネルトランジスタ(38、40)はいずれもキャリア移動度に対し最適化される。  (もっと読む)

(もっと読む)

半導体基板及びその製造方法

【課題】表面上に引っ張り応力を有する層間絶縁膜等の絶縁膜が形成された半導体基板において、反りを抑制しうる半導体基板及びその製造方法を提供する。

【解決手段】シリコンウェーハ10と、シリコンウェーハ10の表面上に形成された層間絶縁膜に埋め込まれた多層配線12と、シリコンウェーハ10の裏面に形成され、引っ張り応力を有する絶縁膜であるシリコン窒化膜16bとを有している。シリコン窒化膜16bにより、多層配線12が埋め込まれた層間絶縁膜によりシリコンウェーハ10に与えられる応力が緩和され、シリコンウェーハ10の反りが抑制される。したがって、半導体基板の搬送系における吸着不良の発生を防止することができる。

(もっと読む)

改善されたしきい電圧およびフラットバンド電圧の安定性を有する相補型金属酸化膜半導体(CMOS)構造およびそれを形成する方法(高k誘電体によるCMOSデバイス形成におけるしきい電圧制御を達成するためのバリア層の選択的実装)

【課題】 改善されたしきい電圧およびフラットバンド電圧の安定性を有するCMOS構造を形成する方法およびそれにより生産されたデバイスを提供することにある。

【解決手段】 発明の方法は、nFET領域とpFET領域とを有する半導体基板を設けるステップと、高k誘電体の上に絶縁中間層を含む誘電体スタックを半導体基板の上に形成するステップと、pFET領域から絶縁中間層を除去せずに、nFET領域から絶縁中間層を除去するステップと、pFET領域内に少なくとも1つのゲート・スタックを設け、nFET領域内に少なくとも1つのゲート・スタックを設けるステップとを含む。絶縁中間層はAlNまたはAlOxNyにすることができる。高k誘電体は、HfO2、ハフニウム・シリケート、またはハフニウム酸窒化シリコンにすることができる。絶縁中間層は、HCl/H2O2過酸化水素溶液を含むウェット・エッチングによりnFET領域から除去することができる。

(もっと読む)

相異なるチャネル領域に相異なるよう調整された内在応力を有するエッチストップ層を形成することによって、相異なる機械的応力を生成するための技術

コンタクトエッチストップ層(116)を設けることによって、異なるトランジスタ型(100N),(100P)のチャネル領域内の応力を効果的に制御することができる。その際、コンタクトエッチストップ層(116)の引張応力部分と圧縮応力部分は、ウェット化学エッチング、プラズマエッチング、イオン注入、プラズマ処理などの十分に確立されたプロセスによって得ることができる。このため、プロセスを著しく複雑にすることなく、トランジスタ(100N),(100P)の性能を大きく改善することができる。  (もっと読む)

(もっと読む)

独立して歪むNチャネル型及びPチャネル型トランジスタ

第一ウェハ上に形成された第一の複数のトランジスタと、第二ウェハ上に形成された第二の複数のトランジスタとを備えた集積回路。第一トランジスタのうち少なくとも実質的に大部分が第一導電型であり、第二の複数のトランジスタのうち少なくとも実質的に大部分が第二導電型である。ウェハ同士が結合された後、第二ウェハの一部が除去されて、第二の複数のトランジスタのチャネルの歪みの圧縮性が、第一の複数のトランジスタのチャネルの歪みの圧縮性よりも高くなる。  (もっと読む)

(もっと読む)

半導体装置及びそのような装置を製造する方法

本発明は、基板(11)と、第1及び第2半導体層(2、3)を連続して備える半導体層構造体と第1導電型の表面領域を有するシリコンの半導体本体(1)とを備え、表面領域には第1導電型と逆の第2導電型のチャネルを有する電界効果トランジスタ(M)が設けられ、表面領域は、電界効果トランジスタ(M)のための第2導電型のソース及びドレイン領域(4A、4B)と、第2半導体層(3)の一部分を形成する、前記ソース及びドレイン領域間に挿入されたより低いドーピング濃度を有するチャネル領域(3A)と、チャネル領域(3A)の下に埋め込まれ、チャネル領域(3A)のものよりはるかに高いドーピング濃度を有し、第1半導体層(2)の一部分を形成する第1導電型の埋め込み半導体領域(2A)とが設けられる、半導体装置(10)に関する。本発明によれば、半導体本体(1)には、電界効果トランジスタ(M)だけでなく、それぞれ第2、第1及び第2導電型のエミッタ、ベース及びコレクタ領域(5A、5B、5C)を有するバイポーラ・トランジスタ(B)も設けられ、エミッタ領域(5A)は第2半導体層(3)内に形成され、ベース領域(5B)は第1半導体層(2)内に形成される。このようにして、高周波用途に非常に適した、本発明による方法を使用して製造するのが容易なBi(C)MOS IC(10)が得られる。好ましくは、第1半導体層(2)はSi−Geを備えデルタドープされるが、第2半導体層(3)はひずみSiを備える。  (もっと読む)

(もっと読む)

2種類の金属酸化物ゲート誘電体に1種類の金属ゲート電極が設けられる半導体プロセス及び集積回路

半導体形成プロセスでは、第1及び第2トランジスタを第1及び第2ウェル領域のそれぞれの上に形成し、第1トランジスタは第1ゲート誘電体を有し、そして第2トランジスタは第1ゲート誘電体とは異なる第2ゲート誘電体を有する。第1トランジスタは第1ゲート電極を有し、そして第2トランジスタは第2ゲート電極を有する。第1及び第2ゲート電極は組成が同じである。第1ゲート誘電体及び第2ゲート誘電体は共に、酸化ハフニウム及び酸化アルミニウムのような高k誘電体を含むことができる。第1及び第2ゲート電極は共に、ゲート電極層を該当するゲート誘電体の上に含む。ゲート電極層は、TaSiN及びTaCのいずれかであることが好ましい。第1及び第2ゲート電極は共に、導電層をゲート電極層の上に含むことができる。このような一の実施形態では、導電層はポリシリコン及びタングステンからなる。  (もっと読む)

(もっと読む)

分離トレンチ

分離トレンチ(209)をウェハ(201)に形成するプロセスである。このプロセスでは、(例えば、異方性堆積法により)第1誘電体材料(307)をトレンチ(209)の中に堆積させ、次に第2誘電体材料(309)を(例えば、異方性堆積法により)トレンチ(209)内の第1誘電体材料(307)を覆うように堆積させる。第3材料(501)をトレンチ(209)内に、かつ第2誘電体材料(309)の上に堆積させる。第2材料(309)及び第3材料(501)の内の一方の材料は、他方の材料をエッチングしないように選択的にエッチングすることができる。一の例では、第1材料(307)は第2材料(309)よりも小さい誘電率を有する。  (もっと読む)

(もっと読む)

半導体構成のための電気的接続を形成する方法

本発明は、半導体構成に関連して電気的接続を形成する方法を含む。その上に導電線路を有し、導電線路に隣接して少なくとも2つの拡散領域を有する半導体基板が設けられる。パターン化されるエッチ・ストップが拡散領域の上に形成される。パターン化されるエッチ・ストップは、開口を貫通して延びる1対の開口を有し、開口は導電線路の軸に実質的に平行に一列に並んでいる。絶縁材料がエッチ・ストップ上に形成される。絶縁材料は、絶縁材料内にトレンチを形成し且つ開口をエッチ・ストップから拡散領域まで延ばすために、エッチングに対して露出される。トレンチの少なくとも一部分は開口の直上にあり、線路の軸に沿って延びる。導電材料が開口内とトレンチ内に形成される。  (もっと読む)

(もっと読む)

調整可能なゲート電極の仕事関数を備えたデュアルメタルのCMOSトランジスタおよびその製造方法

デュアルメタルのCMOSの配列とその形成方法は、基板(10)と、その基板(10)上に形成された複数のNMOSデバイス(44)およびPMOSデバイス(46)を提供する。複数のNMOSデバイス(44)およびPMOSデバイス(46)の各々は、ゲート電極を有する。各NMOSゲート電極は、基板(10)上に第1シリサイド領域(50)を含み、その第1シリサイド領域(50)上に第1金属領域(48)を含む。NMOSゲート電極の第1シリサイド領域(50)は、シリコンの伝導帯に近い仕事関数を有する第1シリサイド(50)からなる。PMOSゲート電極の各々は、基板上に第2シリサイド領域(54)を含み、その第2シリサイド領域(54)上に第2金属領域(52)を含む。PMOSゲート電極の第2シリサイド領域(54)は、シリコンの価電子帯に近い仕事関数を有する第2シリサイド(54)からなる。  (もっと読む)

(もっと読む)

2,421 - 2,440 / 2,469

[ Back to top ]