Fターム[5F048BC06]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ソース・ドレイン (8,322) | 追加領域の形成 (3,324) | LDD (2,469)

Fターム[5F048BC06]に分類される特許

401 - 420 / 2,469

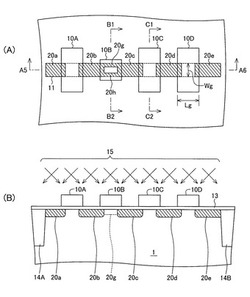

半導体装置及びその製造方法

【課題】エンハンスメント型FETとディプレッション型FETとを集積する場合に製造工程数の削減を実現できる半導体装置の製造方法を提供する。

【解決手段】この製造方法は、アクティブ領域11を横断しゲート電極10Aよりも長さが短いゲート電極10Bを形成する工程と、ゲート電極10A,10Bをマスクとして、アクティブ領域11に不純物を斜めイオン注入することにより、ゲート電極10Aのゲート長方向両側の領域に互いに連続しない不純物拡散領域20a,20bを形成するとともに、ゲート電極10Bのゲート長方向両側の一方の領域から他方の領域に亘って連続する不純物拡散領域20g,20hを形成する斜めイオン注入工程とを含む。

(もっと読む)

自己整合されたデュアル応力層を用いるCMOS構造体及び方法

【課題】 デバイス性能を向上させ、チップの留まりを改善するために、CMOS構造体内に機械的応力を与える構造体及び方法を提供すること。

【解決手段】 第1のトランジスタの上に配置された第1の応力層及び第2のトランジスタの上に配置された第2の応力層が、当接するが、重ならない、CMOS構造体及びCMOS構造体を製造する方法が提供される。こうした重ならない当接により、第1のトランジスタ及び第2のトランジスタの一方の中のソース/ドレイン領域の上に、シリサイド層へのコンタクトを形成するとき、製造の柔軟性が向上する。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタの性能を良好にするとともに、トランジスタにより構成されたアンチヒューズのゲート絶縁膜の破壊後の特性を良好にする。

【解決手段】アンチヒューズ素子190として機能するNMOSトランジスタにおいて、N型チャネル領域112aが設けられている。また、通常のNMOSトランジスタ194には、N型エクステンション領域120およびP型ポケット領域122が設けられているが、アンチヒューズ素子190には、エクステンション領域およびポケット領域が設けられない。

(もっと読む)

半導体製造装置

【課題】内部応力を有する膜を基板の裏面にのみ形成することにより、基板の反り量を抑制し、その際に基板の表面にダメージを与えず、裏面に対する成膜と表面に対するパターン形成とを一貫して行う半導体製造装置を得られるようにする。

【解決手段】基板に薬液を塗布する薬液塗布部102と、基板を加熱する加熱処理部104と、基板の表面にレジストを塗布するレジスト塗布部107と、そのレジストに所定のパターンを露光する露光部105と、そのレジストを現像することにより所定のパターンを得る現像部108とを備えている。薬液塗布部102は、基板を浮遊した状態で、基板を回転させながら基板の裏面にのみ薬液を塗布する薬液塗布手段を有し、加熱処理部104は、基板に熱処理を行うことにより、内部応力を有する応力印加膜を成膜する熱処理手段を有し、裏面に応力印加膜の成膜を行うことと、表面に所定のパターンを形成する処理とを一貫して行う。

(もっと読む)

半導体装置及びその製造方法

【課題】MOSプロセスへの導入が容易で、エミッタ−ベース間のリーク電流(電界強度)を低減し、ノイズやサージ電圧の影響を受けにくい高性能な半導体装置とその製造方法の提供。

【解決手段】導電膜をマスクとして、2回のイオン注入を行ってエミッタを形成する。第2エミッタ領域111bは、低濃度の不純物イオン注入によって形成し、第1エミッタ領域111aは、高濃度の不純物イオン注入によって形成する。その結果、エミッタの周縁部に低濃度の第2エミッタ領域が形成され、電界が緩和され、リーク電流が低減する。また、導電膜とエミッタ電極116とが接続され、ノイズの影響を受けにくくなる。

(もっと読む)

半導体装置

【課題】多層配線間で形成される寄生容量を低減することを目的の一とする。

【解決手段】絶縁表面上に第1配線と、前記第1配線を覆う第1層間絶縁膜と、前記第1層間絶縁膜上の一部に接して第2層間絶縁膜と、前記第1層間絶縁膜及び前記第2層間絶縁膜上に第2配線とを有し、前記第1配線と前記第2配線とが重なっている領域には、前記第1層間絶縁膜と前記第2層間絶縁膜とが積層された半導体装置である。第1配線と第2配線間に層間絶縁膜が積層されていることで寄生容量の低減が可能となる。

(もっと読む)

半導体装置

【課題】待機電力の低減を実現する半導体装置の提供を、目的の一とする。

【解決手段】酸化物半導体を活性層として有するトランジスタをスイッチング素子として用い、該スイッチング素子で、集積回路を構成する回路への電源電圧の供給を制御する。具体的には、回路が動作状態のときに上記スイッチング素子により、当該回路への電源電圧の供給を行い、回路が停止状態のときに上記スイッチング素子により、当該回路への電源電圧の供給を停止する。また、電源電圧が供給される回路は、半導体を用いて形成されるトランジスタ、ダイオード、容量素子、抵抗素子、インダクタンスなどの、集積回路を構成する最小単位の半導体素子を、単数または複数有する。そして、上記半導体素子が有する半導体は、結晶性を有するシリコン(結晶性シリコン)、具体的には、微結晶シリコン、多結晶シリコン、単結晶シリコンを含む。

(もっと読む)

半導体装置の製造方法

【課題】メモリセル領域と高電圧トランジスタとの高濃度不純物拡散領域を同時にイオン注入で形成し、且つ高電圧トランジスタ側の方が浅くなるように形成する。

【解決手段】シリコン基板1にメモリセル領域にゲート電極MG、SGを形成し(図3(b))、周辺回路領域にゲート電極PG(図3(c))を形成する。周辺回路領域のゲート電極PGは、高電圧トランジスタについては厚い膜厚のゲート絶縁膜11が形成されている。ゲート絶縁膜11を残した状態でTEOS酸化膜9を成膜し、スペーサ加工をする。この時、スペーサ9aを形成すると共に、ゲート絶縁膜11を半分程度エッチングして11aとする。TEOS酸化膜10を形成後に高濃度不純物拡散領域1d、1eをイオン注入で深さd1、d2で形成する。高電圧トランジスタについてはゲート絶縁膜11aを介して行うので、浅く形成される。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜の膜厚が異なる複数種類のMISトランジスタを有する半導体装置において、ゲート電極の寸法ばらつきやゲート絶縁膜の信頼性低下等を防止しうる半導体装置の製造方法を提供する。

【解決手段】半導体基板の第1の領域、第2の領域及び第3の領域に、第1の絶縁膜を形成し、第1の領域及び前記第2の領域に形成された第1の絶縁膜を除去し、半導体基板の表面を酸化し、第1の領域及び第2の領域に第2の絶縁膜を形成するとともに、第1の絶縁膜が形成された前記第3の領域を更に酸化し、第2の領域に形成された第2の絶縁膜及び第3の領域に形成された第1の絶縁膜を除去し、半導体基板の表面を酸化し、第2の領域及び第3の領域に第1のゲート絶縁膜を形成するとともに、第2の絶縁膜が形成された第1の領域を更に酸化し、第1の領域に第1のゲート絶縁膜よりも厚い第2のゲート絶縁膜を形成する。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層を含むトランジスタと、酸化物半導体以外の半導体材料を用いて構成された論理回路と、を有し、前記トランジスタのソース電極またはドレイン電極の一方と、前記論理回路の少なくとも一の入力とは電気的に接続され、前記トランジスタを介して、前記論理回路に少なくとも一の入力信号が供給される半導体装置である。ここで、トランジスタのオフ電流は1×10−13A以下であるのが望ましい。

(もっと読む)

半導体装置およびDC−DCコンバータ

【課題】半導体装置のソース領域とドレイン領域との間のオン抵抗を低減させる。

【解決手段】第1導電型のソース領域と第1導電型のドレイン領域とが表面に選択的に形成された第2導電型のベース層と、前記ベース層内に設けられ、前記ソース領域から前記ドレイン領域の方向に延在する素子分離層と、前記素子分離層の上側に設けられ、前記ソース領域と前記ドレイン領域との間の電流経路を制御する制御電極と、前記ベース層の上側の少なくとも一部または前記素子分離層内の少なくとも一部に配置され、前記素子分離層の比誘電率よりも高い比誘電率を有する高誘電体層と、前記ソース領域に接続された第1の主電極と、前記ドレイン領域に接続された第2の主電極と、を備えたことを特徴とする半導体装置が提供される。

(もっと読む)

半導体装置およびその製造方法

【課題】シリサイド層とSi層との界面における抵抗が低いMOSFETを備える半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板2上にゲート絶縁膜11を介して形成されたゲート電極12と、半導体基板2上のゲート電極12の両側に形成された、チャネル移動度に実質的な影響を与えないSiGe層15と、SiGe層15上に形成されたSi層16と、半導体基板2、SiGe層15、およびSi層16内のゲート電極12の両側に形成されたn型ソース・ドレイン領域19と、Si層16上に形成されたシリサイド層17と、を有する。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】半導体材料を含む基板に設けられたチャネル形成領域と、チャネル形成領域を挟むように設けられた不純物領域と、チャネル形成領域上の第1のゲート絶縁層と、第1のゲート絶縁層上の第1のゲート電極と、不純物領域と電気的に接続する第1のソース電極および第1のドレイン電極と、を有する第1のトランジスタと、半導体材料を含む基板上の第2のゲート電極と、第2のゲート電極上の第2のゲート絶縁層と、第2のゲート絶縁層上の酸化物半導体層と、酸化物半導体層と電気的に接続する第2のソース電極および第2のドレイン電極と、を有する第2のトランジスタと、を有する半導体装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】pチャネルトランジスタ及びnチャネルトランジスタの閾値電圧を共に低減できるCMISトランジスタを有する半導体装置を提供する。

【解決手段】pチャネルトランジスタは、半導体基板100における第1の領域上に形成された第1のゲート構造150Aと、第1のゲート構造150Aの側壁上に形成された第1のスペーサ構造とを有する。nチャネルトランジスタは、半導体基板100における第2の領域上に形成された第2のゲート構造150Bと、第2のゲート構造150Bの側壁上に形成された第2のスペーサ構造とを有する。第1のスペーサ構造における第1のゲート構造150Aの側壁との接触部分の含有酸素濃度は、第2のスペーサ構造における第2のゲート構造150Bの側壁との接触部分の含有酸素濃度よりも高い。

(もっと読む)

半導体装置、その製造方法及び表示装置

【課題】他の基板に接合され、かつ薄膜化された基体層に形成されたPMOSトランジスタのサブスレッシュホールド特性を向上することができる半導体装置、その製造方法及び表示装置を提供する。

【解決手段】基板と、基体層に形成され、かつ素子を含むとともに、基板に接合されたデバイス部とを備える半導体装置であって、上記デバイス部は、素子として、少なくともPMOSトランジスタを含み、上記PMOSトランジスタは、基体層のゲート電極側に電気伝導経路を有する半導体装置である。

(もっと読む)

半導体装置

【課題】低酸素処理を施したシリコン基板は基板表面層が応力に対して非常にもろくなってしまい、ハンド津愛想うちの製造プロセスの過程でクラックや反りが発生する原因ともなってしまう。

【解決手段】チャネル形成領域に形成された不純物領域に応力を集中させるため、チャネル形成領域に対して人為的かつ局部的に不純物領域を設ける。チャネル形成領域に局部的に添加された不純物元素(炭素、窒素、酸素から選ばれた一種または複数種類の元素)の領域は、低酸素処理を施したシリコン基板の応力を緩和する緩衝領域として機能する。

(もっと読む)

半導体装置の製造方法

【課題】生産性を低下させず信頼性の高い半導体装置を製造できる半導体装置の製造方法を提供する。

【解決手段】第一のゲート絶縁膜124Aを形成する工程と、第一のゲート絶縁膜124Aのうち第二のトランジスタ形成領域を被覆する部分と、第一のトランジスタ形成領域のうちソース・ドレイン領域に位置する部分とを除去する工程と、第二のゲート絶縁膜124Bを形成する工程と、第一のゲート絶縁膜124Aと第二のゲート絶縁膜124Bとが積層された領域に第一のゲート電極を形成するとともに、第二のトランジスタ形成領域の第二のゲート絶縁膜上に、第二のゲート電極を形成する工程と、第二のトランジスタ形成領域において、第二のゲート電極直下の第二のゲート絶縁膜を残すとともに、他の領域の第二のゲート絶縁膜を除去し、第一のトランジスタ形成領域において、ソース・ドレイン領域に形成された第二のゲート絶縁膜124Bを除去する工程を実施する。

(もっと読む)

高耐圧MOSトランジスタおよび半導体集積回路装置、高耐圧半導体装置

【課題】半導体基板上に他のCMOS素子と集積して形成される高耐圧MOSトランジスタの、工程数を抑制しながら、ドレイン耐圧特性を向上させる。

【解決手段】半導体基板21と、ゲート電極23と、第2の導電型のソース領域21Sと、第2の導電型のドレイン領域21Dと、ソースエクステンション領域21aと、ドレインエクステンション領域21bと、を含み、ソースエクステンション領域21aとドレインエクステンション領域21bとの間にはチャネル領域が形成され、ソース領域21Sおよびソースエクステンション領域21aの下方には第1のウェル21PWが、第1の導電型で、素子分離領域21Iの下端部を超える深さで形成され、第1のウェル21PWの下方には第2のウェル21DNWが第2の導電型で形成され、第1のウェル21PWおよび第2のウェル21DNWは、ドレインエクステンション領域21b、ドレイン領域21Dの下には形成されない。

(もっと読む)

半導体装置の製造方法

【課題】SOIデバイスにおいて生じやすい基板浮遊問題やホットキャリアの問題を充分に抑制することが可能で、広く分布する部分分離絶縁膜であっても周囲の構造に対し結晶欠陥を生じさせにくい半導体装置の製造方法を提供する。

【解決手段】各MOSトランジスタTR1の間に設けられた部分分離絶縁膜5b内におよそ一定の間隔を置いて、素子としての機能を有しないダミー領域DM1を形成する。これにより、部分分離絶縁膜5b下のシリコン層3bよりも抵抗値の低いダミー領域DM1の占める割合が増加して、基板浮遊問題やホットキャリアの問題の抑制が行えるようになる。

(もっと読む)

半導体装置及びその製造方法

【課題】デュアルメタルゲートプロセスを用いることなく、p型MISトランジスタ及びn型MISトランジスタ双方の特性を向上した半導体装置を実現できるようにする。

【解決手段】半導体装置は、p型半導体領域10Aの上に順次形成された第1の界面シリコン酸化膜105、アルミニウムを含む第1のゲート絶縁膜106A及び第1のゲート電極119Aと、n型半導体領域10Bの上に順次形成された第2の界面シリコン酸化膜105、実効仕事関数を低下させる効果を有する元素を含む第2のゲート絶縁膜106B及び第2のゲート電極119Aとを備えている。第1のゲート絶縁膜106Aの上部におけるアルミニウムの濃度は、1×1020/cm3以上である。第2のゲート絶縁膜106Bの上部におけるアルミニウムの濃度は、1×1019/cm3以下である。第1の界面シリコン酸化膜105の膜厚と第2の界面シリコン酸化膜105の膜厚との差は0.2nm以下である。

(もっと読む)

401 - 420 / 2,469

[ Back to top ]