Fターム[5F048BD02]の内容

MOSIC、バイポーラ・MOSIC (97,815) | チャネル (4,415) | 形状 (1,258) | チャネル長(幅) (272)

Fターム[5F048BD02]に分類される特許

261 - 272 / 272

トレンチ拡散領域を有する金属酸化物半導体デバイスおよびその形成方法

【課題】改善された高周波性能およびオン状態特性を可能にするMOSデバイスを提供すること。

【解決手段】MOSデバイスは、第1の伝導型の半導体層と、半導体層の上面に近接して半導体層中に形成された第2の伝導型の第1および第2のソース/ドレイン領域とを含む。第1および第2のソース/ドレイン領域は、互いに間隔を開けて配置されている。ゲートは、少なくとも部分的に第1のソース/ドレイン領域と第2のソース/ドレイン領域との間の半導体層の上に形成され、かつ半導体層から電気的に絶縁されている。第1および第2のソース/ドレイン領域のうちの少なくとも特定の1つは、半導体層とその特定のソース/ドレイン領域との間の接合の幅よりも実質的に大きな実効幅を有して形作られている。

(もっと読む)

Nチャネルプルアップ素子および論理回路

【課題】相補型(CMOS)集積回路におけるプルアップデバイスとしてPMOSFETの代替品となる新たな種類のnチャネルMOSFETを提供する。

【解決手段】切換可能な負性微分抵抗(SNDR)特性を有するnチャネルFETを開示している。このSNDRFETをデプリーションモードデバイスとして構成し、実質的にpチャネルデバイスとして動作するようにバイアスをかける。このデバイスはnチャネルデバイスであるから、動作速度は高く、一方、大規模回路として設計製造する際のプロセス技術の複雑性は緩和される。このデバイスはCMOSに匹敵する性能を達成するので論理ゲート(インバータに含まれるものなど)におけるpチャネルプルアップデバイスの代替品として好適である。

(もっと読む)

移動度を半導体素子において増加させる方法及び装置

トランジスタのチャネル領域における移動度の増大を実現する方法及び装置が提示される。一の実施形態では、チャネル領域(18)は2軸応力が発生する基板の上に形成される。ソース領域(30)及びドレイン領域(32)は基板の上に形成される。ソース領域及びドレイン領域は1軸応力を2軸応力発生チャネル領域に追加する形で発生させるように作用する。1軸応力及び2軸応力はPチャネルトランジスタに関しては共に圧縮応力であり、そしてNチャネルトランジスタに関しては共に引っ張り応力である。その結果、キャリア移動度が短チャネルトランジスタ及び長チャネルトランジスタの両方に関して増加する。両方のタイプのトランジスタを同じ集積回路に搭載することができる。  (もっと読む)

(もっと読む)

電界効果型トランジスタ、相補型電界効果型トランジスタ、および電界効果型トランジスタの製造方法

【課題】 電界効果型トランジスタのオン電流を向上させる。

【解決手段】 {100}面を主面とする単結晶シリコン基板101上に、単結晶シリコンの<010>結晶軸方向または<010>結晶軸方向と等価な軸方向に実質的に延在するゲート電極107と、ゲート電極107の両脇において単結晶シリコン基板101の表面に設けられたソース・ドレイン領域129とを設ける。ゲート電極107の直下の領域におけ単結晶シリコン基板101の表面に、主面と、ゲート電極107の延在方向に沿って主面に対して傾斜した傾斜面133と、を設ける。

(もっと読む)

半導体集積回路装置

【課題】 半導体集積回路装置の設計中あるいは設計完了後の論理変更を容易とする。

【解決手段】 所定の回路が形成された主領域と、主領域に形成された回路の論理変更に用いる予備素子領域とを有する。予備素子領域は、Pチャンネルトランジスタ領域111〜113と、Nチャンネルトランジスタ領域121〜123と、Pチャンネルトランジスタ領域上及びNチャンネルトランジスタ領域上に設けられた複数のゲート電極131〜134、141〜144と、ゲート電極よりも上層の配線層に形成されたバイパス配線151〜155と、バイパス配線よりも上層に位置する主配線層とを備える。バイパス配線151〜155は、いずれも主配線層とバイパス配線とを分離する絶縁層に形成されたコンタクトホールによって、少なくとも2箇所で主配線層と接続可能に構成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】 微細化が進められてもトランジスタのオン電流を十分に確保することができる半導体装置及びその製造方法を提供する。

【解決手段】 全面に高電圧トランジスタ用のゲート絶縁膜4を形成した後、低電圧領域内に存在するゲート絶縁膜4を除去する際に、活性領域3が露出した時点でエッチングを終了するのではなく、低電圧領域内において、活性領域3の表面よりも素子分離絶縁膜2の表面が、例えば15nm程度低くなるまでオーバーエッチングを行う。次に、低電圧領域内の活性領域3に対して高温急速水素加熱処理を行う。この結果、低電圧領域内の活性領域3の表面から自然酸化膜が除去され、平坦度が増すと共に、角部が丸まる。

(もっと読む)

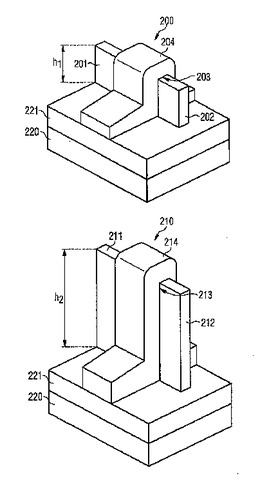

Fin電界効果トランジスタの配列及びFin電界効果トランジスタの配列の形成方法

本発明は、基板と、フィンにおける第1,第2のソース/ドレイン領域の間にチャネル領域が形成され、かつ、フィンの上部にゲート領域が形成されるフィンを有する、上記基板上および/または上記基板中に形成される、第1のFin電界効果トランジスタと、フィンにおける第1,第2のソース/ドレイン領域の間にチャネル領域が形成され、かつ、当該フィンの上部にゲート領域が形成されるフィンを有する、上記基板上および/または上記基板中に形成される、第2のFin電界効果トランジスタとを備えた、Fin電界効果トランジスタ配置に関する。上記第1のFin電界効果トランジスタのフィンの高さは、上記第2のFin電界効果トランジスタのフィンの高さよりも高くなっている。  (もっと読む)

(もっと読む)

半導体装置と半導体装置の製造方法

バリア性を有する絶縁膜サイドウォールスペーサを有する半導体装置を提供する。 半導体装置は、半導体基板の上に形成されたゲート酸化膜とゲート電極と;半導体基板内に形成されたソース/ドレイン領域と;ゲート電極側壁上に形成された2層以上の積層サイドウォールスペーサであって、最外層以外の層として窒化膜を含み、最外層は、酸化膜又は酸化窒化膜で形成され、下面が半導体基板またはゲート酸化膜、又は窒化膜以外の他のサイドウォールスペーサ層と接している第1積層サイドウォールスペーサと;を有する。さらに、不揮発性メモリの積層ゲート電極構造と;積層ゲート電極構造の側壁上に形成され、中間層として半導体基板に接しない窒化膜を含む3層以上の第2積層サイドウォールスペーサと;を有することもできる。  (もっと読む)

(もっと読む)

フィン型電界効果トランジスタを有する半導体装置

n型電界効果トランジスタおよびp型電界効果トランジスタとを含む半導体装置であって、n型電界効果トランジスタを構成する突起状半導体領域の結晶方位は、その基板と平行な面が実質上{100}面であり、その側面が実質上前記{100}面と直交する{100}面であり、p型電界効果トランジスタを構成する突起状半導体領域の結晶方位は、その基板と平行な面が実質上{100}面であり、その側面が実質上前記{100}面と直交する{110}面である、という条件を満足する半導体装置とする。 (もっと読む)

半導体装置及びその製造方法

基体平面に対して突出した半導体凸部と、この半導体凸部を跨ぐようにその上面から相対する両側面上に延在するゲート電極と、このゲート電極と前記半導体凸部の間に介在する絶縁膜と、ソース/ドレイン領域とを有するMIS型電界効果トランジスタを備えた半導体装置であって、1つのチップ内に、前記MIS型電界効果トランジスタとして、ゲート電極下の前記半導体凸部における基板平面に平行かつチャネル長方向に垂直な方向の幅Wが互いに異なる複数種のトランジスタを有する半導体装置。 (もっと読む)

集積化電子切断回路、方法およびシステム

過渡現象遮断用の組み合わせデバイス。過渡現象が入力端子 40に印加されると、トランジスタ 44のボディ電位がデプレッションモードJFET型遮断トランジスタ 71のゲート 81を駆動するように、パストランジスタ44が配置されている。同時に、チャネル77を空乏化するために、電位差 Vdが外部ゲート 52の両端に印加される。このように、外部端子上に現れる過渡現象は、非常に急速に伝播されて、チャネル 77および85を空乏化するので、出力端子42に接続されたデバイスが故障する前に、入力端子 40を出力端子 42から効果的に分離する。一旦過渡現象がおさまると、デバイス 37はその通常の導通状態に戻る。 (もっと読む)

半導体集積回路装置およびその製造方法

【課題】 サブミクロンCMOSトランジスタを、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗などと一緒に、それぞれの特性を劣化させることなく、同一基板上に混載すること。

【解決手段】 半導体基板1の一主面側にパンチスルーストッパー層を形成する際に、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗を形成する領域をマスクしてたとえばイオン注入をおこなう。それによって、サブミクロンCMOSトランジスタの形成領域にパンチスルーストッパー領域4を形成するとともに、アナログCMOSトランジスタ、高耐圧MOSトランジスタ、バイポーラトランジスタ、ダイオードまたは拡散抵抗の形成領域にパンチスルーストッパー領域が形成されるのを防ぐ。

(もっと読む)

261 - 272 / 272

[ Back to top ]