Fターム[5F048BD02]の内容

MOSIC、バイポーラ・MOSIC (97,815) | チャネル (4,415) | 形状 (1,258) | チャネル長(幅) (272)

Fターム[5F048BD02]に分類される特許

101 - 120 / 272

半導体装置

【課題】 動作マージンを確保しつつ、微細化を可能とするSRAMセルを提供する。

【解決手段】

SRAMセルが、それぞれ、NMOSドライバとPMOSロードとが接続された第1、第2のインバータを含み、それぞれのインバータの内部ノードが他方のインバータの入力に接続されたフリップフロップ回路と、第1、第2のビット線と、第1、第2のインバータの内部ノードと第1、第2のビット線との間に接続された第1、第2のNMOSトランスファトランジスタであって、それぞれ、絶縁ゲート電極構造の両側に形成された第1、第2のn型ソース/ドレイン領域と、を含み、2つの第1のn型ソース/ドレイン領域が第1、第2のインバータの内部ノードに接続され、2つの第2のn型ソース/ドレイン領域が第1、第2のビット線に接続された第1、第2のNMOSトランスファトランジスタと、第1のn型ソース/ドレイン領域を覆って形成された圧縮応力膜と、第2のn型ソース/ドレイン領域を覆って形成された引張応力膜と、を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法。

【課題】半導体装置の特性劣化を抑制し、半導体装置のサイズを縮小する技術の提供。

【解決手段】半導体装置は、半導体領域1A内に設けられる第1及び第2の拡散層2A,2Bと、拡散層2A,2B間に設けられる第3の拡散層2Cと、第1の拡散層2Aの周囲を取り囲んで、半導体領域1A表面のゲート絶縁膜3A上に設けられる第1のゲート電極4Aと、第2の拡散層2Bの周囲を取り囲んで、半導体領域1A表面のゲート絶縁膜上に設けられる第2のゲート電極4Bと、ゲート電極4A,4Bの側面上に設けられる第1及び第2の側壁絶縁膜12A,12Bとを具備し、第1及び第2のゲート電極4A,4Bは、側壁絶縁膜12A,12Bが直接接触する部分を有し、第3の拡散層2Cの周囲は、ゲート電極4A,4Bによって取り囲まれている。

(もっと読む)

半導体装置及びその製造方法、並びに、データ処理システム

【課題】異なる特性を有するリセスチャネル型のトランジスタを同一工程で同時に形成する。

【解決手段】ハードマスク71〜73を用いて半導体基板2をエッチングし、ハードマスク71〜73の側面にサイドウォール絶縁膜38を形成し、ハードマスク71,72の側面に形成されたサイドウォール絶縁膜38を選択的に除去し、ハードマスク71〜73とサイドウォール絶縁膜38を用いて半導体基板2をさらにエッチングし、ハードマスク71〜73に覆われていた半導体基板2の一部にそれぞれゲートトレンチ12,22,32を同時に形成する工程と、ゲートトレンチ12,22,32の内部にゲート電極13,23,33を形成する工程と備える。これにより、フィン状領域21f,31fの高さが異なる複数のリセスチャネル型トランジスタを同時に形成することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】周辺回路部のLV系トランジスタでの結晶欠陥の発生を抑制しつつ、HV系トランジスタでの反転リークなどの増加を抑制できるようにするNAND型フラッシュメモリの半導体装置と製造方法を提供する。

【解決手段】LV系トランジスタ領域103のSTI304の上面を、EB加工により、セル領域104のSTI404の上面と同時にエッチングする。こうして、HV系トランジスタ領域102のSTI204の上面の高さはそのままに、LV系トランジスタ領域103のSTI304の上面のみを、第1の電極膜12の上面の高さよりも下げる。上面の高さを下げた分だけ、LV系トランジスタ領域103のSTI304での素子分離用絶縁膜の膜厚を削減して、塗布膜の収縮応力を緩和させる。

(もっと読む)

半導体装置およびその製造方法

【課題】同じ導電型を有するトランジスタであっても、用途に応じて特性を好ましいものにする。

【解決手段】半導体装置100は、半導体基板102上に形成された同じ導電型を有する第1のトランジスタ210および第2のトランジスタ212を含む。第1のトランジスタ210は、ゲート絶縁膜としてHf含有ゲート絶縁膜106を含み、第2のトランジスタ212は、ゲート絶縁膜としてシリコン酸化膜124を含むとともにHf含有膜を含まない。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】同一の半導体基板上に数種類のトランジスタを簡易なプロセスによって形成する半導体装置の製造方法の提供。

【解決手段】LDMOS領域100とオフセットドレインMOS領域200とに、同時に、第2導電型の第1ウェル30を形成する工程と、LDMOS領域100の第1ウェル30と、CMOS領域100とに、同時に、第1導電型の第2ウェル32を形成する工程と、CMOS領域300に、第2導電型の第2ウェル34を形成する工程と、オフセットドレインMOS領域200に第1導電型のオフセット層22を形成する工程とを含み、第1ウェル30は、第2ウェル32,34よりも深いウェルであり、第2ウェル32,34は、高エネルギーイオン注入法によって形成されたレトログレードウェルである、半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】絶縁ゲートバイポーラトランジスタのスイッチング特性および低オン抵抗を維持しつつ耐圧特性を改善しかつ占有面積を低減する。

【解決手段】絶縁ゲートバイポーラトランジスタ(IGBT:2)のターンオフ時のホール流入を抑制するPチャネルMOSトランジスタ(PQ)のゲート電極ノード(6)に対し、IGBTのオフ状態時においてゲート絶縁膜に印加される電圧を緩和する電圧緩和素子(1)を設ける。

(もっと読む)

半導体装置

【課題】印加電圧に対して従来よりも高い耐性を有し、小型化に優れ、被保護素子を保護する半導体装置を提供する。

【解決手段】半導体装置は、被保護素子に接続され、ソース層とドレイン層との間を放電経路として被保護素子を保護する半導体装置であって、絶縁膜20上に設けられた半導体層30と、半導体層内に形成され、第1の方向に延伸するソース層Sと、半導体層内に形成され、ソース層に沿って延伸するドレイン層Dと、ソース層とドレイン層との間の半導体層において第1の方向に延伸するように設けられた複数のボディ領域Bと、複数のボディ領域を接続するボディ接続部BCPとを備え、ボディ接続部から比較的離れた位置におけるソース層とドレイン層との間の第1の間隔は、ボディ接続部の比較的近傍におけるソース層とドレイン層との間の第2の間隔よりも大きい。

(もっと読む)

CMOSインバータ

【課題】ホットキャリア劣化による素子性能の低下を低減すること。

【解決手段】メイン−nMOS52を含む第1回路部分C1及びメイン−pMOS54を含む第2回路部分C2の双方又はいずれか一方を備えており、第1回路部分は、メイン−nMOSと電気的に並列に接続されていて、メイン−nMOSと利得係数が等しく、かつ閾値電圧が段階的に大きくなる1個以上のサブ−nMOS14を備えており、第2回路部分は、メイン−pMOSと電気的に並列に接続されていて、メイン−pMOSと利得係数が等しく、かつ閾値電圧が段階的に大きくなる1個以上のサブ−pMOS18を備えている。

(もっと読む)

半導体装置

【課題】 サージ電流を流すための複数個のトランジスタをできるだけ一斉にオンさせることによってサージに対する保護性能を向上させる。

【解決手段】 第1の外部電位に接続される第1パッドTE2と第2の外部電位に接続される第2パッドとの間に形成されているとともに第1パッドTE2に入力するサージから内部回路を保護するnMOS保護回路1gを備えている。nMOS保護回路1gはp型(第2導電型)ウェル4内に互いに離間して形成されているトランジスタ形成部10とp+型ウェルタップ領域30を備えている。トランジスタ形成部10を複数個のトランジスタが並んでいる方向に沿って観測したときに、トランジスタ形成部10の中央領域に形成されている少なくとも1個のトランジスタのスナップバック電圧が、そのトランジスタよりも端部側に形成されている少なくとも1個のトランジスタのスナップバック電圧よりも高い。

(もっと読む)

半導体基板の作製方法及び半導体装置

【課題】高性能な半導体素子を形成することを可能とする半導体基板および半導体装置の作製方法を提供する。

【解決手段】脆化層を有する単結晶半導体基板と、ベース基板とを絶縁層を介して貼り合わせ、熱処理によって、脆化層を境として単結晶半導体基板を分離して、ベース基板上に単結晶半導体層を固定する。次いで、モニタ基板の複数の領域に対して互いに異なるエネルギー密度条件でレーザ光を照射し、レーザ光を照射後の単結晶半導体層のそれぞれの領域の炭素濃度及び水素濃度の深さ方向の濃度分布を測定し、炭素濃度が極大を有し、且つ水素濃度がショルダーピークを有するレーザ光の照射強度を最適なレーザ光の照射強度とする。モニタ基板を用いて検出した最適のエネルギー密度で、単結晶半導体層にレーザ光を照射し、半導体基板を作製する。

(もっと読む)

半導体装置

【課題】ドレイン・オン電流値のばらつきが小さなCNT-FETを有する半導体装置を提供することを目的とする。また、本発明は、ドレイン電流のスイッチング比のばらつきが小さなCNT-FETを有する半導体装置を提供することを目的とする。

【解決手段】複数本のカーボンナノチューブをチャネルに用いる電界効果型トランジスタを二つ以上用いている半導体装置において、前記電界効果型トランジスタのドレイン・オン電流値のばらつきがσ1(オン電流値の標準偏差を平均値で割ったもの)のとき、各電界効果型トランジスタチャネルのカーボンナノチューブの本数Nが、N>31×σ1-1なる式(1)の関係を満たすことを特徴とする半導体装置を採用する。

(もっと読む)

半導体装置の製造方法及び電気光学装置の製造方法

【課題】装置作成の自由度が高い半導体装置の製造方法及び電気光学装置の製造方法を提

供する。

【解決手段】基板101上の所定領域に段差膜103を形成する工程と、段差膜103の

上面103a及び側壁103bを覆うように半導体薄膜104を形成する工程と、側壁1

03bを覆うように形成された半導体薄膜104aを残して、上面103aを覆うように

形成された半導体薄膜104を除去する工程と、段差膜104を除去する工程と、側壁1

03bを覆うように形成された半導体薄膜104aをチャネルとするフィン型トランジス

タ108を形成する工程と、を備える。

(もっと読む)

スタティックランダムアクセスメモリの製造方法

【課題】改善された性能および安定を備えたSRAMビットセルを製造できるスタティックランダムアクセスメモリの製造方法を提供する。

【解決手段】それぞれ2個のパスゲートトランジスタ302、プルダウントランジスタ304、及びプルアップトランジスタ306を有するSRAMビットセル300が形成され、シリコン窒化膜308が全面に堆積され、その後、プルダウントランジスタ304上にシリコン窒化膜308が形成され、その後、高温アニール処理が行われることにより、シリコン窒化膜308によってカバーされた領域が再結晶化され、歪が導入され、その後、シリコン窒化膜308が除去される。

(もっと読む)

半導体装置

【課題】 切り替え動作が速く、高い耐圧特性を持った半導体装置を提供する。

【解決方法】 半導体装置2には、同一の半導体基板4に縦型半導体素子領域6と横型半導体素子領域8が形成されている。横型半導体素子80では下部領域38に電流が流れないため、下部領域38を通して電流が流れる縦型半導体素子60と干渉しあわない。独立して動作する縦型半導体素子60と横型半導体素子80を混在して形成することができ、横型半導体素子80を用いて縦型半導体素子60の切り換え動作を速くすることができる。半導体装置2では、縦型半導体素子領域6に第1トレンチ24を形成し、横型半導体素子領域8に第2トレンチ54を形成する。トレンチ24、54を形成することによって高耐圧化できる効果を半導体装置の全域に亘って実現することができる。

(もっと読む)

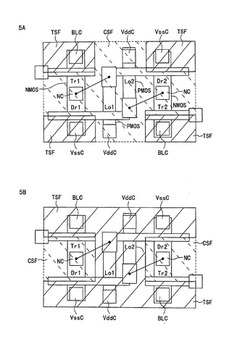

半導体装置、半導体装置の製造方法及び半導体装置の設計方法

【課題】複数のMOSFETにおけるトランジスタ特性変動を抑制すること。

【解決手段】半導体基板1に形成される第1のp型活性領域4と、半導体基板1に形成される第2のp型活性領域6と、半導体基板1に形成される第1のn型活性領域8と、半導体基板1に形成される第2のn型活性領域10と、第1のp型活性領域4の上方に形成されて第1の幅を有する第1導電パターン11gと、第2のp型活性領域6の上方に形成されて第1の幅より大きい第2の幅を有する第2導電パターン12gと、第1のn型活性領域8の上方に形成されて第3の幅を有する第3導電パターン13gと、第2のn型活性領域10の上方に形成されて第3の幅以下の第4の幅を有する第4導電パターン14gとを有する。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】ソース及びドレイン領域の幅を確保しつつ、フィンチャネルの幅のみを狭く形成できる半導体装置の製造方法及び半導体装置を提供する。

【解決手段】Fin型トランジスタの製造方法であって、シリコン基板1上に形成されたマスク層8をマスクとして、STI領域2を形成する工程と、マスク層8をウエットエッチングで縮退させて縮退マスク層8aを形成する工程と、縮退マスク層8aの表面にストッパ酸化膜16を形成し、全面にポリシリコン17を堆積した後、反射防止膜18、フォトレジスト19を形成する工程と、ワード線部分のフォトレジスト19を開口し、当該部分の反射防止膜18とポリシリコン17とを除去して、縮退マスク層8aを露出させた後に、フォトレジスト19を除去する工程と、縮退マスク層8aをマスクとして、縮退マスク層8aの下部両側のシリコン基板1をエッチングして、フィンチャネル30を形成する工程と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の低抵抗化を図ることができるとともに、ゲート電極の表面に大きな凹みが形成されるのを防止することができる構造の半導体装置およびその製造方法を提供する。

【解決手段】酸化膜20上に、第1トレンチ6内に空間22が残り、かつ、第2トレンチ7を埋め尽くすような厚さのドープドポリシリコン層21が形成される。次いで、ドープドポリシリコン層21上に、空間22を埋め尽くすような厚さのノンドープポリシリコン層23が形成される。その後、エッチバックにより、ドープドポリシリコン層21およびノンドープポリシリコン層23における第1トレンチ6および第2トレンチ7外の部分が除去される。

(もっと読む)

相補型MIS装置

【課題】CMOS装置において、pチャネルMOSトランジスタとnチャネルMOSトランジスタの大きさを平衡させる。

【解決手段】 シリコン基板の(100)面上に他の結晶面を有する構造を形成し、かかる構造上にマイクロ波プラズマ処理により、高品質なゲート絶縁膜を形成し、その上にゲート電極を形成する。その際、pチャネルMOSトランジスタとnチャネルMOSトランジスタのキャリア移動度が平衡するように、前記構造の寸法・形状を設定する。

(もっと読む)

制御回路を備える半導体装置

【課題】長時間拡散に伴うチップサイズを大きくすることやフライホイーリングダイオードを内蔵させることなく、かつIGBT部がオンからオフに移る際にコレクタ側を負電圧とする方向のサージ電圧が生じても破壊され難い、制御回路を備える半導体装置を提供すること。

【解決手段】IGBT部20と、IGBT部20の異常状態を検知する制御回路21を備え、前記IGBT部20のpコレクタ領域5側のpn接合界面には、バッテリ電圧より高いpn接合耐圧を有するように設定されるn型バッファ領域46を選択的に形成する構成を備える半導体装置とする。

(もっと読む)

101 - 120 / 272

[ Back to top ]