Fターム[5F048BD02]の内容

MOSIC、バイポーラ・MOSIC (97,815) | チャネル (4,415) | 形状 (1,258) | チャネル長(幅) (272)

Fターム[5F048BD02]に分類される特許

41 - 60 / 272

半導体装置及びその製造方法

【課題】工程数の増加を回避し得る半導体装置及びその製造方法を提供する。

【解決手段】低濃度ドレイン領域28hを形成するためのドーパント不純物が導入される所定領域を除く領域に、所定領域から離間するようにチャネルドープ層22dを形成する工程と、半導体基板10上にゲート絶縁膜24を介してゲート電極26dを形成する工程と、ゲート電極の一方の側の半導体基板内に低濃度ソース領域28gを形成し、ゲート電極の他方の側の半導体基板の所定領域に低濃度ドレイン領域28hを形成する工程とを有している。

(もっと読む)

半導体装置

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタは、半導体特性を示す金属酸化物により設けられ、下部のトランジスタが有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、該ゲート電極層と同一の層の一部を上部のトランジスタのバックゲートとして機能させる。下部のトランジスタは、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタのソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】簡便な製造方法によって製造された良好なTFT特性を有する半導体装置およびその製造方法を提供する。

【解決手段】本発明の半導体装置は、絶縁基板11と、絶縁基板11に支持されたチャネル領域33A、ソース領域34Aおよびドレイン領域35Aを含む半導体層30Aと、チャネル領域33Aの導電性を制御するゲート電極51とを有する。半導体層30Aは、チャネル領域33Aとソース領域34Aとの間に形成された第1低濃度領域31A、および、チャネル領域33Aとドレイン領域35Aとの間に形成された第2低濃度領域32Aとを有する。チャネル領域33A、第1および第2低濃度領域31Aおよび32Aは、ソースおよびドレイン領域34Aおよび35Aの不純物濃度より低い第1不純物濃度を有する。ゲート電極51は、第1および第2低濃度領域31Aおよび32Aの全部を覆うように形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの閾値電圧のバックゲート電圧依存性を低減することができる。

【解決手段】半導体装置100は、基板(例えば、P型半導体基板3)と、基板に形成され素子形成領域1を他の領域と分離する素子分離領域2と、を有している。更に、素子形成領域1上に形成されたゲート電極4を有し、ゲート電極4は、素子分離領域2において素子形成領域1を介して互いに対向する第1及び第2領域2a、2bの上にそれぞれ延伸している。更に、ゲート電極4を基準としてチャネル長方向Dに相互に離間するように素子形成領域1に形成された一対の拡散領域(例えば、N型拡散領域5)を有する。第1領域2a及び第2領域2bの上面の少なくとも一部分ずつは、素子形成領域1の上面よりも下に、チャネル幅Wの5%以上の深さに凹んでおり、それら凹み7内にもゲート電極4の一部分ずつが存在している。

(もっと読む)

半導体装置

【課題】異なる電源系統から電源電圧を供給される出力回路と入力回路とを含む半導体装置において、ESDサージ電圧が出力回路を介して入力回路にそのまま印加されることによって入力回路が破壊されることを有効に抑制する。

【解決手段】半導体装置が、第1電源パッド11と、第1接地パッド12と、第1電源線13と、第1接地線14と、出力回路15と、第2電源パッド21と、第2接地パッド22と、第2電源線23と、第2接地線24と、入力回路25と、信号線20と、メインESD保護素子16と、保護ダイオード対D1と、PMOSトランジスタP2とを備えている。出力回路15がPMOSトランジスタP3を含み、入力回路25がNMOSトランジスタN1を含む。PMOSトランジスタP2は、ソースが信号線20に接続され、ドレインが第2接地線24に接続され、ゲートとバックゲートが第2電源線23に接続されている。

(もっと読む)

半導体装置

【課題】放電効率の向上と、通常動作時の電位変動の伝達の抑制とを両立させることができる静電気保護素子を有する半導体装置を提供すること。

【解決手段】第1電源電位配線と第1接地電位配線との間にて、電気的に接続された第1回路、及びダイオード接続されたMOSトランジスタを有する第1保護素子と、第2電源電位配線と第2接地電位配線との間にて、電気的に接続された第2回路、及びダイオード接続されたMOSトランジスタを有する第2保護素子と、前記第1接地電位配線と前記第2接地電位配線との間に2つのMOSトランジスタが互いに逆バイアス状態になるように並列にダイオード接続された第3保護素子と、を備え、前記第3保護素子における2つのMOSトランジスタの閾値電圧は、前記第1保護素子及び前記第2保護素子における各MOSトランジスタの閾値電圧よりも大きく設定されている。

(もっと読む)

半導体集積回路及びデータ処理システム

【課題】意図的に誤動作を生じさせるための局所的な光照射を検出するための構成を小さなチップ占有面積で実現し、検出感度を高くする。

【解決手段】ロジック回路(6)が形成された領域に分散され初段の入力が一定論理値にされて直列的に接続された複数個の検出インバータ(100)を検出素子として採用し、単数又は複数のインバータに光が照射されて各々に出力が反転することによって直列的に接続された複数個の検出インバータの最終出力が判定され、これにより局所的な光照射を検出することができる。

(もっと読む)

ESD保護回路及び半導体装置

【課題】ESD保護回路に使用するMOSトランジスタのオフリーク電流を低減して、信号端子の端子リーク電流を低減する。

【解決手段】ESD保護回路100は、MOSトランジスタ10(又は20)を備える。MOSトランジスタ10(又は20)は、ドレイン端子とソース端子が信号端子2と電源VDD(又はGND)にそれぞれ接続され、ソース端子に印加されるVDD(又はGND)の電位よりも絶対値が大きく、ゲート端子とソース端子間の制御電圧が逆バイアスとなる電位VH(又はVL)がゲート端子に印加される。

(もっと読む)

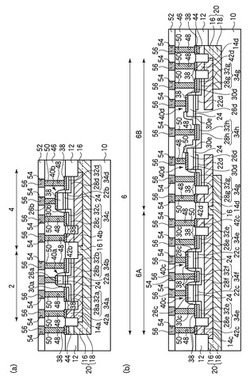

半導体装置

【課題】ロジック系CMOSトランジスタおよびパワー系DMOSトランジスタのそれぞれが最適な構造を有する半導体装置を提供する。

【解決手段】第1半導体領域2の表面側に設けられた第1ソース領域3、ドレイン領域4と、第1ゲート13と、第1ゲートの両側面に形成された第1サイドウォール15と、第1LDD領域17とを有する第1のMOSトランジスタと、第2半導体領域22の表面側に設けられた第2ソース領域23、ドレイン領域24と、第2ゲート33と、第2ゲートの第2ドレイン側の側面に形成され、第1サイドウォールよりも広い第2サイドウォール41と、第2サイドウォール直下に形成されたドリフト領域43と、第2ゲートの第2ソース側の側面に形成され、第1サイドウォールよりも狭い第3サイドウォール35と、第3サイドウォール直下に形成された第2LDD領域37とを有する第2のMOSトランジスタを備えた半導体装置を提供する。

(もっと読む)

半導体装置

【課題】LCDドライバのチップサイズを縮小させる

【解決手段】シリコン基板上に構成されたLCDドライバDRV1を有する半導体装置であって、LCDドライバDRV1は、ソース出力回路領域RSに配置され、データ信号VDを生じる複数のソース出力セルCS1と、そのデータ信号VDを受けて外部に送信するための複数の出力パッドPD1とを有する。複数の出力パッドPD1はシリコン基板上の行方向に沿って並んで配置され、複数のソース出力セルCS1は行方向に沿って2行N列に並んで配置されている。特に、第1行第N列目に配置するソース出力セルCS1は、第(2N−1)番目の出力パッドPD1に電気的に接続され、第2行第N列目に配置するソース出力セルCS1は、第(2N)番目の出力パッドPD1に電気的に接続されている。

(もっと読む)

半導体装置とその製造方法

【課題】製造工程増加を抑制しつつ、閾値電圧の異なる複数のトランジスタ(FET)を同一基板上に有する半導体装置を実現する。

【解決手段】半導体装置は同一導電型の第1及び第2FETを有する。第1FETは、基板1上の第1ゲート電極13L、その側方の第1サイドウォール15L、第1ゲート電極13L両側の第1活性領域1Lの第1エクステンション領域17Lを備える。第2FETは、基板1上の第2ゲート電極13H、その側方の第2サイドウォール15H、第2ゲート電極13H両側の第2活性領域1Hの第2エクステンション領域17Hを備える。ゲート長方向に関し、第1エクステンション領域17Lと第1ゲート電極13Lとの重なりは、第2エクステンション領域17Hと第2ゲート電極13Hとの重なりよりも長い。第1ゲート電極13Lと第1サイドウォール15Lとの距離は、第2ゲート電極13Hと第2サイドウォール15Hとの距離より短い。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層を含むトランジスタと、酸化物半導体以外の半導体材料を用いて構成された論理回路と、を有し、前記トランジスタのソース電極またはドレイン電極の一方と、前記論理回路の少なくとも一の入力とは電気的に接続され、前記トランジスタを介して、前記論理回路に少なくとも一の入力信号が供給される半導体装置である。ここで、トランジスタのオフ電流は1×10−13A以下であるのが望ましい。

(もっと読む)

半導体装置

【課題】多層配線間で形成される寄生容量を低減することを目的の一とする。

【解決手段】絶縁表面上に第1配線と、前記第1配線を覆う第1層間絶縁膜と、前記第1層間絶縁膜上の一部に接して第2層間絶縁膜と、前記第1層間絶縁膜及び前記第2層間絶縁膜上に第2配線とを有し、前記第1配線と前記第2配線とが重なっている領域には、前記第1層間絶縁膜と前記第2層間絶縁膜とが積層された半導体装置である。第1配線と第2配線間に層間絶縁膜が積層されていることで寄生容量の低減が可能となる。

(もっと読む)

高耐圧MOSトランジスタおよび半導体集積回路装置、高耐圧半導体装置

【課題】半導体基板上に他のCMOS素子と集積して形成される高耐圧MOSトランジスタの、工程数を抑制しながら、ドレイン耐圧特性を向上させる。

【解決手段】半導体基板21と、ゲート電極23と、第2の導電型のソース領域21Sと、第2の導電型のドレイン領域21Dと、ソースエクステンション領域21aと、ドレインエクステンション領域21bと、を含み、ソースエクステンション領域21aとドレインエクステンション領域21bとの間にはチャネル領域が形成され、ソース領域21Sおよびソースエクステンション領域21aの下方には第1のウェル21PWが、第1の導電型で、素子分離領域21Iの下端部を超える深さで形成され、第1のウェル21PWの下方には第2のウェル21DNWが第2の導電型で形成され、第1のウェル21PWおよび第2のウェル21DNWは、ドレインエクステンション領域21b、ドレイン領域21Dの下には形成されない。

(もっと読む)

半導体装置

【課題】低酸素処理を施したシリコン基板は基板表面層が応力に対して非常にもろくなってしまい、ハンド津愛想うちの製造プロセスの過程でクラックや反りが発生する原因ともなってしまう。

【解決手段】チャネル形成領域に形成された不純物領域に応力を集中させるため、チャネル形成領域に対して人為的かつ局部的に不純物領域を設ける。チャネル形成領域に局部的に添加された不純物元素(炭素、窒素、酸素から選ばれた一種または複数種類の元素)の領域は、低酸素処理を施したシリコン基板の応力を緩和する緩衝領域として機能する。

(もっと読む)

半導体装置およびその作製方法

【課題】LSIやCPUやメモリに用いるトランジスタのリーク電流及び寄生容量を低減することを課題の一とする。

【解決手段】酸化物半導体中で電子供与体(ドナー)となる不純物を除去することで、真性又は実質的に真性な半導体であって、シリコン半導体よりもエネルギーギャップが大きい酸化物半導体でチャネル領域が形成される薄膜トランジスタを用い、LSIやCPUやメモリなどの半導体集積回路を作製する。水素濃度が十分に低減されて高純度化された酸化物半導体層を用いる薄膜トランジスタは、リーク電流による消費電力の少ない半導体装置を実現できる。

(もっと読む)

半導体装置、センスアンプ回路、半導体装置の制御方法及びセンスアンプ回路の制御方法

【課題】ダブルゲートトランジスタを用いた機能回路のバックゲート電圧を適切に制御して良好な特性を実現可能な半導体装置等及びその制御方法を提供する。

【解決手段】本発明の半導体装置は、ダブルゲートトランジスタを含む機能回路と、ダブルゲート構造の基準トランジスタ20、30を含む電圧制御回路を備えている。基準トランジスタ20、30には、第1ゲート電極に参照電圧Vrp、Vrnが印加され、第2ゲート電極の電位はドレイン電流Ip、Inが参照電流Irp、Irnと一致するように制御され、その電位が制御電圧VBGP、VBGNとして出力される。制御電圧VBGP、VBGNを機能回路のダブルゲートトランジスタの第2ゲート電極に印加することで機能回路に所望の特性が付与される。

(もっと読む)

半導体装置およびその製造方法

【課題】n型MISトランジスタを有する半導体装置の特性ばらつきを低減させる。

【解決手段】シリコン基板1上のメモリ領域RMに形成された、n型導電型である第1トランジスタQ1は、ホウ素を含むメモリ用チャネル領域CH1と、メモリ用ゲート電極GE1の両側壁側下に形成された、n型のメモリ用エクステンション領域ET1および酸素を含む拡散防止領域PA1とを有している。ここで、拡散防止領域PA1はメモリ用エクステンション領域ET1を内包するようにして形成されている。また、拡散防止領域PA1は、少なくともその一部が、メモリ用エクステンション領域ET1とメモリ用チャネル領域CH1との間に配置されている。

(もっと読む)

半導体装置

【課題】占有面積の大きな増加なく、十分なESD保護機能を持たせたシャロートレンチ分離構造を有するESD保護用のN型のMOSトランジスタを有する半導体装置を提供する。

【解決手段】素子分離にシャロートレンチ構造を有するESD保護用のN型MOSトランジスタを有する半導体装置において、ESD保護用のN型MOSトランジスタのドレイン領域上には、薄い絶縁膜を介して前記外部接続端子からの信号を受ける電極が形成されている半導体装置とする。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

【課題】

電子デバイスにおける電力消費を低減するシステム及び方法が開示される。この構造及び方法は、大部分が、バルクCMOSのプロセスフロー及び製造技術を再利用することによって実現され得る。この構造及び方法は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することを可能にするとともに、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有し、それにより、電力制御の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

41 - 60 / 272

[ Back to top ]