Fターム[5F048BD02]の内容

MOSIC、バイポーラ・MOSIC (97,815) | チャネル (4,415) | 形状 (1,258) | チャネル長(幅) (272)

Fターム[5F048BD02]に分類される特許

21 - 40 / 272

半導体装置の製造方法

【課題】第1MISFETのゲート電極と第2MISFETのゲート電極とを別工程で形成する半導体装置の製造技術において、第1MISFETと第2MISFETの信頼性向上を図ることができる技術を提供する。

【解決手段】半導体基板20上にゲート絶縁膜26、電荷蓄積膜27、絶縁膜28、ポリシリコン膜29、酸化シリコン膜30、窒化シリコン膜31およびキャップ絶縁膜32からなる積層膜を形成する。そして、フォトリソグラフィ技術およびエッチング技術を使用して、低耐圧MISFET形成領域および高耐圧MISFET形成領域に形成されている積層膜を除去する。その後、半導体基板20上にゲート絶縁膜34、36、ポリシリコン膜37およびキャップ絶縁膜38を形成する。そして、低耐圧MISFET形成領域および高耐圧MISFET形成領域にゲート電極を形成した後、メモリセル形成領域にゲート電極を形成する。

(もっと読む)

半導体装置

【課題】安定したボディ固定動作と共に、高集積化、低寄生容量化や配線容量の低減化を図ることができる、SOI基板上に形成される半導体装置を得る。

【解決手段】ソース領域1,ドレイン領域2及びゲート電極3で形成されるMOSトランジスタにおいて、ゲート一端領域及びゲート他端領域に部分分離領域11a及び11bが形成され、部分分離領域11aに隣接してタップ領域21aが形成され、部分分離領域11bに隣接してタップ領域21bが形成される。部分分離領域11a,11b、タップ領域21a,21b及び活性領域1,2の周辺領域は全て完全分離領域10が形成される。

(もっと読む)

埋め込みガードリング及び耐放射線性分離構造並びにその製造方法

【課題】大量の商業マイクロエレクトロニクスメーカーがアクセスし易い最先端の基礎設備を使用して、高性能且つ費用対効果に優れた耐放射線性集積回路(RHICs)を提供する。

【解決手段】様々な形式の放射線エネルギーによって引き起こされる有害な影響を減少し、又は排除するために、従来の設計及びプロセスを使用する一方で特殊構造を含んで半導体デバイスを作成する。このような半導体デバイスは本願で開示された1台以上の寄生的な分離デバイス、及び/又は、埋め込みガードリング構造を含む。これら新規な構造に対応する設計、及び/又は、工程ステップの導入には、従来のCMOS製作工程との互換性がある。したがって、比較的低い費用で比較的簡単に実施することができる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を形成する。

【解決手段】薄膜領域TA1中に第1の素子領域、第2の素子領域および第1の分離領域を有し、厚膜領域TA2中に第3の素子領域、第4の素子領域および第2の分離領域を有する半導体装置を次のように製造する。(a)絶縁層1bを介してシリコン層1cが形成された基板を準備する工程と、(b)基板の第1の分離領域および第2の分離領域のシリコン層中に素子分離絶縁膜3を形成する工程と、を有するよう製造する。さらに、(c)薄膜領域TA1にハードマスクを形成する工程と、(d)ハードマスクから露出した、第3の素子領域および第4の素子領域のシリコン層上に、それぞれシリコン膜7を形成する工程と、(e)第3の素子領域および第4の素子領域のシリコン膜7間に、素子分離絶縁膜11を形成する工程と、を有するよう製造する。

(もっと読む)

薄膜半導体装置

【課題】工程を複雑にすることなく、多結晶シリコン膜に回路特性に適した複数の異なる

ゲート絶縁膜厚を有する薄膜トランジスタ(TFT)を同一基板に形成することができる

薄膜半導体装置とその製造方法を提供。

【解決手段】ガラス基板上に形成した多結晶シリコン膜に駆動電圧が異なるTFTを混載

する際に、低電圧駆動TFTではチャネル領域の不純物をアクセプタがより多くなるよう

にしあるいはドナーがより少なくなるようにし、高電圧駆動TFTではチャネル領域の不

純物をドナーがより多くなるようにしあるいはアクセプタがより少なくなるようにする。

(もっと読む)

半導体装置

【課題】半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】半導体装置は、半導体基板に設けられた第1のトランジスタと、第1のトランジスタ上に設けられた第2のトランジスタとを有する。また、第2のトランジスタの半導体層は、半導体層の上側で配線と接し、下側で第1のトランジスタのゲート電極と接する。このような構造とすることにより、配線及び第1のトランジスタのゲート電極を、第2のトランジスタのソース電極及びドレイン電極として機能させることができる。これにより、半導体装置の占有面積を低減することができる。

(もっと読む)

半導体装置

【課題】本発明は、曲面を有する基材に被剥離層を貼りつけた半導体装置およびその作製

方法を提供することを課題とする。特に、曲面を有するディスプレイ、具体的には曲面を

有する基材に貼りつけられたOLEDを有する発光装置、曲面を有する基材に貼りつけら

れた液晶表示装置の提供を課題とする。

【解決手段】本発明は、基板上に素子を含む被剥離層を形成する際、素子のチャネルとし

て機能する領域のチャネル長方向を全て同一方向に配置し、該チャネル長方向と同一方向

に走査するレーザー光の照射を行い、素子を完成させた後、さらに、前記チャネル長方向

と異なっている方向、即ちチャネル幅方向に湾曲した曲面を有する基材に貼り付けて曲面

を有するディスプレイを実現するものである。

(もっと読む)

半導体装置及びその製造方法

【課題】電子及び正孔の移動度を向上させたSOI構造のCMOSの提供

【解決手段】Si基板1上にシリコン窒化膜2及びシリコン酸化膜3を介して、歪みSi層6を挟み、左右にSiGe層5を有する構造からなる第1のエピタキシャル半導体層及び歪みGe層8を挟み、左右にSiGe層7を有する構造からなる第2のエピタキシャル半導体層が島状に絶縁分離されて設けられ、歪みSi層6には概略チャネル領域が形成され、SiGe層5には概略高濃度及び低濃度のソースドレイン領域(10、11、12,13)が形成された包囲型ゲート電極構造のNチャネルのMISFETと、歪みGe層8には概略チャネル領域が形成され、SiGe層7には概略高濃度のソースドレイン領域(14、15)が形成された包囲型ゲート電極構造のPチャネルのMISFETとから構成したCMOS。

(もっと読む)

半導体装置

【課題】本願発明で開示する発明は、従来と比較して、さらに結晶成長に要する熱処理時間を短縮してプロセス簡略化を図る。

【解決手段】

一つの活性層204を挟んで二つの触媒元素導入領域201、202を配置して結晶化を行い、触媒元素導入領域201からの結晶成長と、触媒元素導入領域202からの結晶成長とがぶつかる境界部205をソース領域またはドレイン領域となる領域204bに形成する。

(もっと読む)

半導体装置およびそれを用いた無線通信機器

【課題】半導体装置の熱抵抗を低減すること、および小型化できる技術を提供する。

【解決手段】複数の単位トランジスタQを有する半導体装置であって、半導体装置は、単位トランジスタQを第1の個数(7個)有するトランジスタ形成領域3a、3b、3e、3fと、単位トランジスタQを第2の個数(4個)有するトランジスタ形成領域3c、3dとを有し、トランジスタ形成領域3c、3dは、トランジスタ形成領域3a、3b、3e、3fの間に配置され、第1の個数は、第2の個数よりも多い。そして、単位トランジスタは、コレクタ層と、ベース層と、エミッタ層とを備えており、エミッタ層上には、エミッタ層と電気的に接続されたエミッタメサ層が形成され、このエミッタメサ層上に、エミッタ層と電気的に接続されたバラスト抵抗層が形成されている。

(もっと読む)

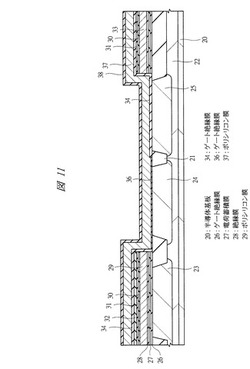

半導体装置の製造方法

【課題】フラッシュメモリセルと低電圧動作トランジスタや高電圧動作トランジスタを集積化し、異種トランジスタを混載する半導体装置の製造法を提供する。

【解決手段】半導体装置の製造方法は、(a)トンネル絶縁膜、Fゲート電極膜、電極間絶縁膜を堆積したFゲート電極構造を形成し(b)ゲート絶縁膜を形成し(c)導電膜、エッチストッパ膜を堆積し(d)エッチストッパ膜、導電膜をエッチングした積層ゲート電極構造を形成し(e)積層ゲート電極構造の側壁上に第1絶縁膜を形成し(f)積層ゲート電極側壁上に第1サイドウォールスペーサ層を形成し(g)エッチストッパ層を除去し(h)他の領域の導電層から、ゲート電極構造を形成し(i)積層ゲート電極構造、ゲート電極構造側壁上に第2サイドウォールスペーサを形成し(j)希弗酸水溶液で半導体基板表面を露出し(k)半導体基板表面にシリサイド層を形成する。

(もっと読む)

半導体装置および携帯電話機

【課題】アンテナスイッチのコスト削減を図る観点から、特に、アンテナスイッチをシリコン基板上に形成された電界効果トランジスタから構成する場合であっても、アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】RXスルートランジスタ群TH(RX)は、互いに直列に接続されたMISFETQ1〜Q5において、それぞれのMISFETのボディ領域と、隣接するMISFETのソース領域あるいはドレイン領域とを、それぞれ、ダイオード(整流素子)を介して接続する。そして、特に、nチャネル型MISFETの場合、MISFETのボディ領域から隣接するMISFETのソース領域あるいはドレイン領域へ向う向きが順方向となるようにダイオードを接続する。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】集積回路のコア部のロジックトランジスタ(MOSFET、MISFET)は、世代が進むごとに動作電圧をスケーリングすることで微細化が可能である。しかし、高耐圧部のトランジスタ(MOSFET、MISFET)は比較的高い電源電圧で動作するために縮小化が困難であり、同様に電源セル内の静電気放電(ESD)保護回路は、静電気(外来サージ)から半導体集積回路内の素子を保護するために耐圧が高いことが必須であり、電荷を逃がすために大面積である必要がある。従って、集積回路の微細化のためには、微細化が可能なトランジスタ構造が必須である。

【解決手段】本願発明は、ソース側にのみハロー領域を有するソースドレイン非対称構造の一対のMISFETから構成されたCMISインバータをESD保護回路部に有する半導体集積回路装置である。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】LSI中の高耐圧MOSFETを含む高耐圧回路は、純粋な内部回路と異なり、外部との関係で動作電圧が高い状態で固定されているため、通常のように、低電圧化による微細化が適用できない。このため、内部回路部の低電圧化に伴って、ますます、チップ内の占有面積を肥大化させる結果となっている。この問題について、本願発明者等が、各種の対策について評価したところによると、CMOSFET回路構成およびデバイス構成との適合性等の問題がネックとなっていることが明らかとなった。

【解決手段】本願発明は、各チャネル表面に波状起伏が設けられたNチャネル型およびPチャネル型MISFETを有する半導体集積回路装置において、Pチャネル型MISFETのチャネル表面に設けられた波状起伏に比べて、Nチャネル型MISFETのチャネル表面に設けられた波状起伏のピッチを狭くしたものである。

(もっと読む)

オフセット構造の薄膜トランジスタ

【課題】オフセット構造の薄膜トランジスタを提供する。

【解決手段】ゲート電極と、それぞれゲート電極と一部重畳する第1活性領域及び第2活性領域を備える活性層と、ゲート電極と活性層との間のゲート絶縁膜と、第1活性領域とそれぞれ電気的に連結された第1ソース/ドレイン電極及び第2ソース/ドレイン電極、第2活性領域とそれぞれ電気的に連結された第3ソース/ドレイン電極及び第4ソース/ドレイン電極を備えるソース/ドレイン電極層と、を備えるが、第1ソース/ドレイン電極ないし第4ソース/ドレイン電極のいずれか二つは、ゲート電極と一部重畳し、他の二つは、ゲート電極とオフセットされており、ソース/ドレイン電極の配置は、ソース/ドレイン電極層の中心に対称である薄膜トランジスタである。

(もっと読む)

半導体装置の設計方法

【課題】半導体装置を構成する回路ブロックにおけるトランジスタの信頼性劣化を考慮した半導体装置の設計方法を提供する。

【解決手段】経時劣化計算部11は、複数のトランジスタで構成される回路のネットリスト(回路記述ファイル101)、設計情報102を用いて、複数のトランジスタのうちの1つのトランジスタの回路定数を変化させて劣化後の回路動作特性(第1の特性)を算出する。解析部12は、第1の特性に変曲点があるかどうかを判定し、ある場合、変曲点に相当する回路定数を修正後の定数と決定する。変曲点がない場合、経時劣化計算部11は、更に劣化前の回路動作特性(第2の特性)を算出し、解析部12は、第1及び第2の特性に基づき、修正後の定数を決定する。解析部12は、ネットリストのうちの1つのトランジスタの回路定数を修正後の定数へ修正し、修正回路記述ファイル103を生成する。

(もっと読む)

半導体装置

【課題】アンテナスイッチのコスト削減を図る観点から、特に、アンテナスイッチをシリコン基板上に形成された電界効果トランジスタから構成する場合であっても、アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】TXシャントトランジスタSH(TX)を構成するMISFETQN1〜MISFETQN5において、GND端子に近い側に接続されたMISFETQN5から送信端子TXに近い側に接続されたMISFETQN1になるに連れて、ゲート幅Wgが大きくなるように構成されている。

(もっと読む)

半導体装置

【課題】MISFETにおけるAvt(Vtばらつき)のゲート幅依存性を考慮し、Vtミスマッチ及びVtばらつきを低減できるようにする。

【解決手段】半導体装置は、それぞれが半導体基板に形成され、ソースドレインを構成する拡散層205及び該拡散層205の上に形成されたゲート203を有し、且つ互いに並列接続された複数の単位MISFETから構成される複数のMISFET201、202を含む。MISFET201、202同士の間の閾値電圧のばらつきの標準偏差は、各MISFETにおける単位MISFETのそれぞれのゲート長とゲート幅との積の総和であるチャネル面積と同一の面積を有する単一のMISFET同士の間の閾値電圧のばらつきの標準偏差よりも小さい。

(もっと読む)

デカップリング回路及び半導体集積回路

【課題】容量値の切り換えが可能なデカップリング回路を提供すること。

【解決手段】本発明は、インバータ21を有する。インバータ21は、ゲート電極G1を有するi(iは1以上の整数)個のPMOSトランジスタ及びゲート電極G2を有するj(jは0以上の整数)個のPMOSトランジスタを有する。また、インバータ21は、ゲート電極G3を有するm(mは1以上の整数)個のNMOSトランジスタ及びゲート電極G2を有するn(nは0以上の整数)個のNMOSトランジスタを有する。ゲート電極G1〜G4は、インバータ21の入力端と接続される。ゲート電極G1及びG2の合計面積は、ゲート電極G3及びG4の合計面積と異なる。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。さらに、これらの微細化を達成した半導体装置の良好な特性を維持しつつ、3次元高集積化を図ることを目的の一つとする。

【解決手段】絶縁層中に埋め込まれた配線と、絶縁層上の酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極及びドレイン電極と、酸化物半導体層と重畳して設けられたゲート電極と、酸化物半導体層と、ゲート電極との間に設けられたゲート絶縁層と、を有し、絶縁層は、配線の上面の一部を露出するように形成され、配線は、その上面の一部が絶縁層の表面の一部より高い位置に存在し、且つ、絶縁層から露出した領域において、ソース電極またはドレイン電極と電気的に接続し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根粗さが1nm以下である半導体装置である。

(もっと読む)

21 - 40 / 272

[ Back to top ]